Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих процессоров цифровой обработки сигналов и в арифметических устройствах быстродействующих цифровых и комбинированных вычислительных машин.

Цель изобретения - увеличение быстродействия устройства.JQ

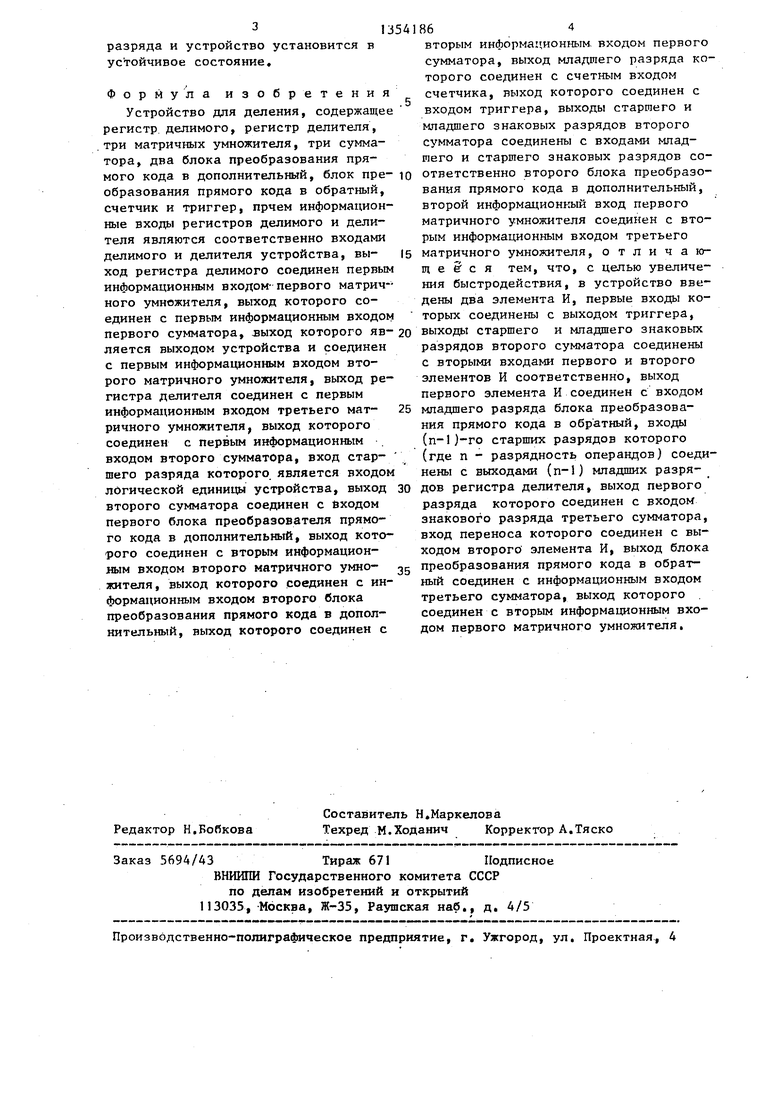

На чертеже показана функциональная схема устройства.

Устройство для деления содержит регистр 1 делимого, регистр 2 делителя, три матричных умножителя 3-5, три сумматора 6-8, блоки 9--1Q преобразования прямого кода в дополнительный, блок 11 преобразования прямого кода в обратный, входы 1 . и 13 делителя и делимого, счетчик 14, триггер 15, два элементы И 16 и. 17, вход 18 логической единицы.

Устройство работает следующим образом.

Одновременно на регистры 1 и 2 подают делимое и делитель в виде п- разрядных двоичных кодов, соответст- вуюпщх двоичным числам в нормализованной форме с запятой перед старшим разрядом, В исходном состоянии счетчик и триггер установлены в нуль.

При поступлении потешщапьных сигналов на входы матричных умножителей 3 и 5 на выходах появляются потенциальные сигналы, соответствующие произв едениям Ъ- Ц|(а) и atf(a) в виде {п+2)-раз- рядного двоичного кода Ъ Cf (а)

,.-.,, и а (р (а)

20

7.

мое,

о

9 УП+(

n-4-f

где Ъ - делиа - делитель, Ц (а) 1, а а« - код на выходе сумматора 8,

2

альные сигналы (а) - у , у, у ... ... У„,, и (О, 7., 7.:.. г„, )V 1 -(О, 7., 7,... 7.„, .

в результате появления потенциальных сигналов на входах сумматора 6 и матричного умножителя 4 возникает непрерывный переходный процесс, который может быть описан формулой

.ц (а) - 1 х + bcf (а) где Ъ - делимое; а - делитель; X - частное,

а индексы при х указывают номер ите- рации. Выходные сигналы, поступающие с (п+2)-х выходов матричного умножителя 4, поступают на вход блока 10 и в зависимости от значений (j, ,С5„ двух старших разрядов сумматора 7 могут появляться на выходе блока 10, то ли в прямом коде, если О., О, а о то ли в дополнительном, если 0-, 1 , а(з„ 0.

После нескольких итераций переход- ньй процесс завершается и устройство приходит в устойчивое состояние, при этом на выходе устройства устанавли- вается код, соответствующий коду частного от деления входных чисел. Соединение выхода младшего разряда сумматора 6 с входом счетчика 14 . обеспечивает счет числа импульсов на его входе, возникающих вследствие переходных процессов в устройстве.

Если же итерационный процесс не завершается, а происходит зацикливание, то происходит переполнение счетчика и появившийся в результате выходной сигнал с выхода счетчика 14 поступает на вход триггера 15.

25

30

35

40

....-- В сумматоре 7 происходит суммирование Выходной сигнал триггера 15, по- поступившего кода с сигналом логичес- ступая на первые входы элементов 16 кой единицы. На выходе сумматора 7 об- и 17, разрешает прохождение потенциа- разуется результат суммирования в ви- 45 °s ° одного из выходов двух старших де 1+7.0,7,, 7,,,...,7.„. С5,„С„, Z, Z, разрядов С5., или GQ , сумматора 7.

о 9 ч

nfi

7 + l -it - o

В зависимости от значений

разрядов G-, и Gg информационные сигналы О, z,7.2,...,z.,

появятся на выПри комбинации сигналов СТ., , G равной 10 появляется, сигнал на выходе элемента И 16, который постуходах блока 9 в виде прямого кода или 50 пает на вход младшего (п-го) разряда дополнительного по отношению к вход- блока 11, В результате происходит ному. Если С., 1, aGg О,, то на выходе блока 9 сигнал;Ы (соответствует прямому коду О, 7м22 .. 5 а если G., 0,Gp 1, то в блоке 9 входной код преобразован в дополнительный -(0, 7,,7.,,.. z, ).

уменьшение кода значения Ч(а) на величину младшего разряда. При комбинации сигналов G., Gj, , равной 0,1, 55 появляется сигнал на выходе элемента И 17, который поступает на вход переноса в младший разряд сумматора 8, В

результате происходит увеличение кода значения Cf (а) на величину младшего

На выходах матричного умножителя 3 и блока 9 устанавливаются потенци

0

альные сигналы (а) - у , у, у ... ... У„,, и (О, 7., 7.:.. г„, )V 1 -(О, 7., 7,... 7.„, .

в результате появления потенциальных сигналов на входах сумматора 6 и матричного умножителя 4 возникает непрерывный переходный процесс, который может быть описан формулой

.ц (а) - 1 х + bcf (а), где Ъ - делимое; а - делитель; X - частное,

а индексы при х указывают номер ите- рации. Выходные сигналы, поступающие с (п+2)-х выходов матричного умножителя 4, поступают на вход блока 10 и в зависимости от значений (j, ,С5„ двух старших разрядов сумматора 7 могут появляться на выходе блока 10, то ли в прямом коде, если О., О, а о то ли в дополнительном, если 0-, 1 , а(з„ 0.

После нескольких итераций переход- ньй процесс завершается и устройство приходит в устойчивое состояние, при этом на выходе устройства устанавли- вается код, соответствующий коду частного от деления входных чисел. Соединение выхода младшего разряда сумматора 6 с входом счетчика 14 . обеспечивает счет числа импульсов на его входе, возникающих вследствие переходных процессов в устройстве.

Если же итерационный процесс не завершается, а происходит зацикливание, то происходит переполнение счетчика и появившийся в результате выходной сигнал с выхода счетчика 14 поступает на вход триггера 15.

5

0

5

0

При комбинации сигналов СТ., , G равной 10 появляется, сигнал на выходе элемента И 16, который поступает на вход младшего (п-го) разряда блока 11, В результате происходит

уменьшение кода значения Ч(а) на величину младшего разряда. При комбинации сигналов G., Gj, , равной 0,1, появляется сигнал на выходе элемента И 17, который поступает на вход переноса в младший разряд сумматора 8, В

При комбинации сигналов СТ., , G авной 10 появляется, сигнал на выоде элемента И 16, который поступает на вход младшего (п-го) разряда блока 11, В результате происходит

результате происходит увеличение кода значения Cf (а) на величину младшего

разряда и устройство установится устойчивое состояние.

Формула изобретения Устройство для деления, содержаще регистр, делимого, регистр делителя, .три матричных умножителя, три сумматора, два блока преобразования прямого кода в дополнительный, блок пре- образования прямого кода в обратный, счетчик и триггер, прчем информационные входы регистров делимого и делителя являются соответственно входами делимого и делителя устройства, вы- ход регистра делимого соединен первым информационным входом- первого матричного умножителя, выход которого соединен с первым информационным входом первого сумматора, -выход которого яв- ляется выходом устройства и соединен с первым информационным входом второго матричного умножителя, выход регистра делителя соединен с первым информационным входом третьего мат- ричного умножителя, выход которого соединен с первым информационным входом второго сумматора, вход стар- шего разряда которого является входом логической единицы устройства, выход второго сумматора соединен с входом первого блока преобразователя прямого кода в дополнительный, выход которого соединен с вторым информационным входом второго матричного умно- жителя, выход которого соединен с информационным входом второго блока преобразования прямого кода в дополнительный, выход которого соединен с

Редактор Н.Бобкова Заказ 5694/43

Составитель Н.Маркепова

Техред М.Ходанич Корректор А.Тяско

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ю|5 20 2530 355541864

вторым информационным, входом первого сумматора, выход младшего разряда которого соединен с счетным входом счетчика, выход которого соединен с входом триггера, выходы старшего и младшего знаковых разрядов второго сумматора соединены с входами младшего и старшего знаковых разрядов соответственно второго блока преобразования прямого кода в дополнительный, второй информационный вход первого матричного умножителя соединен с вторым информационным входом третьего матричного умножителя, отличающейся тем, что, с цепью увеличения быстродействия, в устройство введены два элемента И, первые входы которых соединены с выходом триггера, выходы старшего и младшего знаковых разрядов второго сумматора соединены с вторыми входами первого и второго элементов И соответственно, выход первого элемента И соединен с входом мпадшего разряда блока преобразования прямого кода в обратный, входы (п-1)-го старших разрядов которого (где п - разрядность операндов) соединены с выходами (п-1) младших разрядов регистра делителя, выход первого разряда которого соединен с входом знакового разряда третьего сумматора, вход переноса которого соединен с выходом второго элемента И, выход блока преобразования прямого кода в обратный соединен с информационным входом третьего сумматора, выход которого . соединен с вторым информационным входом первого матричного умножителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1517026A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления | 1986 |

|

SU1325467A1 |

| Устройство для деления | 1989 |

|

SU1619256A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении быстродействующих процессов цифровой обра- ботки сигналов и в арифметических устройствах быстродействующих цифро- вых и комбинированных вычислительных машин о Целью изобретения является увеличение быстродействия устройства для деления, содержащего регистры 1 и 2 Делимого и делителя, три матричных умножителя 3-5, три сумматора 6-8, два блока преобразования прямого кода в дополйительный 9 и 10, блок 11 преобразования прямого кода в обратный, счетчик 14 и триггер 15, Для достижения цели в устройство дополнительно введены два элемента И 16 и 17. 1 илв f3

| Устройство для деления | 1981 |

|

SU987621A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1985 |

|

SU1317432A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-11-23—Публикация

1986-01-03—Подача