Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах ввода-вывода информации автоматизированных систем научного исследования сварочного процесса.

Цель изобретения - повышение информативности преобразователя за счет временного уплотнения последовательного кода.

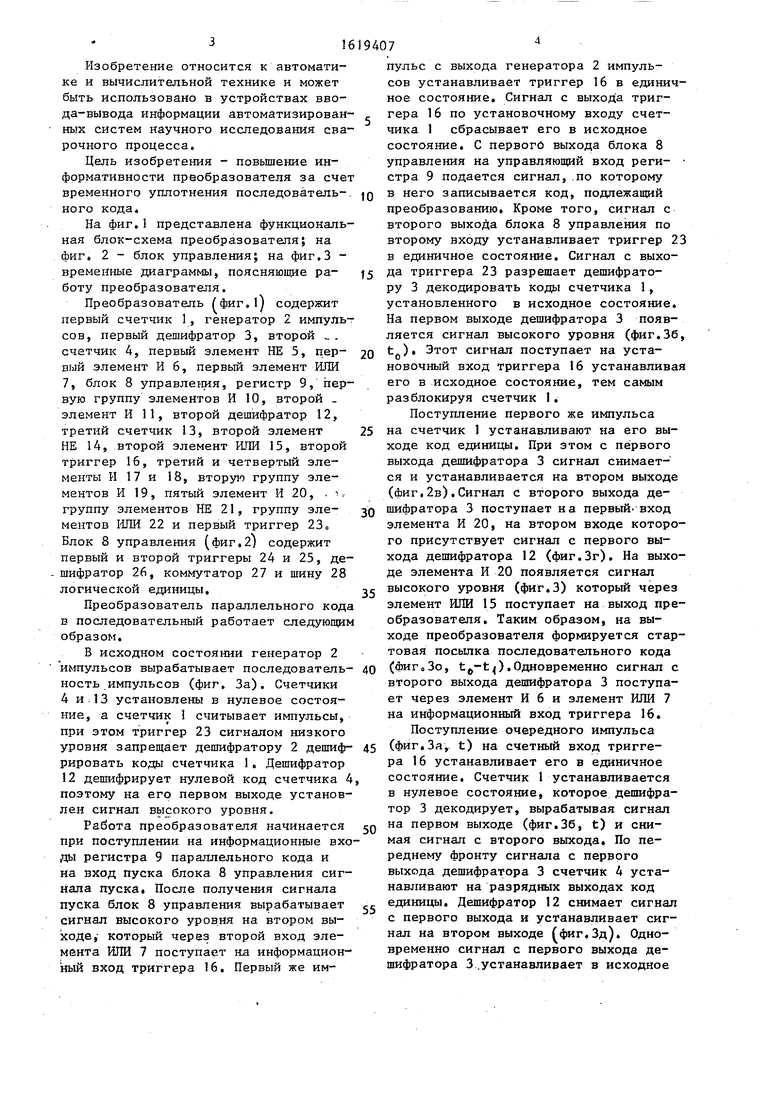

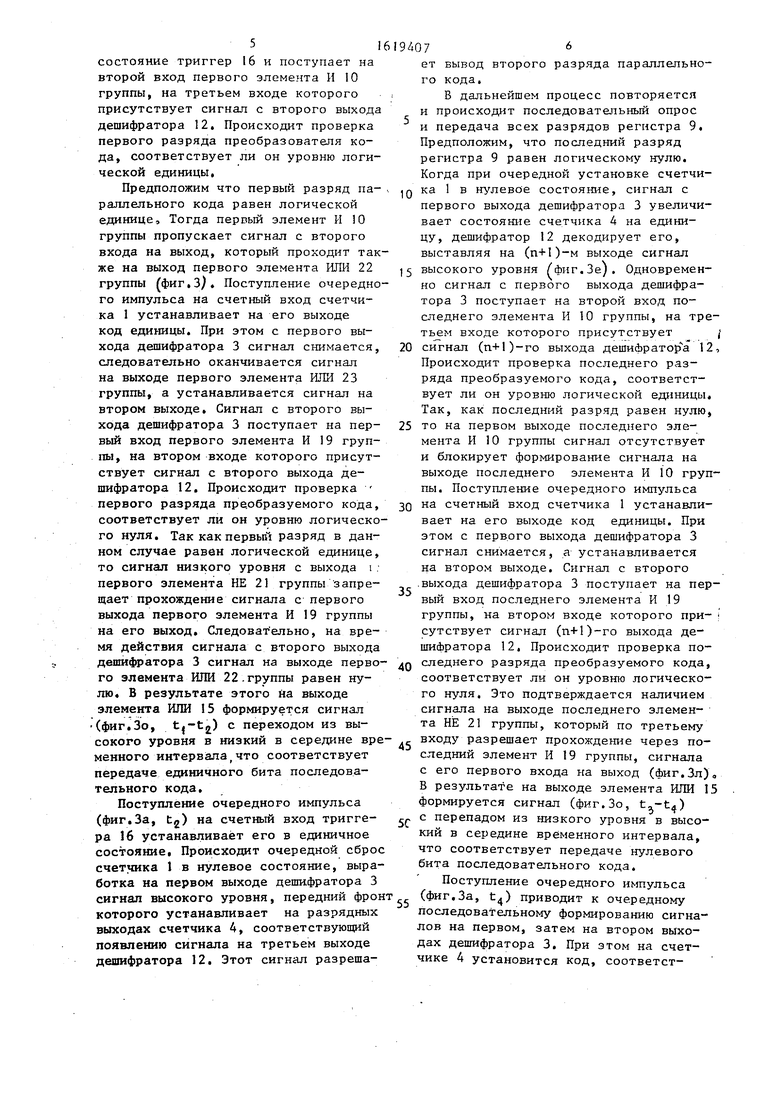

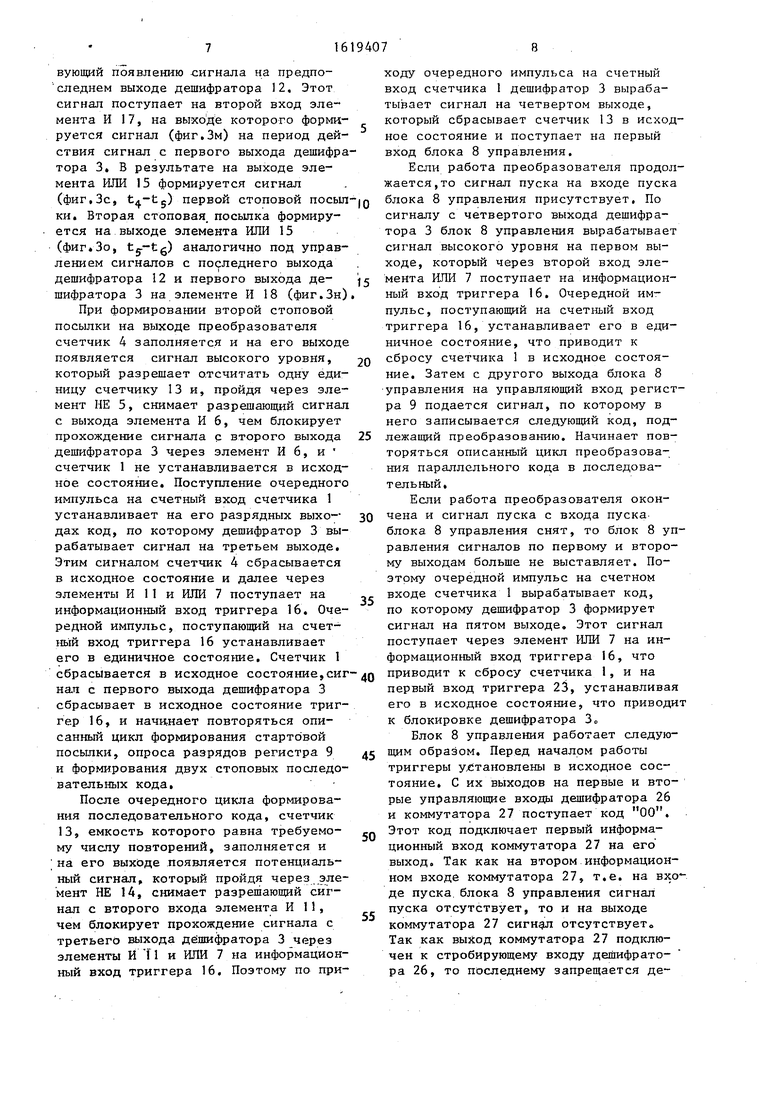

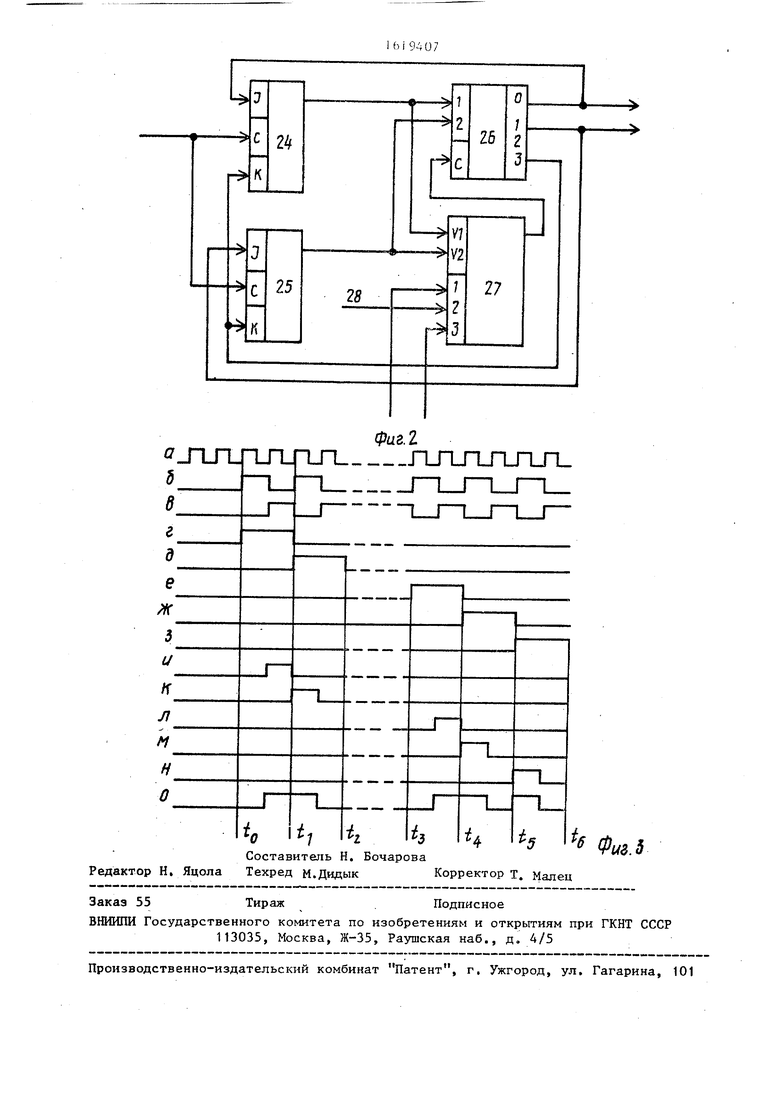

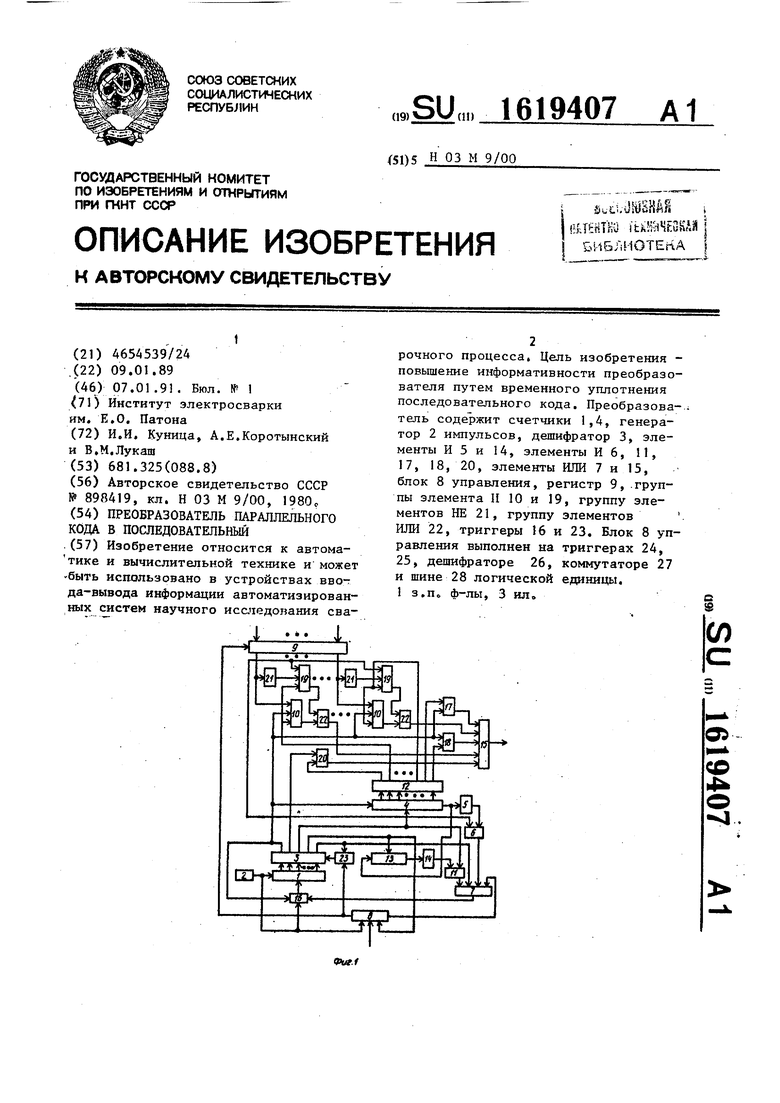

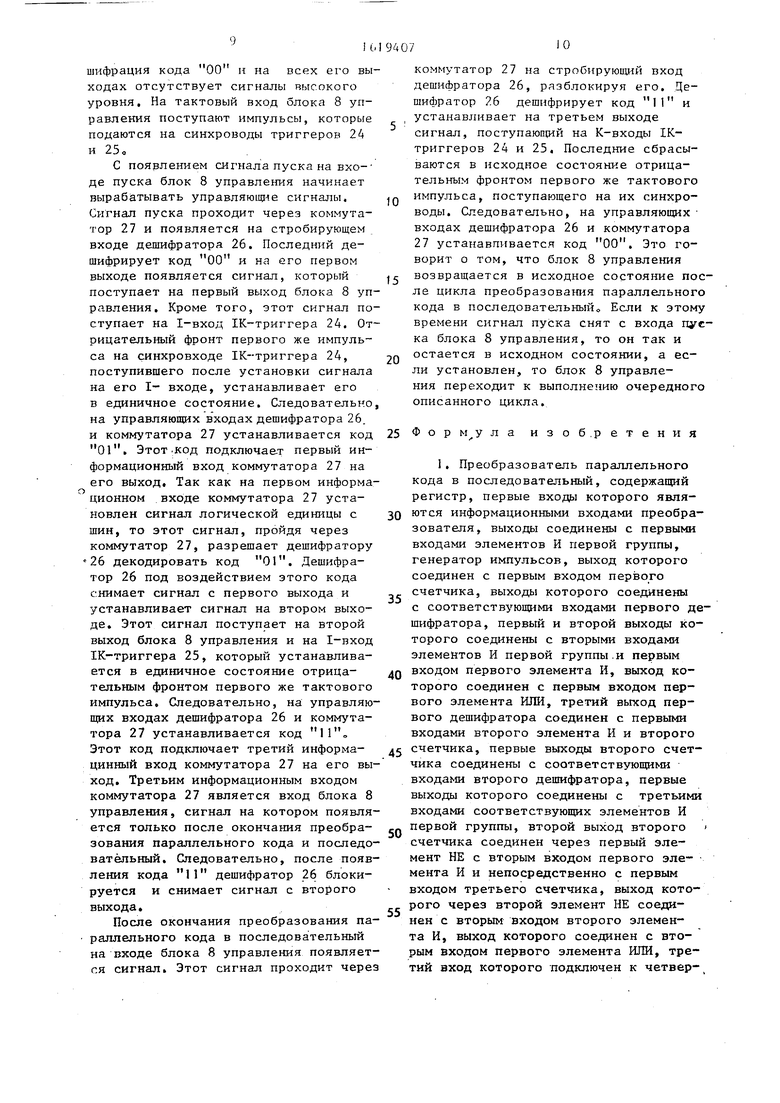

На фиг.1 представлена функциональная блок-схема преобразователя; на Лиг. 2 - блок управления; на фиг.З - временные диаграммы, поясняющие работу преобразователя.

Преобразователь (фиг.1) содержит

первый счетчик 1, генератор 2 импульсов, первый дешифратор 3, второй . счетчик 4, первый элемент НЕ 5, пер- 20 вый элемент И 6, первый элемент ИЛИ 7, блок 8 управления, регистр 9, первую группу элементов И 10, второй элемент И 11, второй дешифратор 12, третий счетчик 13, второй элемент 25 НЕ 14, второй элемент ИЛИ 15, второй триггер 16, третий и четвертый элементы И 17 и 18, вторую группу элементов И 19, пятый элемент И 20, . группу элементов НЕ 21, группу эле- 30 ментов ИЛИ 22 и первый триггер 23 Блок 8 управления (фиг.2) содержит первый и второй триггеры 24 и 25, де- - шифратор 26, коммутатор 27 и шину 28 логической единицы.

Преобразователь параллельного кода в последовательный работает следующим образом.

В исходном состоянии генератор 2 импульсов вырабатывает последователь- 40 ность импульсов (фиг. За). Счетчики 4 и 13 установлены в нулевое состояние, а счетчик 1 считывает импульсы, при этом триггер 23 сигналом низкого

16194074

пульс с выхода генератора 2 импульсов устанавливает триггер 16 в единичное состояние. Сигнал с выхода триггера 16 по установочному входу счетчика 1 сбрасывает его в исходное состояние. С первого выхода блока 8 управления на управляющий вход реги- стра 9 подается сигнал, по которому

JQ в него записывается код, подлежащий преобразованию. Кроме того, сигнал с второго выхоДа блока 8 управления по второму входу устанавливает триггер 23 в единичное состояние. Сигнал с выхоJ5 да триггера 23 разрешает дешифратору 3 декодировать коды счетчика 1, установленного в исходное состояние. На первом выходе дешифратора 3 появляется сигнал высокого уровня (фиг.36,

35

t ). Этот сигнал поступает на установочный вход триггера 16 устанавливая его в исходное состояние, тем самым разблокируя счетчик 1.

Поступление первого же импульса на счетчик 1 устанавливают на его выходе код единицы. При этом с первого выхода дешифратора 3 сигнал снимается и устанавливается на втором выходе (Лиг.2в).Сигнал с второго выхода дешифратора 3 поступает на первый- вход элемента И 20, на втором входе которого присутствует сигнал с первого выхода дешифратора 12 (фиг.Зг). На выходе элемента И 20 появляется сигнал высокого уровня (фиг.З) который через элемент ИЛИ 15 поступает на выход преобразователя. Таким образом, на выходе преобразователя формируется стартовая посылка последовательного кода (бигоЗо, te-tj).Одновременно сигнал с второго выхода дешифратора 3 поступает через элемент И 6 и элемент ИЛИ 7 на информационный вход триггера 16.

Поступление очередного импульса

уровня запрещает дешифратору 2 дешиф- 45 (Фиг.За t) на счетный вход триггерировать коды счетчика 1. Дешифратор 12 дешифрирует нулевой код счетчика 4 поэтому на его первом выходе установлен сигнал высокого уровня.

Работа преобразователя начинается при поступлении на информационные входы регистра 9 параллельного кода и на вход пуска блока 8 управления сигнала пуска. После получения сигнала пуска блок 8 управления вырабатывает сигнал высокого уровня на втором выходе, который через второй вход элемента ИЛИ 7 поступает нл информационный вход триггера 16. Первый же им

0

0

5

t ). Этот сигнал поступает на установочный вход триггера 16 устанавливая его в исходное состояние, тем самым разблокируя счетчик 1.

Поступление первого же импульса на счетчик 1 устанавливают на его выходе код единицы. При этом с первого выхода дешифратора 3 сигнал снимается и устанавливается на втором выходе (Лиг.2в).Сигнал с второго выхода дешифратора 3 поступает на первый- вход элемента И 20, на втором входе которого присутствует сигнал с первого выхода дешифратора 12 (фиг.Зг). На выходе элемента И 20 появляется сигнал высокого уровня (фиг.З) который через элемент ИЛИ 15 поступает на выход преобразователя. Таким образом, на выходе преобразователя формируется стартовая посылка последовательного кода (бигоЗо, te-tj).Одновременно сигнал с второго выхода дешифратора 3 поступает через элемент И 6 и элемент ИЛИ 7 на информационный вход триггера 16.

Поступление очередного импульса

Q

5

ра 16 устанавливает его в единичное состояние. Счетчик 1 устанавливается в нулевое состояние, которое дешифратор 3 декодирует, вырабатывая сигнал на первом выходе (фиг.36, t) и снимая сигнал с второго выхода. По переднему фронту сигнала с первого выхода дешифратора 3 счетчик 4 устанавливают на разрядных выходах код единицы. Дешифратор 12 снимает сигнал с первого выхода и устанавливает сигнал на втором выходе (фиг.Зд). Одновременно сигнал с первого выхода дешифратора 3 .устанавливает в исходное

5

состояние триггер 16 и поступает на второй вход первого элемента И 10 группы, на третьем входе которого присутствует сигнал с второго выхода дешифратора 12. Происходит проверка первого разряда преобразователя кода, соответствует ли он уровню логической единицы.

Предположим что первый разряд параллельного кода равен логической единице, Тогда первый элемент И 10 группы пропускает сигнал с второго входа на выход, который проходит также на выход первого элемента ИЛИ 22 группы (фиг.З). Поступление очередного импульса на счетный вход счетчика 1 устанавливает на его выходе код единицы. При этом с первого выхода дешифратора 3 сигнал снимается, следовательно оканчивается сигнал на выходе первого элемента ИЛИ 23 группы, а устанавливается сигнал на втором выходе. Сигнал с второго выхода дешифратора 3 поступает на первый вход первого элемента И 19 группы, на втором входе которого присутствует сигнал с второго выхода дешифратора 12. Происходит проверка первого разряда преобразуемого кода, соответствует ли он уровню логического нуля. Так как первый разряд в данном случае равен логической единице, то сигнал низкого уровня с выхода i первого элемента НЕ 21 группы запрещает прохождение сигнала с первого выхода первого элемента И 19 группы на его выход. Следовательно, на время действия сигнала с второго выхода дешифратора 3 сигнал на выходе первого элемента ИЛИ 22.группы равен нулю, В результате этого на выходе элемента ИЛИ 15 формируется сигнал (фиг.Зо, t|-t2) с переходом из вы1619407 ет

10

20

вывод второго разряда параллельного кода.

В дальнейшем процесс повторяется и происходит последовательный опрос и передача всех разрядов регистра 9. Предположим, что последний разряд регистра 9 равен логическому нулю. Когда при очередной установке счетчика 1 в нулевое состояние, сигнал с первого выхода дешифратора 3 увеличивает состояние счетчика 4 на единицу, дешифратор 12 декодирует его, выставляя на (п+1)-м выходе сигнал 15 высокого уровня /фиг.Зе). Одновременно сигнал с первого выхода дешифратора 3 поступает на второй вход последнего элемента И 10 группы, на третьем входе которого присутствует сигнал (п+1)-го выхода дешифратора 12 Происходит проверка последнего разряда преобразуемого кода, соответствует ли он уровню логической единицы. Так, как последний разряд равен нулю, то на первом выходе последнего элемента И 10 группы сигнал отсутствует и блокирует формирование сигнала на выходе последнего элемента И 10 группы. Поступление очередного импульса на счетный вход счетчика 1 устанавливает на его выходе код единицы. При этом с первого выхода дешифратора 3 сигнал снимается, а устанавливается на втором выходе. Сигнал с второго выхода дешифратора 3 поступает на первый вход последнего элемента И 19 группы, на втором входе которого при- сутствует сигнал (п+1)-го выхода дешифратора 12, Происходит проверка последнего разряда преобразуемого кода, соответствует ли он уровню логического нуля. Это подтверждается наличием сигнала на выходе последнего элемента НЕ 21 группы, который по третьему

25

30

35

40

сокого уровня в низкий в середине вре- -с входу разрешает прохождение через поменного интервала,что соответствует передаче единичного бита последовательного кода.

Поступление очередного импульса (фиг.За, t2) на счетный вход триггера 16 устанавливает его в единичное состояние. Происходит очередной сброс счетчика 1 в нулевое состояние, выработка на первом выходе дешифратора 3

5С

следний элемент И 19 группы, сигнала с его первого входа на выход (фиг.Зл), В результате на выходе элемента ИЛИ 15 формируется сигнал (фиг.Зо, t,-t4) с перепадом из низкого уровня в высокий в середине временного интервала, что соответствует передаче нулевого бита последовательного кода.

Поступление очередного импульса

сигнал высокого уровня, передний фронт (фиг,За, t4) приводит к очередному которого устанавливает на разрядных последовательному формированию сигна- выходах счетчика 4, соответствующий лов на первом, затем на втором выхо- появлению сигнала на третьем выходе дах дешифратора 3. При этом на счет- дешифратора 12. Этот сигнал разреша- чике 4 установится код, соответст19407 ет

10

20

вывод второго разряда параллельного кода.

В дальнейшем процесс повторяется и происходит последовательный опрос и передача всех разрядов регистра 9. Предположим, что последний разряд регистра 9 равен логическому нулю. Когда при очередной установке счетчика 1 в нулевое состояние, сигнал с первого выхода дешифратора 3 увеличивает состояние счетчика 4 на единицу, дешифратор 12 декодирует его, выставляя на (п+1)-м выходе сигнал 15 высокого уровня /фиг.Зе). Одновременно сигнал с первого выхода дешифратора 3 поступает на второй вход последнего элемента И 10 группы, на третьем входе которого присутствует / сигнал (п+1)-го выхода дешифратора 12, Происходит проверка последнего разряда преобразуемого кода, соответствует ли он уровню логической единицы. Так, как последний разряд равен нулю, то на первом выходе последнего элемента И 10 группы сигнал отсутствует и блокирует формирование сигнала на выходе последнего элемента И 10 группы. Поступление очередного импульса на счетный вход счетчика 1 устанавливает на его выходе код единицы. При этом с первого выхода дешифратора 3 сигнал снимается, а устанавливается на втором выходе. Сигнал с второго выхода дешифратора 3 поступает на первый вход последнего элемента И 19 группы, на втором входе которого при- сутствует сигнал (п+1)-го выхода дешифратора 12, Происходит проверка последнего разряда преобразуемого кода, соответствует ли он уровню логического нуля. Это подтверждается наличием сигнала на выходе последнего элемента НЕ 21 группы, который по третьему

25

30

35

40

следний элемент И 19 группы, сигнала с его первого входа на выход (фиг.Зл), В результате на выходе элемента ИЛИ 15 формируется сигнал (фиг.Зо, t,-t4) с перепадом из низкого уровня в высокий в середине временного интервала, что соответствует передаче нулевого бита последовательного кода.

вующий появлению сигнала на предпоследнем выходе дешифратора 12, Этот сигнал поступает на второй вход элемента И 17, на выходе которого формируется сигнал (фиг.Зм) на период действия сигнал с первого выхода дешифратора 3. В результате на выходе элемента ИЛИ 15 формируется сигнал (фиг,Зс, t4-ts) первой стоповой посылки. Вторая стоповая, посылка формируется на выходе элемента ИЛИ 15 (фиг.Зо, tj--tg) аналогично под управлением сигналов с последнего выхода дешифратора 12 и первого выхода дешифратора 3 на элементе И 18 (фиг.3н)

При формировании второй стоповой посылки на выходе преобразователя счетчик 4 заполняется и на его выходе появляется сигнал высокого уровня, который разрешает отсчитать одну единицу счетчику 13 и, пройдя через элемент НЕ 5, снимает разрешающий сигнал с выхода элемента И 6, чем блокирует прохождение сигнала с второго выхода дешифратора 3 через элемент И б, и счетчик 1 не устанавливается в исходное состояние. Поступление очередного импульса на счетный вход счетчика 1 устанавливает на его разрядных выходах код, по которому дешифратор 3 вырабатывает сигнал на третьем выходе. Этим сигналом счетчик 4 сбрасывается в исходное состояние и далее через элементы И 11 и ИЛИ 7 поступает на информационный вход триггера 16. Очередной импульс, поступающий на счетный вход триггера 16 устанавливает его в единичное состояние. Счетчик 1 сбрасывается в исходное состояние,сиг нап с первого выхода дешифратора 3 сбрасывает в исходное состояние триггер 16, и начинает повторяться описанный цикл формирования стартовой посылки, опроса разрядов регистра 9 и формирования двух стоповых последовательных кода.

После очередного цикла формирования последовательного кода, счетчик 13, емкость которого равна требуемому числу повторений, заполняется и на его выходе появляется потенциальный сигнал, который пройдя через элемент НЕ 14, снимает разрешающий сигнал с второго входа элемента И 11, чем блокирует прохождение сигнала с третьего выхода дешифратора 3 через элементы И Т1 и ИЛИ 7 на информационный вход триггера 16. Поэтому по при

5

0

5

5

0

5

0

0

5

ходу очередного импульса на счетный вход счетчика 1 дешифратор 3 вырабатывает сигнал на четвертом выходе, который сбрасывает счетчик 13 в исходное состояние и поступает на первый вход блока 8 управления.

Если работа преобразователя продолжается, то сигнал пуска на входе пуска блока 8 управления присутствует. По сигналу с четвертого выхода1 дешифратора 3 блок 8 управления вырабатывает сигнал высокого уровня на первом выходе, который через второй вход элемента ИЛИ 7 поступает на информационный вход триггера 16. Очередной импульс, поступающий на счетный вход триггера 16, устанавливает его в единичное состояние, что приводит к сбросу счетчика 1 в исходное состояние. Затем с другого выхода блока 8 управления на управляющий вход регистра 9 подается сигнал, по которому в него записывается следующий код, подлежащий преобразованию. Начинает повторяться описанный цикл преобразования параллельного кода в доследова- тельный.

Если работа преобразователя окончена и сигнал пуска с входа пуска блока 8 управления снят, то блок 8 управления сигналов по первому и второму выходам больше не выставляет. Поэтому очередной импульс на счетном входе счетчика 1 вырабатывает код, по которому дешифратор 3 формирует сигнал на пятом выходе. Этот сигнал поступает через элемент ИЛИ 7 на информационный вход триггера 16, что приводит к сбросу счетчика 1, и на первый вход триггера 23, устанавливая его в исходное состояние, что приводит к блокировке дешифратора 3

Блок 8 управления работает следующим образом. Перед началом работы триггеры установлены в исходное состояние. С их выходов на первые и вторые управляющие входы дешифратора 26 и коммутатора 27 поступает код 00. Этот код подключает первый информационный вход коммутатора 27 на его выход. Так как на втором информационном входе коммутатора 27, т.е. на входе пуска блока 8 управления сигнал пуска отсутствует, то и на выходе коммутатора 27 сигнал отсутствуете Так как выход коммутатора 27 подключен к стробирующему входу дешифратора 26, то последнему запрещается деифрация кода 00 и на всех его выодах отсутствует сигналы высокого ровня. На тактовый вход блока 8 управления поступают импульсы, которые подаются на синхроводы триггеров 24 и 250

С появлением сигнала пуска на вхо- де пуска блок 8 управления начинает вырабатывать управляющие сигналы. Сигнал пуска проходит через коммутатор 27 и появляется на стробирующем входе дешифратора 26. Последний дешифрирует код 00 и на его первом выходе появляется сигнал, который поступает на первый выход блока 8 управления. Кроме того, этот сигнал поступает на 1-вход IK-триггера 24. Отрицательный фронт первого же импульса на синхровходе 1К--триггера 24, поступившего после установки сигнала на его I- входе, устанавливает его в единичное состояние. Следовательно, на управляющих входах дешифратора 26. и коммутатора 27 устанавливается код 01. Этот.код подключает первый информационный вход коммутатора 27 на его выход. Так как на первом информационном входе коммутатора 27 установлен сигнал логической единицы с шин, то этот сигнал, пройдя через коммутатор 27, разрешает дешифратору 26 декодировать код 01. Дешифратор 26 под воздействием этого кода снимает сигнал с первого выхода и устанавливает сигнал на втором выходе. Этот сигнал поступает на второй выход блока 8 управления и на 1-вход IK-триггера 25, который устанавливается в единичное состояние отрицательным фронтом первого же тактового импульса. Следовательно, на управляющих входах дешифратора 26 и коммутатора 27 устанавливается код Этот код подключает третий информа- цинный вход коммутатора 27 на его выход. Третьим информационным входом коммутатора 27 является вход блока 8 управления, сигнал на котором появляется только после окончания преобразования параллельного кода и последовательный. Следовательно, после появления кода 11 дешифратор 26 блокируется и снимает сигнал с второго выхода.

После окончания преобразования па- раплельного кода в последовательный на входе блока 8 управления появляется сигнал. Этот сигнал проходит через

коммутатор 27 на стробируюший вход дешифратора 26, разблокируя его. Це- шифратор 26 дешифрирует код 11 и устанавливает на третьем выходе сигнал, поступающий на К-входы IK- триггеров 24 и 25, Последние сбрасываются в исходное состояние отрицательным фронтом первого же тактового

импульса, поступающего на их синхроводы. Следовательно, на управляющих входах дешифратора 26 и коммутатора 27 устанавливается код 00. Это говорит о том, что блок 8 управления

возвращается в исходное состояние после цикла преобразования параллельного кода в последовательныйо Если к этому времени сигнал пуска снят с входа пуска блока 8 управления, то он так и

Q остается в исходном состоянии, а если установлен, то блок 8 управления переходит к выполнению очередного описанного цикла.

5 изобретен и я

1. Преобразователь параллельного кода в последовательный, содержащий регистр, первые входы которого явля0 ются информационными входами преобразователя, выходы соединены с первыми входами элементов И первой группы, генератор импульсов, выход которого соединен с первым входом первого счетчика, выходы которого соединены с соответствующими входами первого дешифратора, первый и второй выходы которого соединены с вторыми входами элементов И первой группы.и первым

Q входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, третий выход первого дешифратора соединен с первыми входами второго элемента И и второго

5 счетчика, первые выходы второго счетчика соединены с соответствующими входами второго дешифратора, первые выходы которого соединены с третьими входами соответствующих элементов И первой группы, второй выход второго

5

0

5

счетчика соединен через первый элемент НЕ с вторым входом первого эле- мента И и непосредственно с первым входом третьего счетчика, выход которого через второй элемент НЕ соединен с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого подключен к четвер-ч

тому выходу первого дешифратора, пятый выход первого дешифратора соединен с первым входом блока управления, второй вход которого является входом Пуск преобразователя, первый и второй выходы блока управления соединены соответственно с вторым входом регистра и четвертым входом первого

элемента ИЛИ, второй элемент ИЛИ, вы- JQ ход которого является выходом Преобразователя, отличающийся тем, что, с целью повышения информативности преобразователя, в него введены вторая группа элементов И, труп- |. па элементов НЕ, группа элементов ИЛИ, третий, четвертый и пятый элементы И и триггеры, первый и второй входы И выход первого триггера подключены соответственно к первому выхо- )Q ду блока управления, четвертому выходу и второму входу первого дешифратора, третий вход блока управления и первый вход второго регистра объединены и подключены к выходу генератора 25

импульсов, второй вход второго счетчика и первые входы третьего и четвертого элементов И подключены к первому выходу первого дешифратора, выход первого элемента ИЛИ соединен с тре- Чп тьим входом второго триггера, выход которого соединен с вторым входом первого счетчика, второй вход третьего счетчика подключен к пятому выходу первого дешифратора, первые входы элементов И второй группы и первый вход пятого, элемента И подключены к второму выходу первого дешифратора, входы элементов НЕ группы подключены к соответствующим выходам регистра,

35

40

выходы - к вторым входам соответст . 5

п

5

0

вующих элементов И второй группы, третьи входы которых подключены к соответствующим первым выходам второго дешифратора, выходы элементов И первой и второй групп соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ группы, выходы которых соединены с соответствующими первыми входами второго элемента ИЛИ, второй, третий и четвертый выходы второго дешифратора соединены с вторыми входами соответственно пятого, третьего и четвертого элементов И, выходы которых соединены соответственно с вторым, третьим и четвертым входами второго элемента ИЛИ.

2 Преобразователь по п. отличающийся тем, что блок управления содержит дешифраторы, коммутатор, триггер и шину логической единицы, выходы первого и второго триггеров соединены с одноименными управляющими входами дешифратора и коммутатора, выход которого соединен со стробирующим входом дешифратора, первый и второй выходы которого соединены с I-входами соответственно первого и второго триггеров и являются одноименными выходами блока управления, третий выход дешифратора соединен с К-входами триггеров, С-входы которых объединены и являются третьим входом блока управления, первый информационный вход коммутатора подключен к шине логической единицы, второй и третий информационные входы коммутатора являются соответственно вторым и первым входами блока управления.

ь в

г д

е

ж д и

/г л м н о

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1980 |

|

SU898419A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310818A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Устройство для последовательного программного управления | 1983 |

|

SU1126928A1 |

| Устройство для программного управления | 1989 |

|

SU1698875A1 |

| Устройство для сопряжения ЦВМ с линиями связи | 1986 |

|

SU1462328A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

Изобретение относится к автома- тике и вычислительной технике и может -быть использовано в устройствах ввода-вывода информации автоматизированных систем научного исследования сваi X рочного процесса. Цель изобретения - повышение информативности преобразователя путем временного уплотнения последовательного кода. Преобразователь содержит счетчики 1,4, генератор 2 импульсов, дешифратор 3, элементы И 5 и 14, элементы И 6, 11, 17, 18, 20, элементы ИЛИ 7 и 15, блок 8 управления, регистр 9, группы элемента II 10 и 19, группу элементов НЕ 21, группу элементов ИЛИ 22, триггеры 16 и 23. Блок 8 управления выполнен на триггерах 24, 25, дешифраторе 26, коммутаторе 27 и шине 28 логической единицы. 1 З.Пс, ф-ЛЫ, 3 ИЛ i / о QD -U

| Преобразователь параллельного кода в последовательный | 1980 |

|

SU898419A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-07—Публикация

1989-01-09—Подача