Ј

Ж

В

11

12

13

#

1о

№

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой перестраиваемый полосовой фильтр | 1982 |

|

SU1166274A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Цифровой фильтр | 1983 |

|

SU1145346A1 |

| Усреднитель-анализатор спектра Фурье | 1980 |

|

SU955086A1 |

| Устройство для вычисления коэффициентов интерполирующего полинома | 1990 |

|

SU1748158A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

Изобретение может быть использовано в системах цифровой обработки сигналов и позволяет повысить быстродействие и точность при многодиап.з- зонпой фильтрации. Устройство содержит цифровой фильтр 1, блок 7 формирования адресов, блок 11 памяти и блок 14 управления. Применение1 памяти результатов дает возможность вычислять отфильтрованное значение сигнала только с помощью операций сдки- га и сложения при уменьшении погрешностей, обусловленных ограниченной длиной представления коэфбнциентоп цифрового фильтра. 10 ил. 8 (Я

19

W

ДГ

,Ј СЛ

/4

Фиг.1

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов.

Цель изобретения - повышение быстродействия и точности устройства при многодиапазонной фильтрации.

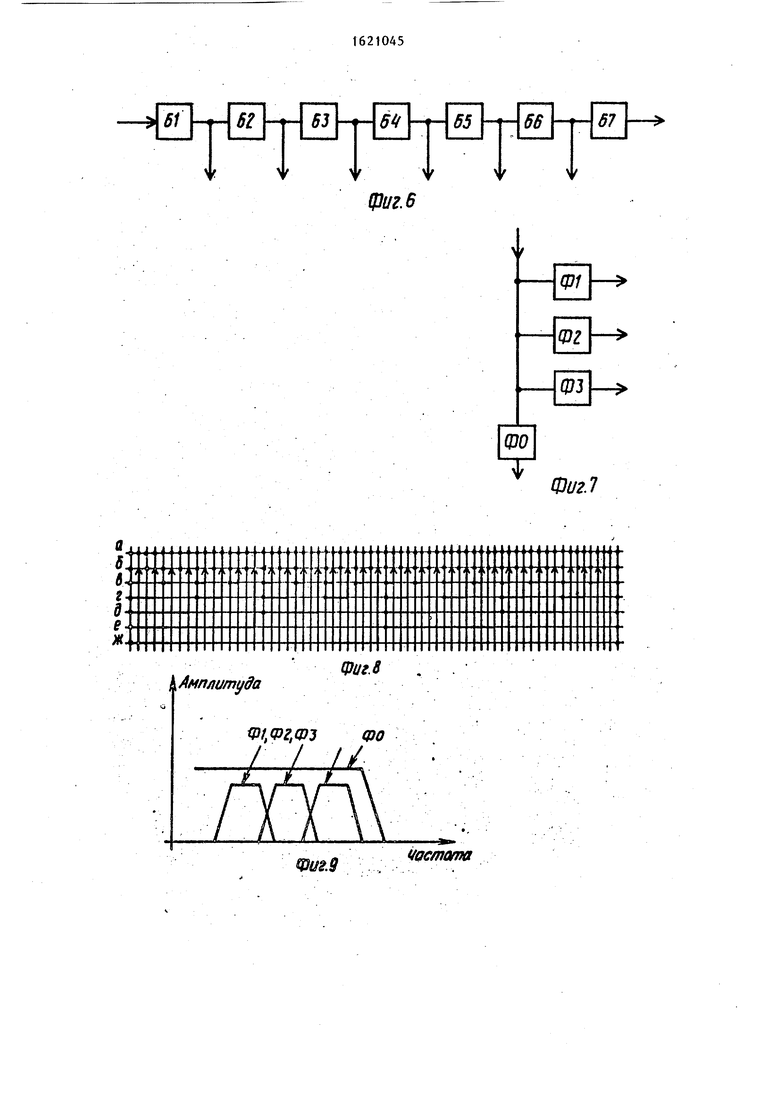

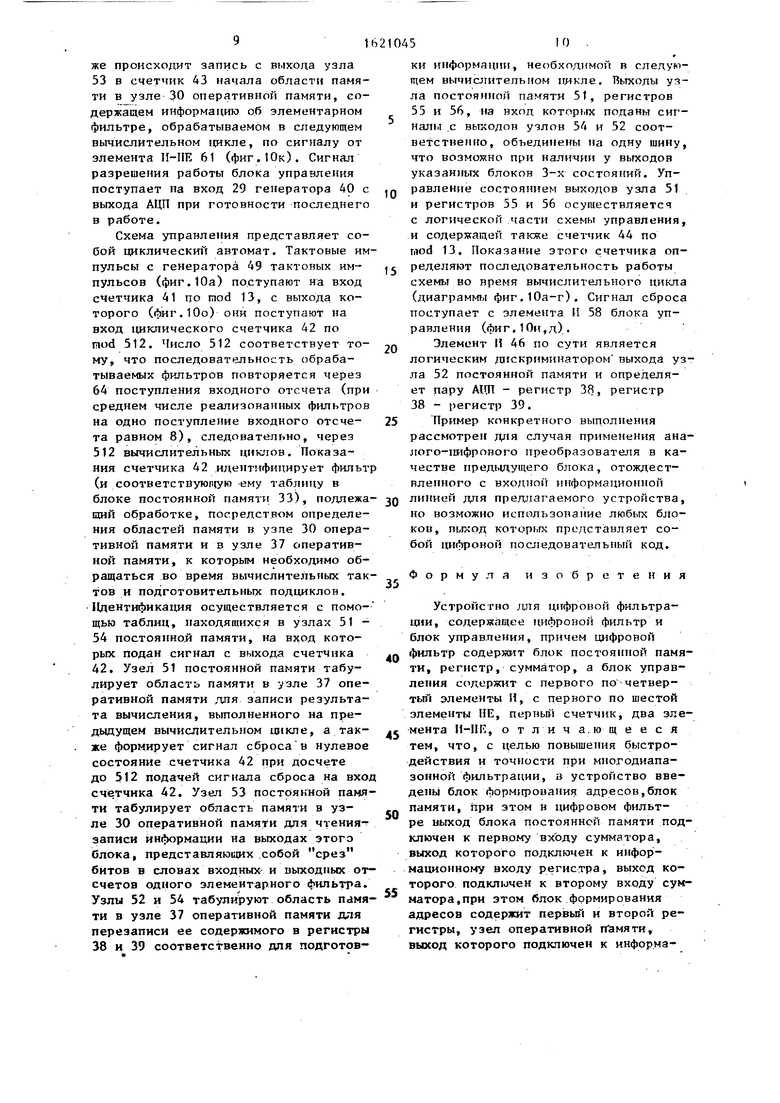

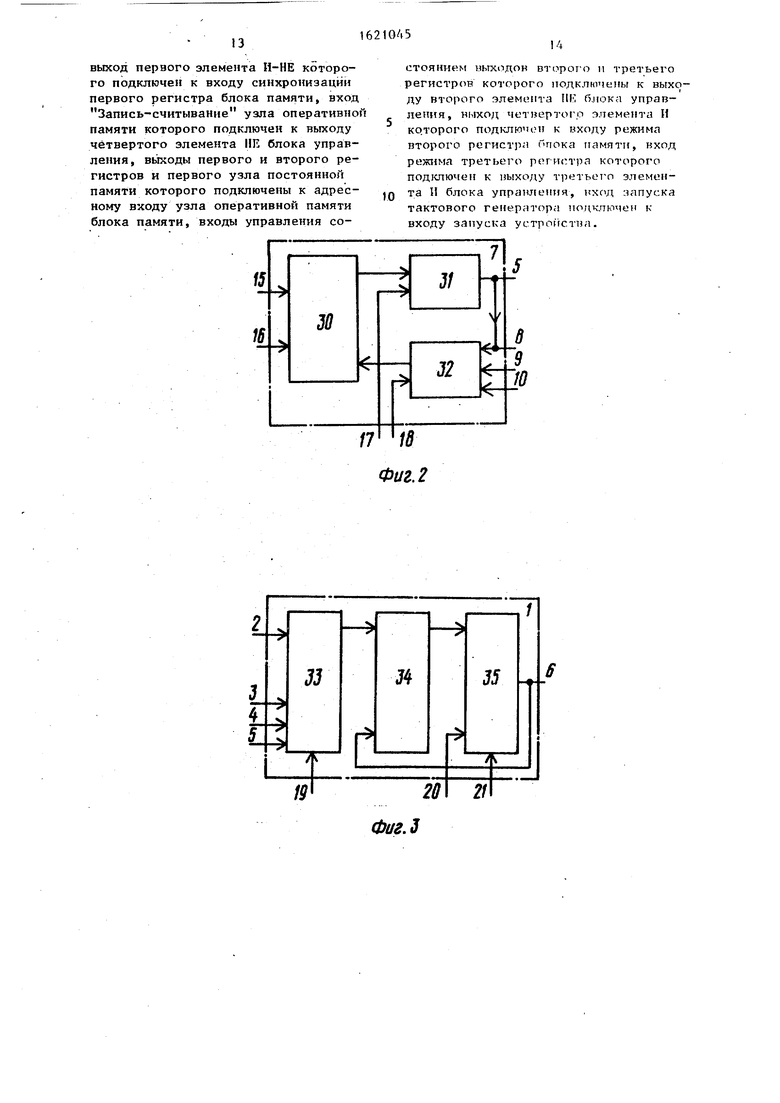

На фиг.1 показана блок-схема устройства для цифровой фильтрации; на фиг.2 - функциональная схема блока формирования адресов; на фиг.З - функциональная схема цифрового фильтра;, на фиг.4 - функциональная схема блока памяти; на фиг.З - функциональная схема блока управления; на фиг.6 - блок-схема каскадного включения блоков фильтров;, на Лиг.7 - блок-схема одного блока фильтров; на фиг.8 - алгоритм обработки полос фильтрации; на фиг.9 - амплитудно- частотные характеристики элементарных фильтров; на фиг.10 - диаграмма работы устройства.

Устройство для цифровой фильтрации содержит цифровой фильтр 1 с информационными входами 2-5 и информационным выходом 6, блок 7 формирования адресов с информационными входам 8-10, блок 11 памяти с информационными выходами 12-13, блок 14 управления, управляющие входы 15-18 блока формирования адресов, управляющие входы 19-21 цифрового фильтра, управляющие входы 22-23 блока памяти, вход управления 29 блока управления, причем входы 4 и 10 являются информационными входами для устройства, а выход 12 - информационным выходом устройства.

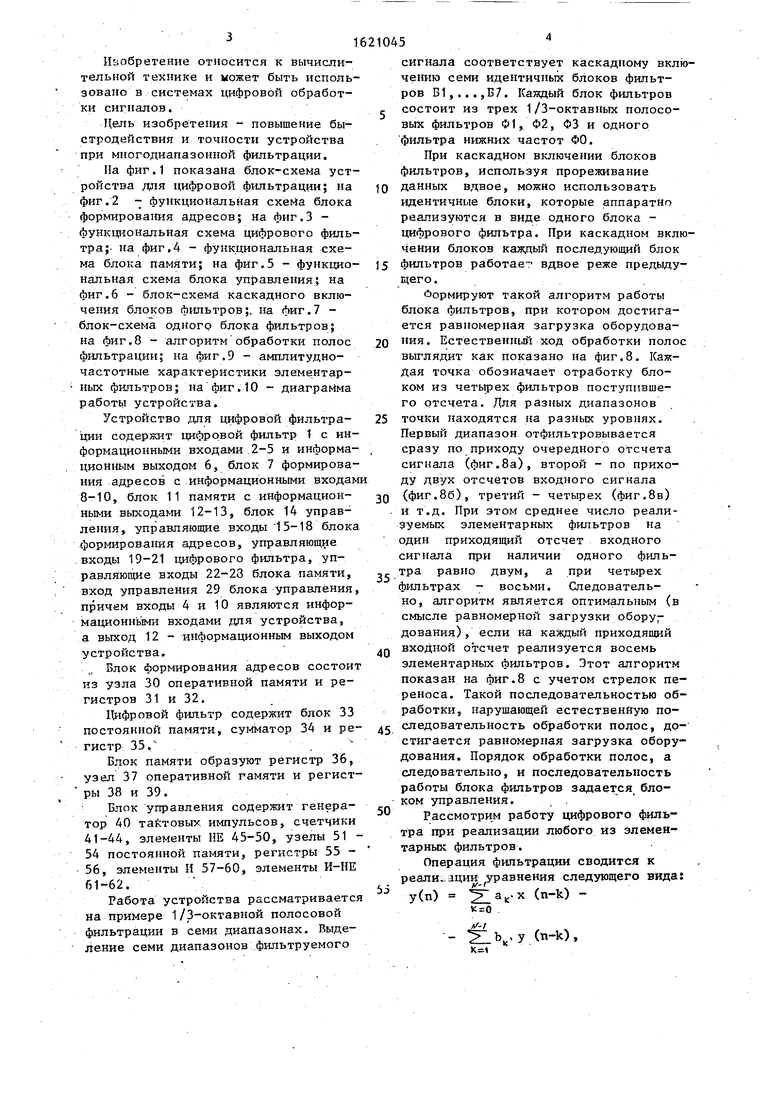

Блок формирования адресов состоит из узла 30 оперативной памяти и регистров 31 и 32.

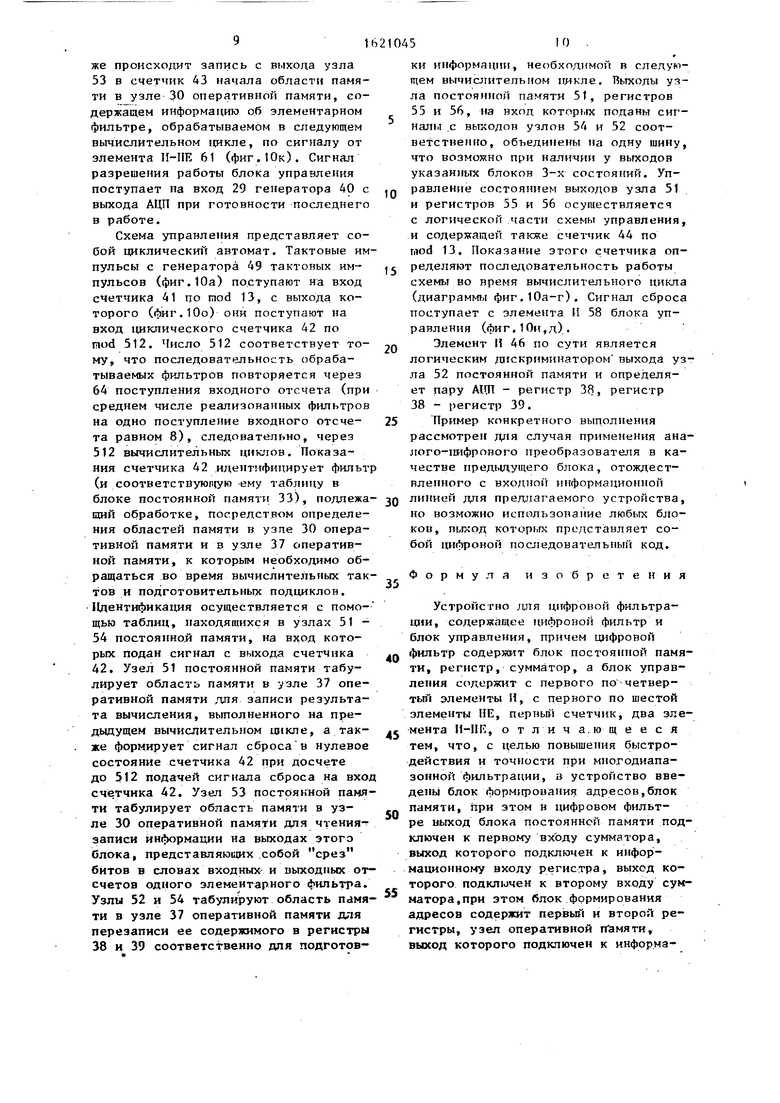

Цифровой фильтр содержит блок 33 постоянной памяти, сумматор 34 и регистр 35 S

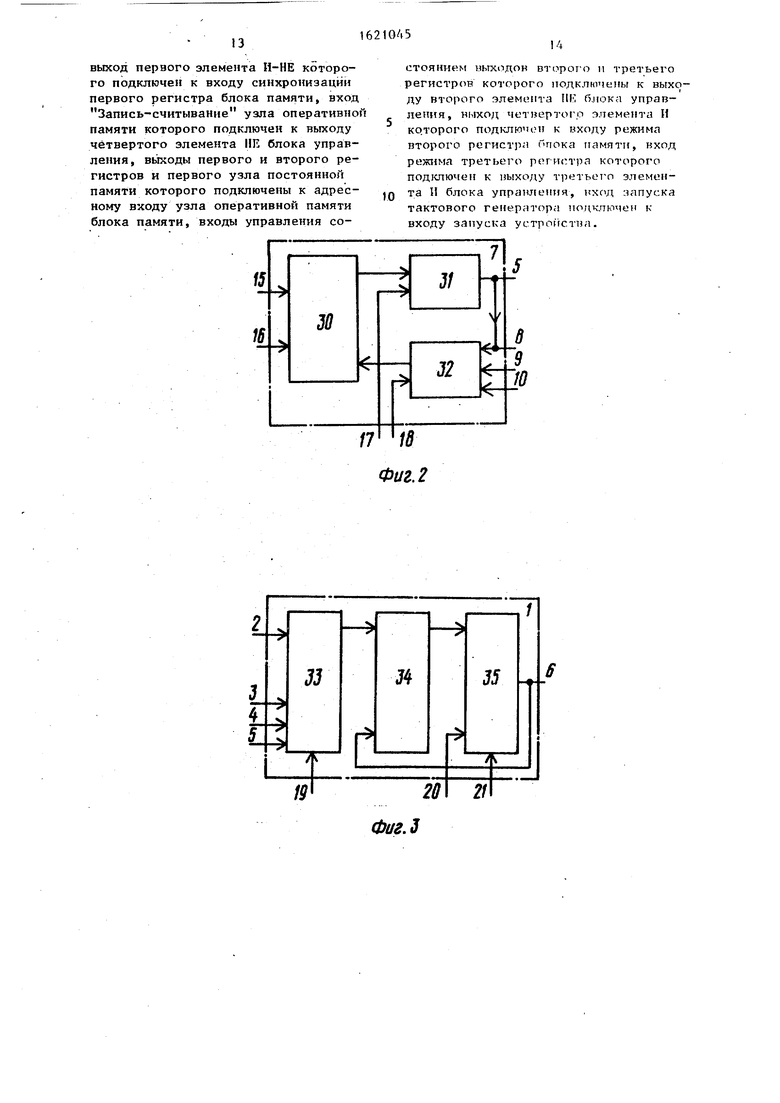

Блок памяти образуют регистр 36, узел 37 оперативной памяти и регист- ры 38 и 39.

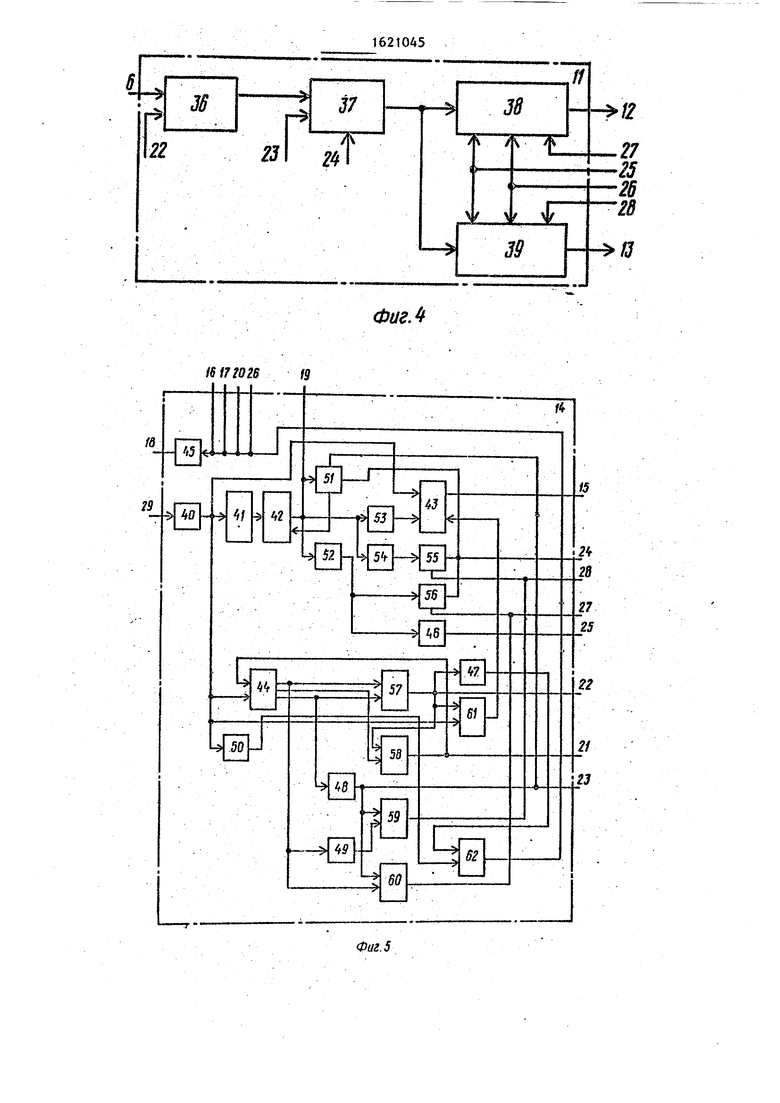

Блок управления содержит генератор 40 тактовых импульсов, счетчики 41-44, элементы НЕ 45-50, узелы 51 - 54 постоянной памяти, регистры 55 - 56, элементы И 57-60, элементы И-ИЕ 61-62.

Работа устройства рассматривается на примере 1/3-октавной полосовой фильтрации в семи диапазонах. Выделение семи диапазонов фильтруемого

0

5

сигнала соответствует каскадному включению семи идентичных блоков фильтров Б1Б7. Каждый блок фильтров

состоит из трех 1/3-октавных полосовых фильтров Ф1, Ф2, ФЗ и одного фильтра нижних частот ФО.

При каскадном включении блоков фильтров, используя прореживание данных вдвое, можно использовать идентичные блоки, которые аппаратно реализуются в виде одного блока - цифрового фильтра. При каскадном включении блоков каждый последующий блок фильтров работав 1 вдвое реже предыдущего.

Формируют такой алгоритм работы блока фильтров, при котором достигается равномерная загрузка оборудования. Естественный ход обработки полос выглядит как показано на фиг.З. Каждая точка обозначает отработку блоком из четырех фильтров поступившего отсчета. Для разных диапазонов точки находятся на разных уровнях. Первый диапазон отфильтровывается сразу по приходу очередного отсчета сигнала (фиг.8а), второй - по приходу двух отсчетов входного сигнала (фиг.Зб), третий - четырех (фиг.8в) и т.д. При этом среднее число реализуемых элементарных фильтров на один приходящий отсчет входного сигнала при наличии одного фильтра равно двум, а при четырех фильтрах - восьми. Следовательно, алгоритм является оптимальным (в смысле равномерной загрузки оборур дования), если на каждый приходящий входной отсчет реализуется восемь элементарных фильтров. Этот алгоритм показан на фиг.З с учетом стрелок переноса. Такой последовательностью обработки, нарушающей естественную по- следовательность обработки полос, достигается равномерная загрузка оборудования. Порядок обработки полос, а следовательно, и последовательность работы блока фильтров задается блоком управления.

Рассмотрим работу цифрового фильтра при реализации любого из элементарных фильтров.

Операция фильтрации сводится к реали. дции уравнения следующего вида;

у(п)

0

5

0

0

5

а к- х (n-k) - fib .у (n-k),

а,к b

где х(п) - выборки входной последовательности;

у(п) - выборки выходной последовательности ; постоянные коэффициента, определяющие характери стики фильтра;

k - порядковый номер выборки N - порядок фильтра. Фильтры блока ФО, Ф1, Ф2, ФЗ идентичны по структуре и различаются лишь выбором коэффициентов а,, и Ьк. В нашем случае используется гребенка рекурсивных фильтров, амплитудно-частотные характеристики (АЧХ) которых представлены на фиг.9.

Для исключения операции умножения отсчетов сигнала на коэффициенты используется перегруппировка, в результате которой для получения выходного отсчета элементарного фильтра используются только операции сдвига и сложения, число которых равно числу разрядов входных данных. Разряды входных выборок используются для адресации памяти, где хранятся значения функций, суммирование которых со сдвигом дает значение выходного отсчета фильтра. Адресуемая память называется памятью результатов. Применение памяти результатов дает возможность повысить быстродействие устройства за счет исключения операции умножения отсчетов входного сигнала на коэффициенты фильтра и повысить точность, путем уменьшения погрешностей, обусловленных ограниченной длиной представления коэффициентов цифрового фильтра.

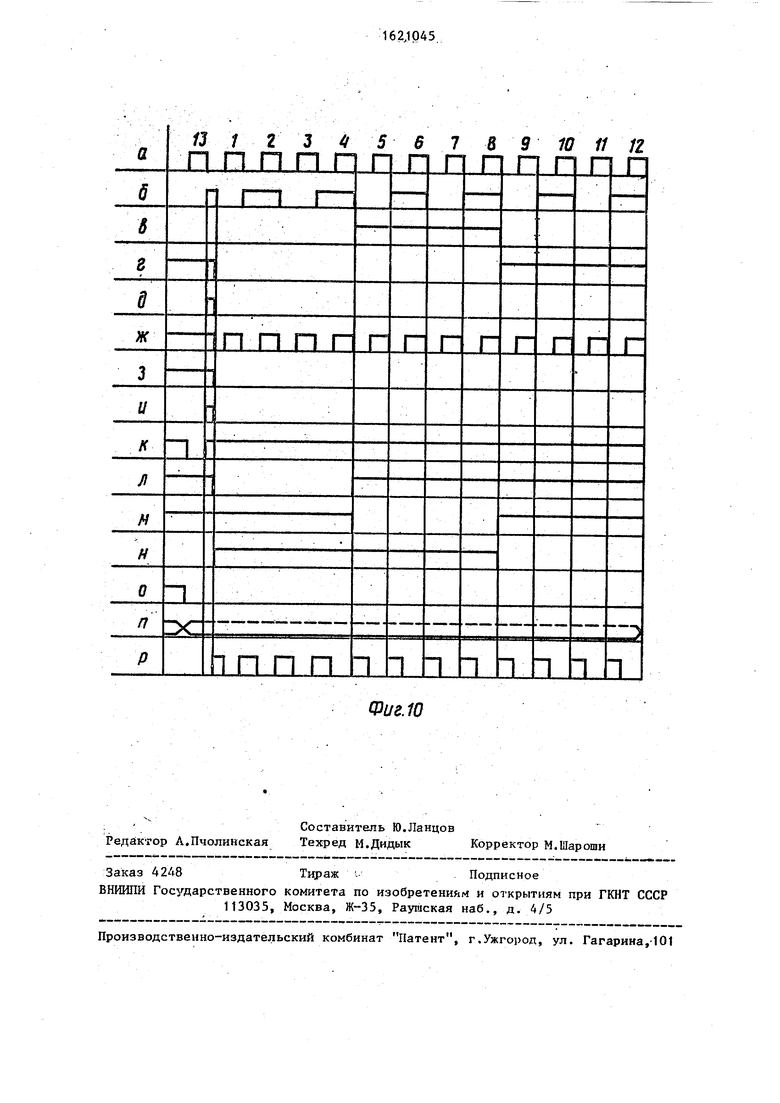

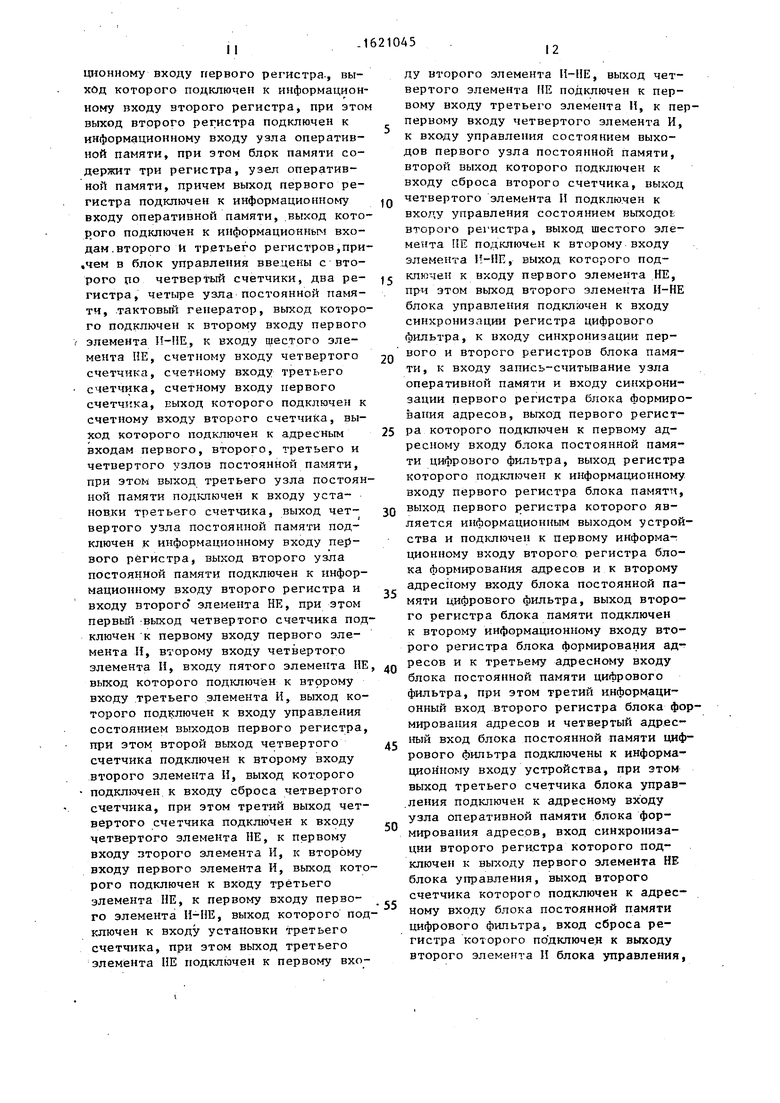

Цикл вычисления выходного отсчета цифровым фильтром разбит на 13 тактов (26 полутактов). Во время 1-г полутакта синхросигнал тактового генератора имеет высокую амплитуду, во время 2-го полутакта - низкую,Каждый цикл вычисления содержит 12 вычислительных и 1 предварительный такт, а также разбит на 3 подготовительных пог,цикла, следующих друг за другом и содержащих соответственно А, 4, 5 тактов (фиг.10).

Число вычислительных тактов соответствует разрядности обрабатываемых слов. Л данном случае разрядность равна 1.. Предварительный такт предназначен для приведения схемы в состяние готовности вычисления отсчета для конкретного элементарного фильт1

; оо621045°

ра. Подготовительные подциклы необ,ходимы для подготовки информации к-, обработке в следующем за данным вычислительном цикле и записи результата вычисления предыдущего цикла. Такая временная организация цикла вычисления дает возможность реализации конвейерной схемы вычисления, так

JQ как в этом случае подготовка информации к вычислению, само вычисление и запись результата вычисления разнесены во времени в разные вычислительные циклы.

5 Устройство работает следующим образом.

Код от А1Щ поступает на информационный вход 10 блока 7 формирования адресов и информационный вход 4 бло20 ка цифрового фильтра 1, а также на вход 29 блока 14 управления. Сигнал на входе 29 осуществлет запуск блока 14 управления и всего устройства в целом. От блока 14 управления

25 на выходе 15 выставляется адрес, по которому по сигналам на выходах 16 и 17 от блока 14 управления производится считывание информации из блока формирования адресов 7 по выходу 5 в

30 блок 1 цифрового Лильтра. Одновременно с этим по сигналу на выходе 26 с блока 14 упратения на информационный вход 2 цифрового фильтра 1 и информационный вход 8 блока 7 формирования адресов поступает информация с ныхода Т2 блока 11 памяти. В соответствии с сигналами на выходах 19-21.поступающими с блока 14 управления, в блоке 1 производится цифро4С вая фильтрация сигналов на входах 2-5. ОтЛильтропанное значение сигналов по сигналу на выходе 22 передается по выходу 6 в блок 11 памяти. По сигналам на выходах 23, 24, 25 и

дц 28 результаты фильтрации передаются с выхода 13 блока 11 памяти на информационный вход 3 блока циЛрового фильтра 1 и информационный вход 9 блока 7 формирования адресов.По сиг5Q налам на выходах 15, 16, 18 и 26, поступаыпим от блока 14 управления, в блоке 7 формирования адресов запоминается значение сигналов на входах 8-10 блока формирования адресов. По

,, сигналам на выходах 23, 24, 26 и 27 результаты фильтрации передаются по выходу 12 на выход устройства.

Во время первого полутакта каждого вычислительного такта, каждого

35

вычислительного цикла на вход 16 узла 30 оперативной памяти элемента И-НЕ 62 (фиг.Юж) поступает сигнал считывания информации по адресу, поступающему одновременно от счетчика 43 на вход 15 узла 30 оперативной памяти и удерживаемого в течение всего такта. Одновременно на вход 17 регистра 31 от элемента И-НЕ 62 на входы 26 регистров 38 и 39 подается сигнал считывания хранящейся в них информации. Считывание информации в данный вычислительный цикл происходит или с пары АЦП - регистр 38, или с пары регистр 38 - регистр 39. Выбор пары зависит от состояния сигнала на вход 25 регистра 39, поданного от элемента НЕ 46 (фиг. 1Эп) управления во время предварительного такта предыдущего вычислительного цикла и удерживаемого в течение всех вычислительных тактов вычислительного цикла.

В 1-й половине вычислительного та такта в регистр 36 производится запись промежуточного результата вычисления, вычисленного в предыдущем такте по сигналу элемента И-НЕ 62, поданному на вход 20 регистра 35.

Во время второй половины вычислительного такта по сигналу элемента И-НЕ 52, поданному на вход 16 узла 30 оперативной памяти, происходит запись содержимого регистра 32, выходы которого по сигналу от элемента НЕ 45 (фиг.Юр) на входе 18 во 2-м полутакте имеют активное состояние. Запись в регистр 32 содержимого регистра 31, регистра 38, регистра 39 или АЦП, происходит также во 2-м полутакте. Таким образом, в узел 30 оперативной памяти во 2-м полутакте в соответствии с уравнением фильтра перезаписывается часть информации, считываемой из него во время 1-го полутакта, и добавляется еще входной отсчет на данном вычислительном цикле и выходной .отсчет предыдущего вычислительного цикла.

Во время 2-го полутакта происходи вычисление промежуточных результатов вычисления в цифровом фильтре по информации, поданной на него с регистра 31, регистра 38, АЦП или регистра 39, а также в зависимости от состояния сигнала на входе 19, поданного от счетчика 42 (фиг.Юп) во время предварительного такта предыдущего вычислительного цикла, удер

5

0

живаемого в течение всех вычислительных тактов и определяющего характер реализуемого фильтра (каждой из трех полосовых или фильтра низкой частоты (йнч)).

Во время 1-го подготовительного подцикла по сигналу с регистра 5 (фиг.Юп) на входе 23 узла 37 оперативной памяти выставляется адрес ячейки памяти, из которой на этом же подцикле в соответствии с сигналом на входе 24 того же узла происходит перезапись содержимого в регистр 39 по сигналу от элемента И 59 на входе 28 регистра 39, поданному также в 1-м подготовительном подцикле, соответствующему выходному отсчету ФИЧ-октавы, расположенной на частотной оси над той, в которой обрабатывается фильтр в следующем вычислительном цикле.

Во втором подготовительном подцикле по сигналу регистра 56 на вхо- 5 де 23 узла 37 оперативной памяти

выставляется адрес ячейки памяти, из которой на этом же подцикле в соответствии с сигналом от элемента НЕ 48 на входе 24 того же узла 37 происходит перезапись в регистр 38 по сигналу от элемента И 60 (фиг.10м) на входе 27 регистра 38, поданному также во втором подцикле, выходного отсчета фильтра, полученного во время предыдущей реализации фильтра, и реализуемого в следующем заданном вычислительном цикле.

В течение третьего подготовительного подцикла по сигналу от узла 51 на входе 23 узла 37 оперативной памяти выставляется адрес ячейки памяти, в которую в соответствии с сигналом от элемента НЕ 48 (фиг. Юн) на входе 24 того же узла 37, происхо- 5 дит запись результатов вычисления выходного отсчета фильтра, реализованного в предыдущий цикл.

На 1-м полутакте каждого 13-го предварительного такта каждого вычислительного цикла по сигналу элемента И 57 (фиг. Юз) на входе 22 регистра 36 происходит запись результатов вычисления данного вычислительного цикла с ыхода регистра 35 в регистр 36. На втором полутакте предварительного такта происходит сброс в нулевое состояние регистра 35 в соответствии с сигналами от элемента И 58 (фиг.Юи) на входе 21 этого же регистра, а так0

0

0

5

же происходит запись с выхода узла

53в счетчик 43 начала области памяти в узле 30 оперативной памяти, содержащем информацию об элементарном фильтре, обрабатываемом в следующем вычислительном цикле, по сигналу от элемента И-НЕ 61 (фиг.Юк). Сигнал разрешения работы блока управления поступает на вход 29 генератора 40 с выхода АЦП при готовности последнего в работе.

Схема управления представляет собой циклический автомат. Тактовые импульсы с генератора 49 тактовых импульсов (фиг.Юа) поступают на вход счетчика 41 по mod 13, с выхода которого (фиг.Юо) они поступают на вход циклического счетчика 42 по nod 512. Число 512 соответствует тому, что последовательность обрабатываемых фильтров повторяется через 64 поступления входного отсчета (при среднем числе реализованных фильтров на одно поступление входного отсчета равном 8), следовательно, через 512 вычислительных циклов. Показания счетчика 42 идентифицирует фильт (и соответствующую ему таблицу в блоке постоянной памяти 33), подлежащий обработке, посредством определения областей памяти в узле 30 оперативной памяти и в узле 37 оперативной памяти, к которым необходимо обращаться во время вычислительных тактов и подготовительных подциклон. Идентификация осуществляется с помощью таблиц, находящихся в узлах 51 54постоянной памяти, на вход которых подан сигнал с выхода счетчика 42. Узел 51 постоянной памяти табулирует область памяти в узле 37 оперативной памяти для записи результата вычисления, выполненного на предыдущем аычислительном цикле, а также формирует сигнал сброса в нулевое состояние счетчика 42 при досчете

до 512 подачей сигнала сброса на вход счетчика 42. Узел 53 постоянной памяти табулирует область памяти в узле 30 оперативной памяти для чтения- записи информации на выходах этого блока, представляющих собой срез битов в словах входных и выходных отсчетов одного элементарного фильтра. Узлы 52 н 54 табулируют область памяти в узле 37 оперативной памяти для перезаписи ее содержимого в регистры 38 и 39 соответственно для подготов

5

0

5

ки информации, необходимой в следующем вычислительном цикле. Выходы узла постоянном памяти 51, регистров 55 и 56, на вход которых поданы сигналы с выходов узлов 54 и 52 соответственно, объединены на одну шину, что возможно при наличии у выходов указанных блоков 3-х состояний. Управление состоянием выходов узла 51 и регистров 55 и 56 осуществляется с логической части схемы управления, и содержащей также счетчик 44 по mod 13. Показание этого счетчика определяют последовательность работы схемы во время вычислительного цикла (диаграммы фиг.10а-г). Сигнал сброса поступает с элемента И 58 блока управления (фиг.10н,д).

Элемент Н 46 по сути является логическим дискриминатором выхода узла 52 постоянной памяти и определяет пару АЦП - регистр 38, регистр 38 - регистр 39.

Пример конкретного выполнения рассмотрен для случая применения аналого-цифрового преобразователя в качестве предыдущего блока, отождествленного с входной информационной Q линией для предлагаемого устройства, но возможно использование любых блоков, пыход которых представляет собой цифровой последовательный код.

35

Формула изобретения

0

Устройство для цифровой фильтрации, содержащее цифровой фильтр и блок управления, причем цифровой фильтр содержит блок постоянной памяти, регистр, сумматор, а блок управления содержит с первого по четвертый элементы И, с первого по шестой элементы НЕ, первый счетчик, два эле- с мента И-ПЕ, отличающееся тем, что, с целью повышения быстродействия и точности при многодиапазонной фильтрации, в устройство введены блок Лормировапия адресов,блок памяти, при этом в цифровом фильтре выход блока постоянной памяти подключен к первому входу сумматора, выход которого подключен к информационному входу регистра, выход которого подключен к второму входу сумматора .при этом блок формирования адресов содержит первый и второй регистры, узел оперативной памяти, выход которого подключен к информационному входу первого регистра, выход которого подключен к информационному входу второго регистра, при этом выход второго регистра подключен к информационному входу узла оперативной памяти, при этом блок памяти содержит три регистра, узел оперативной памяти, причем выход первого регистра подключен к информационному д входу оперативной памяти, выход которого подключен к информационным входам, второго и третьего регистров,причем в блок управления введены с второго по четвертый счетчики, два ре- 15 гистра, четыре узла постоянной памяти, тактовый генератор, выход которого подключен к второму входу первого элемента И-НЕ, к входу шестого элемента НЕ, счетному входу четвертого 20 счетчика, счетному входу третьего счетчика, счетному входу первого счетчика, ЕЫХОД которого подключен к счетному входу второго счетчика, выход которого подключен к адресным 25 входам первого, второго, третьего и четвертого узлов постоянной памяти, при этом выход третьего узла постоянной памяти подключен к входу установки третьего счетчика, выход чет- 30 вертого узла постоянной памяти подключен к информациоиному входу первого регистра, выход второго узла постоянной памяти подключен к информационному входу второго регистра и с входу второго элемента НЕ, при этом первый выход четвертого счетчика подключен к первому входу первого элемента И, второму входу четвертого элемента И, входу пятого элемента НЕ, Q выход которого подключен к второму входу третьего элемента И, выход которого подключен к входу управления состоянием выходов первого регистра, при этом второй выход четвертого 45 счетчика подключен к второму входу второго элемента И, выход которого

подключен к входу сброса четвертого счетчика, при этом третий выход четвертого счетчика подключен к входу ,-п четвертого элемента НЕ, к первому входу второго элемента И, к второму входу первого элемента И, выход которого подключен к входу третьего элемента НЕ, к первому входу перво- . го элемента И-НЕ, выход которого подключен к входу установки третьего счетчика, при этом выход третьего элемента НЕ подключен к первому входу второго элемента И-НЕ, выход четвертого элемента НЕ подключен к первому входу третьего элемента И, к пе первому входу четвертого элемента И, к входу управления состоянием выходов первого узла постоянной памяти, второй выход которого подключен к входу сброса второго счетчика, выход четвертого элемента И подключен к входу управления состоянием выходог. второго регистра, выход шестого элемента НЕ подключен к второму входу элемента 1 -НЕ, выход которого подключен к входу первого элемента НЕ, при этом выход второго элемента И-НЕ блока управления подключен к входу синхронизации регистра цифрового фильтра, к входу синхронизации первого и второго регистров блока памяти, к входу запись-считывание узла оперативной памяти и входу синхронизации первого регистра блока формирования адресов, выход первого регистра которого подключен к первому адресному входу блока постоянной памяти цифрового фильтра, выход регистра которого подключен к информационному входу первого регистра блока памяти, выход первого регистра которого является информационным выходом устройства и подключен к первому информационному входу второго регистра блока формирования адресов и к второму адресному входу блока постоянной памяти цифрового фильтра, выход второго регистра блока памяти подключен к второму информационному входу второго регистра блока формирования адресов и к третьему адресному входу блока постоянной памяти цифрового фильтра, при этом третий информационный вход второго регистра блока фомирования адресов и четвертый адресный вход блока постоянной памяти цифрового фильтра подключены к информационному входу устройства, при этом выход третьего счетчика блока управления подключен к адресному входу узла оперативной памяти блока формирования адресов, вход синхронизации второго регистра которого подключен к выходу первого элемента НЕ блока управления, выход второго счетчика которого подключен к адресному входу блока постоянной памяти цифрового фильтра, вход сброса регистра которого подключен к выходу второго элемента И блока управления,

выход первого элемента И-НЕ которого подключен к входу синхронизации первого регистра блока памяти, вход Запись-считывание узла оперативно памяти которого подключен к выходу четвертого элемента НЕ блока управления, выходы первого и второго регистров и первого узла постоянной памяти которого подключены к адресному входу узла оперативной памяти блока памяти, входы управления со15

стоянием ныходон второт о и третьего регистров которого подключены к выходу второго элемента ПК блока управления, ныход четвертого опемента И которого подключен к входу режима второго регистра Гттока памяти, вход режима третьего регистра которого подключен к ныходу третьего элемента И блока управления, иход чапуска тактового генератора подключен к входу запуска устроиспы.

Фиг. 2

Фиг.З

а

Фиг Л

Амплитуда

Фиг. 8

ЩФг,ФЗ фо

/ / //

Фи.9

фиг. 6

Фиг. 7

час/пата

Фиг.Ю

| Пепед, Лиу Б | |||

| Цифровая обработка сигналоп | |||

| Теория, проектирование, реализация | |||

| - Киев: Высшая школа, 1979, с.210-216 | |||

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Steenaart W., Dubois D., flonke- wich 0 | |||

| Stored-Product Digital Filtering, Structures, Potential and Applications | |||

| - Ptoceding of the European Conference on Circuit Theory and Design, 1981. | |||

Авторы

Даты

1991-01-15—Публикация

1987-11-25—Подача