Изобретение относится к импульсной и вычислительной технике, в частности к синхронным счетчикам, и может быть использо- вано в устройствах промышленной автоматики и вычислительной техники, отвечающих повышенным требованиям к времени восстановления работоспособности после отказа.

Известен двоично-десятичный счетчик, содержащий два элемента НЕ, два элемента ИЛИ, четыре элемента И и четыре разряда, каждый из которых содержит два элемента

И-НП, элемент И с одним инверсным входом и триггер с соответствующими конструктивными связями 1.

Недостатком известного счетчика является низкая эксплуатационная отказоустойчивость, обусловленная необходимостью проведения замены всей интегральной микросхемы при выходе из строя (отказе) одного из разрядов.

Наиболее близким по технической сущности является двоично-десятичный счетчик, содержащий два элемента НЕ, два

N5

элемента ИЛИ, четыре элемента И, основные и резервный разряды, причем резервный разряд содержит триггер, три элемента И-НЕ, элемент 2-2И-ИЛИ м элемент И, первый разряд содержит два элемента И-НЕ, элемент И/И-НЕ, триггер, три элемента 2-2И-ИЛИ, и элемент И, второй разряд содержит элемент И/И-НЕ. четыре элемента 2-2И-ИЛИ, элемент И, два элемента И-НЕ и триггер, третий разряд содержит элемент И/И-НЕ, три элемента 2-2И-ИЛИ, элемент И, два элемента И-НЕ и триггер, четвертый разряд содержит элемент И-И-НЕ, два элемента И-НЕ, триггер и элемент 2-2И-ИЛИ с соответствующими конструктивными связями 2.

Недостатком известного устройства является отсутствие средств контроля за правильностью срабатывания его основных функциональных элементов, что приводит к необходимости разработки дополнительных средств контроля и диагностики, а также сравнительно длительная процедура восстановления работоспособности (найти отказавший разряд и исключить его из работоспособной структуры).

Целью изобретения является повышение достоверности функционирования устройства и автоматизация процесса восстановления его работоспособности.

Поставленная цель достигается тем, что двоично-десятичный счетчик, содержащий два элемента НЕ, два элемента ИПМ, четыре элемента И, основные и оезервньн разряды причем резервный разряд со/ еужит триггер, элемент И/И-НЁ, элемент 2-2И- ИЛИ, элемент И и дня элемента И--Не, пор- аый разряд содержит три; rep, элемент И/И- НЕ, три элемента 2-2 И- ИЛИ, элемент И и два элемента i/ЬЧЕ, второй разряд содержит триггер, элемент И/И-НЕ, четыре элемента 2-2И-ИЛИ, элемент И и два элемента И -НЕ, третий разряд содержит триггер, элемент И/И-НЕ, три элемента 2-2И-ИЛИ, элемент И и два элемента И- НЕ, четвертый разряд содержит триггер, элемент И, два элемента И-НЕ и элемент 2-2И-ИЛИ, контрольный L-вход счетчика соединен с входом первого элемента НЕ счетчика, выход которого соединен с первыми входами первого и второго элементов И-НЕ каждого, включая и резервный, разряда, вход установки в О счетчика соединен с входом первого элемента ИЛИ счетчика, выход которого соединен с R0 входом триггера каждого, включая и резервный, разряда, синхровход счетчика соединен с входом второго элемента НЕ счетчика, выход которого соединен с инверсными входами элементов И первого-четвертого разрядов, R-вход счетчика соеди нен с первым входом первого элемента И счетчика, второй вход которого соединен с Т-входом счетчика и с третьим входом четвертого элемента И счетчика, выхлд первого элемента И-НЕ каждого, включая и резервный, разряда соединен с l-входом триггера одноименного разряда, выход второго элемента И-HF каждого, включая и резервный,

0 разряда соединен с вторым входом первого элемента И-НЕ и с К-входом триггера одноименного разряда, выход г.ервого элемента И счетчика соединен с первым оходом третьего и с четвертым входом второго эле5 ментов И счетчика, с прямым входом элемента И первого разряда, с третьим входом элемента И второго разряда и с третьим входом элемента И третьего разряда, инверсный выход элемента И/И-НЕ резервного

0 разряда соединен с первым входом второй группы входов элемента 2-2И-ИЛИ, с первым входом элемента И одноименного и с вторым входом первой группы входов третьего элемента 2-2И-ИЛИ первого разрядов,

5 прямой выход элемента И/И - НЕ резервного оазряда соединен с входом первой группы входов элемента 2-2И-ИЛИ одноименного и с первым входом второй группы входов третьего элемен0 то 2 - 2 И - И Л И первого разрядов , информационный яход предустанова первого разряда соединен с первым входом первой гг /ппы входов первого элемента 2- 2И-ИЛИ одноименного и с вторым входом

5 второй группы входов элемента 2-2И-ИЛИ резервного разряда, выход которого соединен с вторым входом второго элемента И- НЕ одноименного разряда, выход эпемента И резервною разряда соединен ее счетным

С входом триггера одноименного разряда, г.рямой выход которого соединен с первым входом первой группы входов третьего элемента 2°-2И-ИЛИ первого разряда, инверсный выход элемента И/И-НЕ первого

5 разряда соединен с первым входом второй группы входов первого, с первым входом второй группы входов второго элементов 2-2И-ИЛИ одноименного и с вторым входом первой группы входов четвертого эле0 мента 2-2И-ИЛИ второго разряда, прямой выход элемента И/И-НЕ первого разряда соединен с первым входом элемента И/И- НЕ резервного разряда, с вторым входом первой группы входов первого, с вторым

5 входом первой группы входов второго элементов 2-2И-ИЛИ одноименного и с первым входом второй группы входов четвертого элемента 2-2И-ИЛИ второго разряда, информационный вход предуста- нова второго разряда соединен с первым

входом napL-e группы входов второго элемента 2-2И-ИЛИ одноименного разряда и с вторым входом вшрой группы входов первого элемента 2-2И-ИЛИ первого разряда, выход которого соединен с вторым входом второго элемента И-НЕ одноименного разряда, выход элемента И первого разряда соединен с первым входом первой группы входов второго элемента 2-2И-ИЛИ одноименного и с вторым входом элемента И резервного разряда, выход второго элемента 2-2И-ИЛИ первого разряда соединен со счетным входом триггера одноименного разряда, прямой выход которого соединен с вторым входом ВТОРОЙ группы входов третьего элемента 2-2И-ИЛ И одноименного и с первым входом первой группы входов четвертого элемента 2-2И-ИЛИ второго разряда, инверсный выход элемента И/И- НЕ второго разряда соединен с первым входом второй группы входов второго элемента 2-2И-ИЛИ, с первым входом второй группы входов третьего элемента 2-2И-ИЛИ одноименного и с вторым входом первой группы входов третьего элемента 2-2И-ИЛИ третьего разряда, прямой выход элемента И/И- НЕ второго разряда соединен с первым входом элемен-та И/И-НЕ первого разряда, с вторым входом первой группы входов второго, с вторым входом первой группы входов третьего элементов 2-2И-ИЛИ второго разряда и с первым входом второй группы входов третьего элемента 2-2И-ИЛИ третьего разряда, выход второго элемента 2-2И-ИЛИ второго разряда соединен с вторым входом второго элемента И-НЕ одноименного разряда, выход первого элемента 2-2И-ИЛИ второго разряда соединен с вторым входом элемента И одноименного разряда, выход которого соединен с первым входом первой группы входов третьего элемента 2-2И-ИЛИ одноименного и с вторым входом второй группы входов второго элемента 2-2И-ИЛИ первого разряда, выход третьего элемента 2-2И- ИЛИ второго разряда соединен со счетным входом триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов четвертого элемента 2-2И-ИЛИ одноименного и с первым входом первой группы входов третьего элемента 2-2И-ИЛИ третьего разряда, ин- в е р с и выход элемента И/И- НЕ третьего разряда соединен с первым входом второй группы входов первого элемента 2-2И- ИЛИ второго разряда, с первым входом второй группы входов первого, с первым входом второй группы входов второго элементов 2-2И-ИЛИ третьего разряда и с вторым входом первой группы входов элемента 2-2И-ИЛИ четвертого разряда, прямой выход элемента И/И-НЕ третьего разряда соединен с. первым входом элемента И/И-НЕ 5 второго разряда, с вторым входом первой группы входов первого, с вторым входом первой группы входов второго элементов 2-2И-ИЛИ третьего разряда и с первым входом второй группы входов элемента 210 2И-ИЛИ четвертого разряда, информаци онный вход предустанова третьего разряда соединен с вторым входом второй группы входов второго элемента 2-2И-ИЛИ второго разряда и с первым входом первой груп5 пы входов первого элемента 2-2И-ИЛИ третьего разряда, информационный вход предустанови четвертого разряда соединен с вторым входом второго элемента И-НЕ одноименного разряда и с вторым входом

0 второй группы входов первого элемента 2- 2И-ИЛИ третьего разряда, выход которого соединен с вторым входом второго элемента И-НЕ третьего разряда, выход элемента И третьего разряда соединен с первым вхо5 дом первой группы входов второго элемента 2-2И-ИЛИ третьего разряда и с вторым входом второй группы входов третьего элемента 2-2И-МЛЙ второго разряда, выход зторого элемента 2--2И-ИЛИ третьего рзз0 ряда соединен со счетным входом триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов третьего элемента 2-2И-ИЛИ третьего к с первым входом первой группы

5 входов элемента 2-2И-ИЛ И четвертого разрядов, инверсный выход триггера третьего разряда соединен с вторым входом вгорой группы входов первого элемента 2-2И-ИЛ И второго разряда, выход элемента И четвер-.

0 того разряда соединен со счетным входом триггера одноименного разряда и с вторым входом второй группы входов второго элемента 2-2И-ИЛИ третьего разряда,инверсный выход триггера четвертого разряда

5 соединен с вторым входом первой группы входов первого элемента 2-2И-ИЛИ второго разряда, прямой выход триггера четвертого разряда соединен с вторым входом вторий группы входов элемента 2-2И-ИЛИ

0 одноименного разряда, выход третьего элемента 2-2И-ИЛИ первого разряда является первым информационным выходом счетчика и соединен с первыми входами элементов И второго и третьего разрядов, с

5 третьим входом второго, с вторым входом третьего и с вторым входом четвертого элементов И счетчика, выход четвертого элемента 2-2И-ИЛИ второго разряда является вторым информационным выходом счетчи- ка и соединен с вторым входом элемента И

третьего разряда и с вторым входом второго элемента И счетчика, выход третьего элемента 2--2И-ИЛИ третьего разряда является третьим информационным выходом счетчика и соединен с первым входом второго элемента И счетчика, выход которого соединен с первым входом второго элемента ИЛИ счетчика, второй вход которого сое- динен с выходом третьего элемента И счетчика, выход элемента 2-2И--ИЛИ четвертого разряда является четвертым информационным выходом счетчика и соединен с третьим входом третьего элемента И счетчика и с первым входом четвертого элемента И счетчика, выход которого является выходом переноса максимального значения счетчика, выход второго элемента ИЛИ счетчика соединен с прямым входом элемента И четвертого разряда, дополнительно содержит пятый и шестой элементы И, третий элемент ИЛИ, каждый, кроме четвертого, оазояд дополнительно содержит элемент ИЛИ, т р и ггер каждого , включая и резервный , разряда в своей структуре содержит два элемента 2И-ИЛИ-НЕ, четыре элемента И, два элемента НЕ, четыре элемента И--НЕ, элемент и элемент 7И-ЙЛИ-НЕ, причем Ro - &ход триггера каждого разряда соединен с первым входом четвертого элемента И-НЕ, с первым входом первого элемента И, с яторым входом первой и с первым входом РТОРОЙ групп входов первого элемента 2И- ИЛИ- НЕ , 1-вход триггере каждого разряда соединен с третьем входом второй группы входов первого элемента 2И-ИЛИ-НЬ, с вторым входом элемента И/И-ИЕ м с это- рум входом тротьпй группы входов элемента 7 И-И Л И-НЕ инверсный Ro-вход триггера каждого разряда дополнительно соединен с первым входом четвертого элемента И, вход синхронизации триггера каждого разряда соединен с четвертым входом второй группы входов перзого и с первым входом первой группы входов второго элементов 2И-ИЛИ-НЕ, а также с входом первого элемента НЕ, К-вход триггера каждого разряда соединен с вторым входом первой группы входов второго элемента 2И-ИЛИ- НЕ, с первым входом элемента И/И-НЕ и с первым входом четвертой группы входов элемента 7И-ИЛИ-НЕ, инверсный S-вход триггера каждого разряда соединен с четвертым входом первой и с первым входом второй групп входов второго элемента 2И- ИЛИ-НЕ, с вторым входом четвертого элемента И, с третьим входом второго элемента И и с третьим входом третьего элемента И-НЕ, зход Rr- установки в исходное состояние средств функционального контроля

триггера каждого разряда соединен с первым входом седьмой группы входов элемента 7И--ИЛИ-НЕ, выход первого элемента 2И-ИЛИ-НЕ соединен с вторым входим

второго элемента И и с вторым входом второй группы входов второго элемента 2И- ИЛИ-НЕ, выход которого соединен с вторым входом первого элемента И и с первым входом порвой группы входов первого

0 элемента 2И-ИЛИ-НЕ, выход первого элемента И соединен с порчь;м входов первого элемента , с третьи а:-.одом второй с вторым входом четвертой г. с вторым входом питой групп входов элемента 7И-ИЛИ-НС,

5 выход первого элемента НЕ соединен с зто- р ы м в х о д о первого и с п е р - в ы м входом второго элементов И-НЕ, с третьим входом пер- вой и с яторым входом второй rpvnn ВХОДОЕ.

0 элемента 7И-ИЛИ-НЕ. выход второго элемента И соединен с вторым входом второго элемента И-НЕ, с четвертым входом первой, с первым входом третьей и с вторым входом шестой групп входов элемента 7И

5 ИЛИ-НЕ, выход первого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ, с первым входом второго и с первым входом третьего элементов И, выход второго элемента И-НЕ соединен с вторым вхо0 дом четвертого элемента И-НЕ, с вторым входом третье о элемента И и с третьим входом первого элемента И, выход третьего элемент И соединен с входом второю элемента Н;, с третьим входом третьей-шес5 той rpvnn входов элемента 7И-ИЛИ-НЕ. выход второго элемент НЕ соединен с вторым входом парной и с пеовым входом агорой групп входов элемента 7И-1/1ЛИ-НЕ. выход четвертого элемента И соединен с

0 пятыми входами первой и второй, с четвертыми входами третьей-шестой групп входов элемента 7И-ИЛИ-НЕ, инверсный выход элемента И/И-НЕ соединен с пятыми входами третьей и четвертой групп входов эле5 . мента 7И-ИЛИ-НЕ, прямой выход элемента И/И-НЕ соединен с пятыми входами пятой и шестой групп входов элемента 7И-ИЛИ- НЕ, ЕЫХОД третьего элемента И-НЕ является прямым выходом триггера каждого

0 разряда и соединен с третьим входом четвертого элемента И-НЕ, с третьим входом первой группы входов второго элемента 2И-ИЛИ-НЕ. с первым входом первой и пятой групп входов элемента 7И-ИЛИ-НЕ,

5 выход четвертого элемента И-НЕ является инверсным выходом триггера каждого разряда и соединен с первым входом третьего элемента И-НЕ, с вторым входом второй труппы входов первого элемента 2И-ИЛИ- НЕ, с четвертым входом второй и с первым

входом iwftcit л трупп входов элемента 7И- ИЛИ-НЕ, инверсный выход которого является выходом Отсутствие откьза триггера каждого разряда, прямой выход элемента 7И-ИЛИ-НЕ соединен с вторым входом своей седьмой группы входов, вход установки в исходное состояние средств функционального контроля устройства соединен с входом третьего элемента ИЛИ устройства, выход которого соединен с инверсными Rp-входами триггеров каждого, включая и резервный, разряда, выход Отсутствие отказа триггера резервного разряда соединен с вторым входом элемента ИЛИ одноименного разряда и с первым входом пятого элемента И устройства, второй вход котрро- го соединен с первым входом элемента ИЛИ и с прямым выходом элемента И/И-НЕ резервного разряда, выход Отсутствие отказа триггера первого разряда соединен с вторым входом элемента И/И- НЕ резервного разряда и с первым входом элемента ИЛИ первого разряда, второй вход которого соединен с выходом элемента И/И-НЕ одноименного разряда, выход От- сутствие отказа триггера второго разряда соединен с вторым входом элемента И/И- НЕ первого разряда и с первым входом элемента ИЛИ второго разряда, второй аход которого соединен с прямым выходом эле- мента И/И-НЕ второго разряда, выход Отсутствие отказа триггера третьего разряда соединен с вторым входом элемента И/И- НЕ второго разряда и с первым входом элемента ИЛИ третьего разряда, второй вход которого соединен с прямым выходом элемента И/И-НЕ одноименного разряда, выход Отсутствие отказа .триггера четвертого разряда соединен с входами элемента И/И-НЕ третьего разряда и с первым входом первой группы входов первого элемента 2-2И-ИЛИ второго разряда, выходы элементов ИЛИ резервного, первого, второго и третьего разрядов соединены соответственно с первым-четвертым входами шестого элемента И счетчика, выход которого является выходом Отсутствие полного отказа счетчика, выход пятого элемента И является выходом Отсутствие .частичного отказа счетчика.

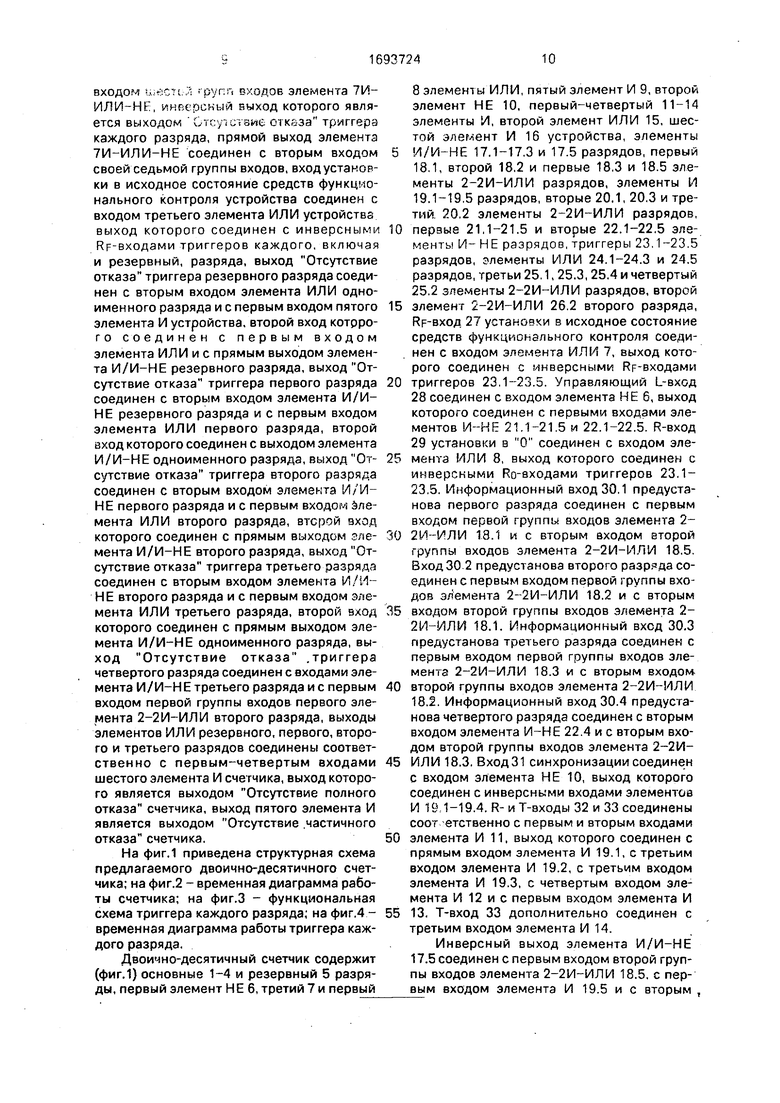

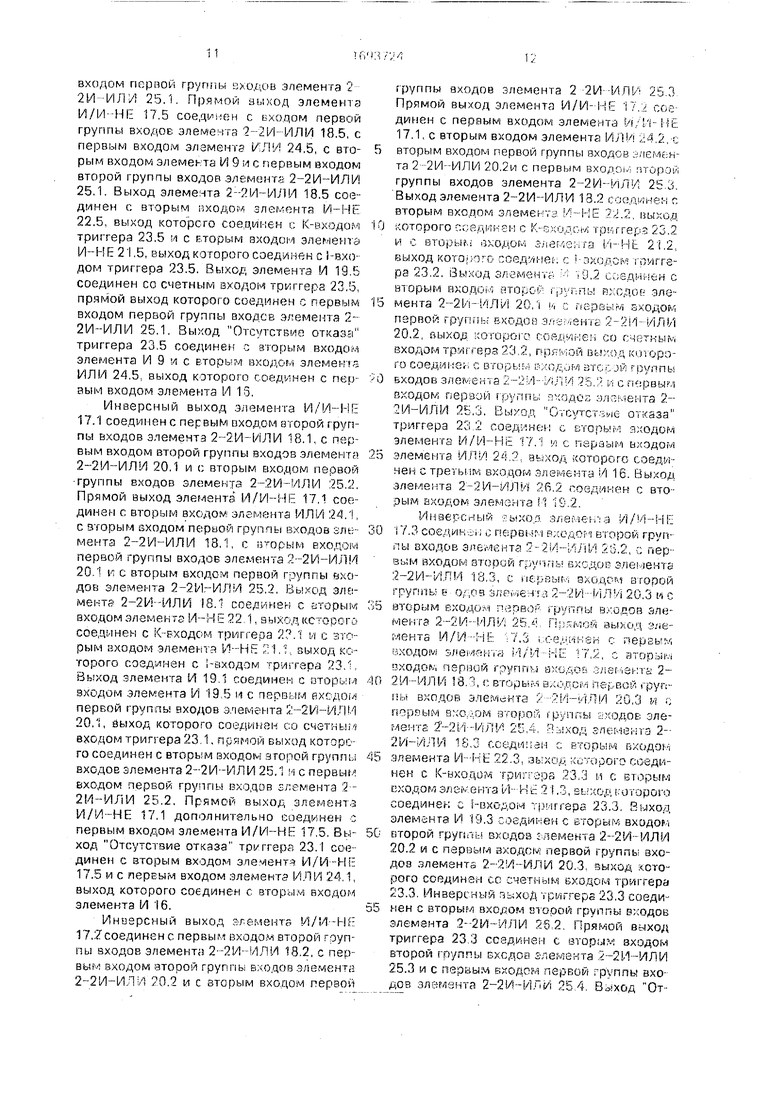

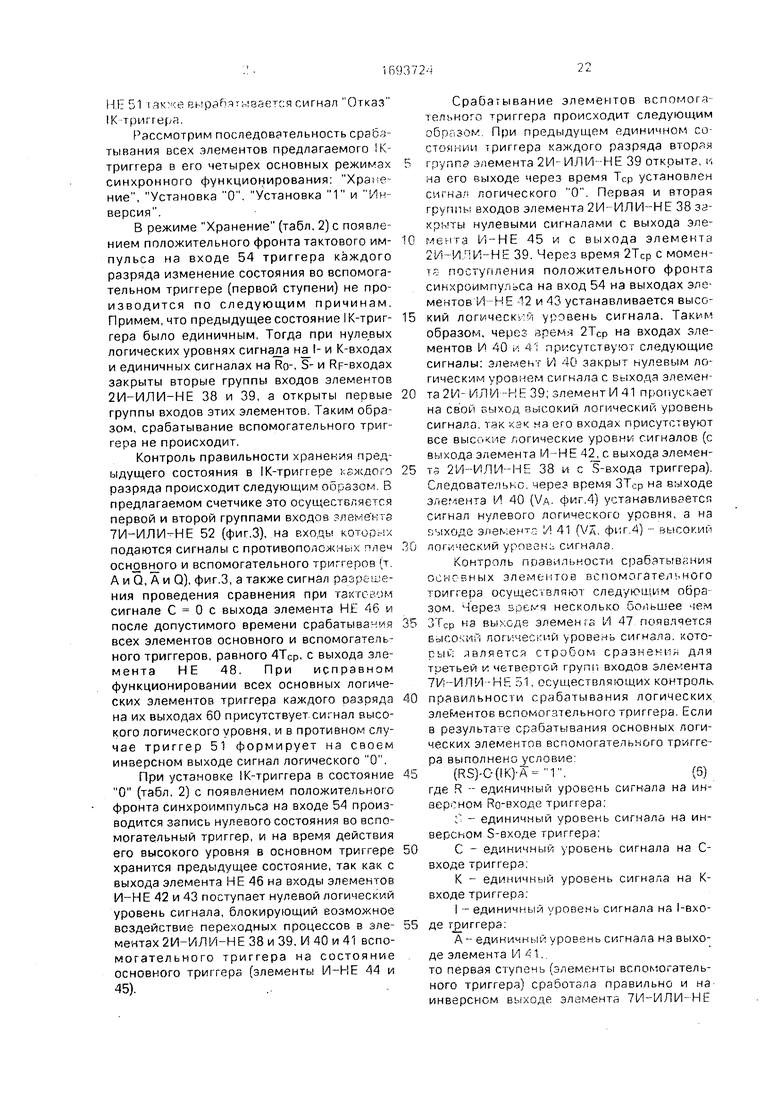

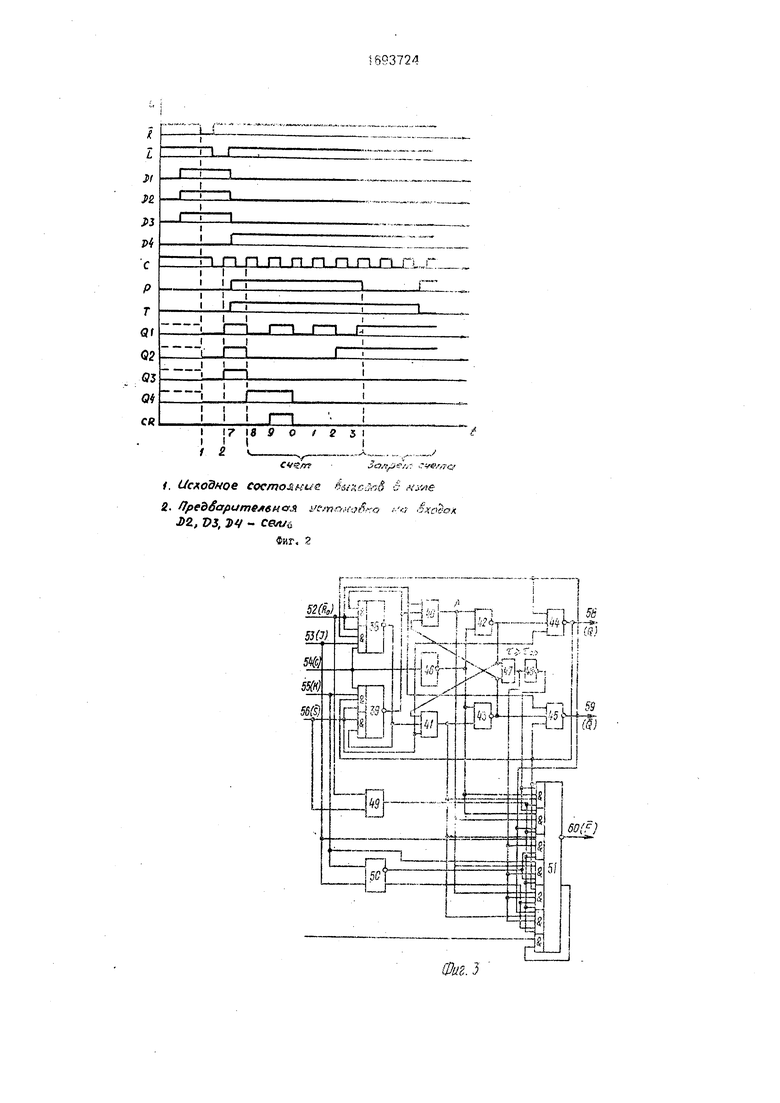

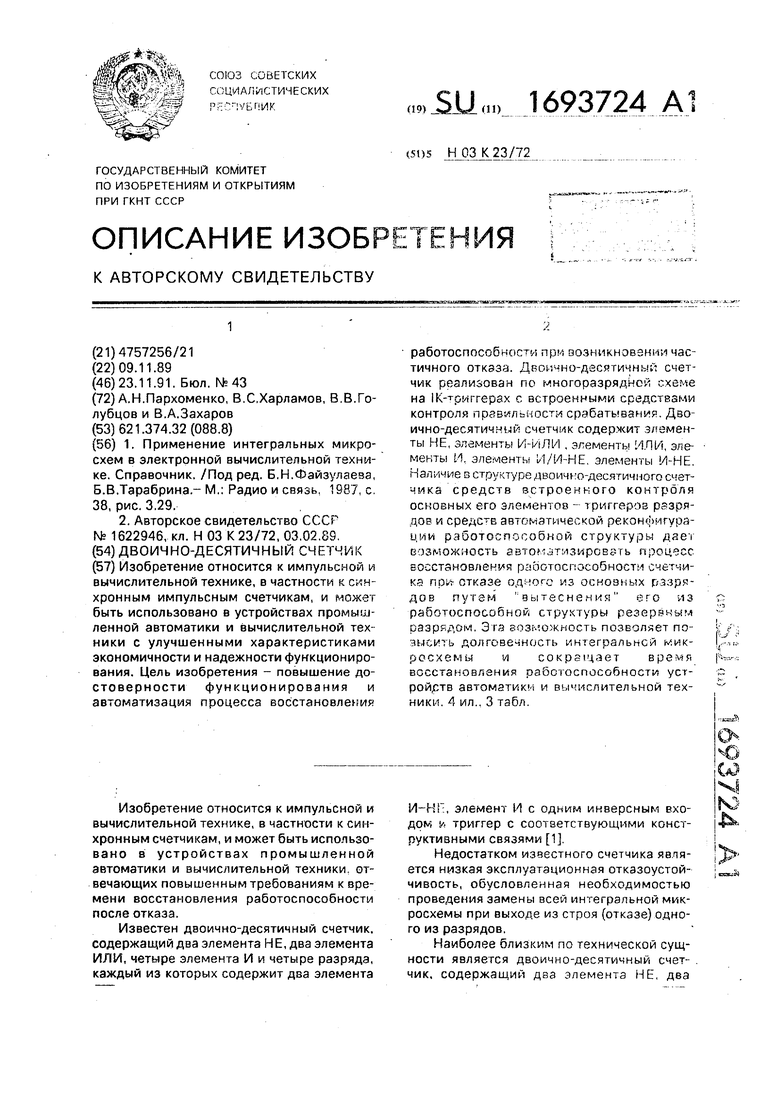

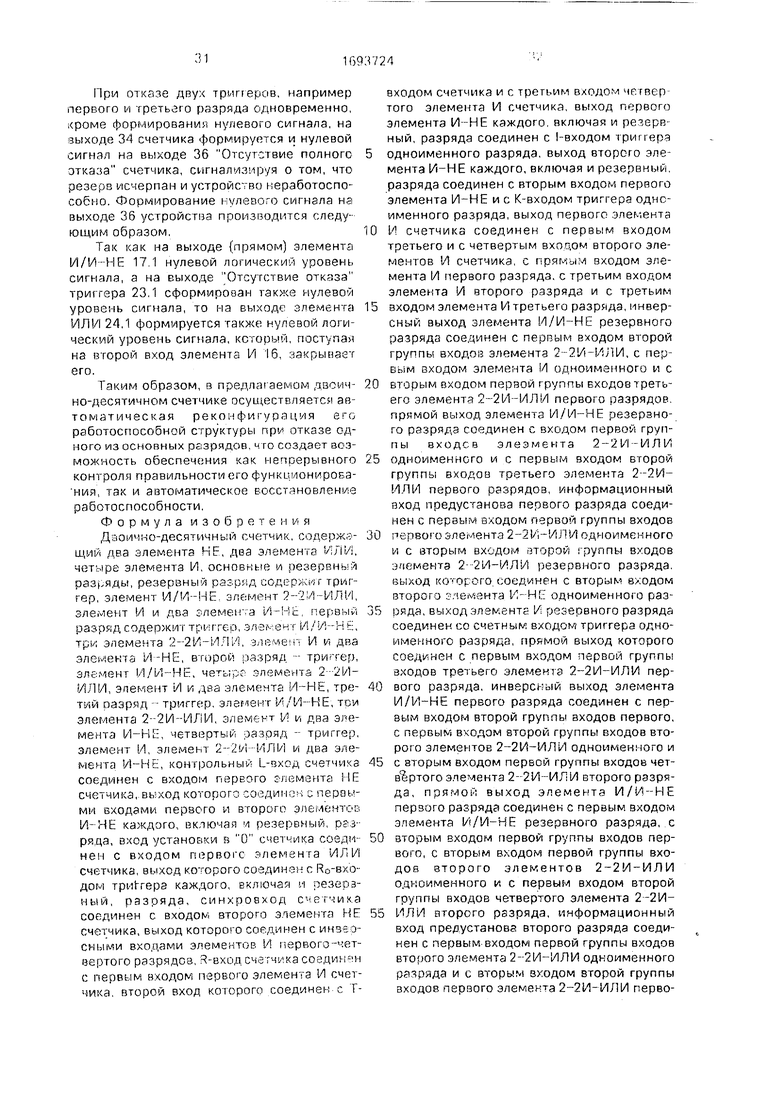

На фиг.1 приведена структурная схема предлагаемого двоично-десятичного счетчика; на фиг.2 - временная диаграмма работы счетчика; на фиг.З - функциональная схема триггера каждого разряда; на фиг.4 - временная диаграмма работы триггера каждого разряда.

Двоично-десятичный счетчик содержит (фиг.1) основные 1-4 и резервный 5 разряды, первый элемент НЕ 6, третий 7 и первый

8 элементы ИЛИ, пятый элемент И 9, второй элемент НЕ 10, первый-четвертый 11-14 элементы И, второй элемент ИЛИ 15. шестой элемент И 16 устройства, элементы И/И-НЕ 17.1-17.3 и 17.5 разрядов, первый

18.1,второй 18.2 и первые 18.3 и 18.5 элементы 2-2И-ИЛИ разрядов, элементы И 19.1-19.5 разрядов, вторые 20,1, 20.3 и третий. 20.2 элементы 2-2И-ИЛИ разрядов, первые 21,1-21.5 и вторые 22.1-22.5 элементы И- НЕ разрядов, триггеры 23.1-23.5 разрядов, элементы ИЛИ 24.1-24.3 и 24.5 разрядов, третьи 25.1,25.3,25.4 и четвертый 25.2 элементы 2-2И-ИЛИ разрядов, второй элемент 2-2И-ИЛИ 26.2 второго разряда, Rp-вход 27 установки в исходное состояние средств функционального контроля соединен с входом элемента ИЛИ 7, выход которого соединен с инверсными Rp-входами триггеров 23.1-23.5. Управляющий L-вход

28соединен с входом элемента НЕ 6, выход которого соединен с первыми входами элементов И-НЕ 21.1-21.5 и 22.1-22.5. R-вход

29установки в О соединен с входом элемента ИЛИ 8, выход которого соединен с инверсными Ro-входами триггеров 23.1- 23.5. Информационный вход 30.1 предуста- нова первого разряда соединен с первым входом первой группы входов элемента 2- 2И-ИЛИ 18.1 и с вторым входом второй группы входов элемента 2-2И-ИЛИ 18.5. Вход 30.2 предустанова второго разряда соединен с первым входом первой группы входов элемента 2-2И-ИЛИ 18.2 и с вторым входом второй группы входов элемента 2- 2И-ИЛИ 18.1. Информационный вход 30.3 предустанова третьего разряда соединен с первым входом первой группы входов элемента 2-2И-ИЛИ 18.3 и с вторым входом- второй группы входов элемента 2-2И-ИЛИ

18.2.Информационный вход 30.4 предустанова четвертого разряда соединен с вторым входом элемента И-НЕ 22.4 и с вторым входом второй группы входов элемента 2-2И- ИЛИ 18.3. Вход 31 синхронизации соединен с входом элемента НЕ 10, выход которого соединен с инверсными входами элементов И 19 1-19.4. R- и Т-входы 32 и 33 соединены соот етственно с первым и вторым входами элемента И 11, выход которого соединен с прямым входом элемента И 19.1, с третьим входом элемента И 19.2, с третьим входом элемента И 19.3, с четвертым входом элемента И 12 и с первым входом элемента И 13. Т-вход 33 дополнительно соединен с третьим входом элемента И 14.

Инверсный выход элемента И/И-НЕ 17.5 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 18,5, с пер- вым входом элемента И 19.5 и с вторым ,

входом первой группы входов элемента 2 - 2И--ИЛИ 25.1. Прямой выход элемента И/И--НЕ 17.5 соединен с входом первой группы входов элемента 2-2И- ИЛИ 18.5, с первым входом элемента ИЛИ 24.5, с вторым входом элемента И 9 и с первым входом второй группы входов элемента 2-2И-ИЛИ 25.1. Выход элемента 2-2И-ИЛИ 18.5 соединен с вторым входом элемента И-НЕ 22.5, выход которого соединен с К-входом триггера 23,5 и с вторым входом элемента И-Н Е 21.5, выход которого соединен с -вхо- дом триггера 23.5, Выход элемента И 19.5 соединен со счетным входом триггера 23.5, прям ой выход которого соединен с первым входом первой группы входов элемента 2- 2И-ИЛИ 25.1. Выход Отсутствие отказа триггера 23.5 соединен с вторым входом элемента И 9 и с вторым входом элемента ИЛИ 24.5, выход которого соединен с первым входом элемента И 16.

Инверсный выход элемента И/И-НЕ 17.1 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 18.1, с первым входом второй группы входов элемента 2-2И-ИЛИ 20.1 и с вторым входом первой труппы входов элемента 2-2И-ИЛИ 25.2. Прямой выход элемента И/И-НЕ 17.1 соединен с вторым входом элемента ИЛИ 24.1, с вторым входом первой группы входов зле- мента 2-2И-ИЛИ 18.1, с вторым входом первой группы входов элемента 2-2И-ИЛИ 20.1 и с вторым входом первой группы входов элемента 2-2И-ИЛИ 25.2. Выход элемента 2-2И-ИЛИ 18.1 соединен с вторым входом элемента И-НЕ 22.1, выход которого соединен с К-входом триггера 23.1 и с вторым входом элемента И-НЕ 21,1, выход которого соединен с I-входом триггера 23.1, Выход элемента И 19.1 соединен с вторым входом элемента И 19.5 и с первым входом первой группы входов элемента 2-2И-ИЛИ 20.1, быход которого соединен со счетным входом триггера 23.1, прямой выход которого соединен с вторым входом второй группы входов элемента 2- 2И-ИЛИ 25.1 и с первым входом первой группы входов элемента 2- 2И-ИЛИ 25.2, Прямой выход элемента И/И-НЕ 17.1 дополнительно соединен с первым входом элемента И/И-НЕ 17.5. Выход Отсутствие отказа триггера 23.1 соединен с вторым входом элемента И/И-НЕ 17.5 и с первым входом элемента ИЛИ 24.1, выход которого соединен с вторым входом элемента И 16,

Инверсный выход элемента И/И-НЕ 17,2 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 18.2, с первым входом второй группы входов элемента 2-2И-ИЛИ 20.2 и с вторым входом первой

группы входов элемента 2 -2И ИЛИ 25.3. Прямой выход элемента И/И-НЕ 17,2 соединен с первым входом элемента И/И-НЕ

17.1,с вторым входом элемента ИЛИ 24.2, с вторым входом первой группы входов элемента 2-2И--ИЛИ 20.2и с первым входом второй группы входов элемента 2-2И-ИЛИ 25.3. Выход элемента 2-2И-ИЛИ 18.2 соединен с вторым входом элемента И-НЕ 22.2, выход

0 которого соединен с К-входом триггера 23.2 и с вторым оходом элемента И-НЕ 21.2, выход которого соединен с 1-оходсм тоигге- ра 23.2. Выход элементе И 19.2 соединен с вторым входом второй группы входов зле5 мента 2-2 И-ИЛ И 20,1 /, с первым входом первой группы входов элемента 2-2И-ИЛИ

20.2,выход которого соединен со счетным входом триггера 23,2, примой выход KOI opo- го соединен с вторым входом второй группы

0 входов элемента 2-2И-ИЛИ 25,2 и с первым входом первой группы входов элемента 2- 2И-ИЛИ 25.3. Выход Отсутсте ш отказа триггера 23,2 соединен с вторым входом элемента И/И-НЕ 17.1 и с первым входом

5 элемента ИЛИ 24.2, выход которого соединен с третьим входом элемента И 16. Выход элемента 2-2И-ИЛИ 26.2 соединен с вторым входом элемента И 19.2.

Инверсный аыхол элемента И/И-НЕ

0 7.3 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 26.2, с первым входом второй группы входов элемента 2-2И-ИЛИ 18.3, с первым входом второй группы Б одов элемента 2-2И-ИЛИ 20.3 м с

5 вторым входом первой группы входов элемента 2-2И-ИЛИ 25.4. Прямой выход элемента И/И-НЕ 17.3 соединен с первым входом элемента И/И-НЕ 17.2, с вторым входом первой группы входов элемента 20 2И-ИЛИ 18.3, с вторым входом первой группы входов элемента 2--2И-ИЛИ 20,3 и с первым входом второй группы входов элемента 2Ч2И-ИЛИ 25,4. Выход элемента 2- 2И-ИЛИ 18,3 соединен с вторым входом

5 элемента И-НЕ 22.3, выход которого соединен с К-входом триггера 23.3 и с вторым входом элемента И-НЕ 21,3, выход которого соединен с I-входом триггера 23.3, Выход элемента И 19,3 соединен с вторым входом

0 второй группы входов элемента 2-2И-ИЛИ

20.2и с первым аходом первой группы входов .элемента 2-2И-ИЛИ 20,3, выход которого соединен со счетным входом триггера 23.3, Инверсный выход триггера 23.3 соеди5 нен с вторым входом второй группы входов элемента 2-2И-ИЛИ 26.2, Прямой выход триггера 23.3 соединен с еторы входом второй группы входов элемента 2-2И-ИЛИ

25.3и с первым входом первой группы входов элемента 2-2И-ИЛИ 254. Выход Отсутстане отц-ьза триггера 23.3 соединен с вторые входом элемента И/И-НЕ 17.2 и с первым ВХОАСМ зл.емйпта 24.3, выход которого соединен с четвертым входом элемента И 16.

Выход элемента И 19.4 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 20.3 и со счетным входом триггера 23.4, инверсный выход которого соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 26.2, Выход элемента И-НЕ- 22.4 соединен с К-входом триггера 23.4 и с вторым входом элемента И-НЕ 21.4, выход которого соединен с l-входом триггера 23.4, прямой выход которого соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ 25.4. Выход Отсутствие отказа триггера 23.4 соединен с входами элемента И/И-НЕ 17.3, с вторым входом элемента ИЛИ 24.3 и с первым входом первой группы входов элемента 2-2И-ИЛИ 26.2.

Выходы элементов И 12 и 13 соединены соответственно с первым и вторым входами элемента ИЛИ 15, выход которого соединен с вторым входом элемента И 19.4. Выход элемента И 9 является выходом 34 Отсутствие частичного отказа счетчика. Выход элемента 2-2И-ИЛИ 25.1 является первым информационным выходом 35.1 счетчика и соединен с первыми входами элементов И 19.2, 19.3, с третьим входом элемента И 12, с вторым входом элемента И 13 и с вторым входом элемента И 14. Выход элемента 2- 2И-ИЛИ 25.2 является вторым информационный выходом 35.2 счетчика и соединен с вторым входом элемента И 19.3, с вторым входом элемента И 12.Выход элемента 2- 2И-ИЛИ 25.3 является третьим информационным выходом 35.3 счетчика и соединен с первым входом элемента И 12. Выход элемента 2-2И-ИЛИ 25.4 является четвертым информационным выходом 35.4 счетчика и соединен с третьим входом элемента И 13 и с первым входом элемента И 14, выход которого является выходом 36 Отсутствие полного отказа счетчика.

Триггер каждого разряда (фиг.З) содержит два элемента 2И-ИЛИ-НЕ 3.8 и 39, первый 40 и второй 41 элементы И, первый-четвертый элементы И-НЕ 42-45, первый элемент НЕ 46, третий элемент И 47, второй элемент НЕ 48, четвертый элемент И 49, элемент И/И-НЕ 50 и элемент 7И-ИЛИ- НЕ51.

Инверсный Ro-вход триггера каждого разряда соединен с первым входом элемента И-НЕ 45, с первым входом элемента И 40, с вторым входом первой и с первым входом второй групп входов элемента 2И-ИЛИ-НЕ

38 и с первым входом элемента И 49. 1-вход 53 триггера каждого разряда соединен с третьим входом второй группы входов элемента 2И-ИЛИ-НЕ 38, с вторым входом эле- 5 мента И/И-НЕ 50 и с вторым входом третьей группы входов элемента 7И-ИЛИ- НЕ 51. Синхровход 54 триггера каждого разряда соединен с четвертым входом второй группы входов элемента 2И-ИЛИ-НЕ 38, с 0 первым входом первой группы входов элемента 2И-ИЛИ-НЕ 39 и с входом элемента НЕ 46. К-вход 55 триггера каждого разряда соединен с вторым входом первой группы входов элемента 2И-ИЛИ-НЕ 39, с первым

5 входом элемента И/И-НЕ 50 и с первым входом четвертой группы входов элемента 7И-ИЛИ-НЕ 51. Инверсный S-вход 56 триггера каждого разряда соединен с вторым входом элемента И 49, с четвертым входом

0 первой и с первым входом второй групп входов элемента 2И-ИЛИ-НЕ 39, с третьим входом элемента И 41 и с третьим входом элемента И-НЕ 44.Нр-вход 57 триггера каждого разряда соединен с первым входом

5 седьмой группы входов элемента 7И-ИЛИ- НЕ51.

Выход элемента 2И-ИЛИ-НЕ 38 соединен с вторым входом элемента И 41 и с вторым входом второй группы входов эле0 мента 2И-ИЛИ-НЕ 39, выход которого соединен с вторым входом элемента И 40 и с первым входом первой группы входов элемента 2И-ИЛ И-НЕ 38. Выход элемента И 40 соедийен с первым входом элемента И-НЕ

5 42, с третьим входом второй, с вторым входом четвертой и с вторым входом пятой групп входов элемента 7И-ИЛИ-НЕ 51, Выход элемента И 41 соединен с вторым входом элемента И-НЕ 43, с четвертым входом.

0 первой, с первым входом третьей и с вторым входом шестой групп входов элемента 7И- ИЛИ-НЕ 51. Выход элемента НЕ 46 соединен с вторым входом элемента И-НЕ 42, с первым входом элемента И-НЕ 43, с треть5 им входом первой и с вторым входом второй групп входов элемента 7Й-ИЛ И-НЕ 51. Выход элемента И-НЕ 42 соединен с вторым входом элемента И-НЕ 44, с первым входом элемента И 47 и с первым входом элемента

0 И 41. Выход элемента И-НЕ 43 соединен с вторым входом элемента И-НЕ 45, с вторым входом элемента И 47 и с третьим входом элемента И 40. Выход элемента И 47 соединен с третьим входом третьей, с третьим

5 входом четвертой, с третьим входом пятой, с третьим входом шестой групп входов элемента 7И-ИЛ И-НЕ 51 и с входом элемента НЕ 48, выход которого соединен с вторым входом первой и с первым входом второй групп входов элемента 7И-ИЛИ-НЕ51. Выход элемента И 49 соединен с пятыми входами первой и второй и с четвертыми входами третьей-шестой ipynn входов элемента 7И-ИЛИ-НЕ 51. Инверсный выход элемента И/И-НЕ 50 соединен с пятыми входами третьей и четвертой групп входов элемента 7И-ИЛИ-НЕ 51. Прямой выход элемента И/И-НЕ 50 соединен с пятыми входами пятой и шестой групп входов элемента 7И- ИЛИ-НЕ 51, прямой выход которого соединен с вторым входом своей седьмой группы входов. Выход элемента И-НЕ 44 является прямым выходом триггера 58 каждого разряда и соединен с третьим входом первой группы входов элемента 2И- ИЛИ-НЕ 39, с третьим входом элемента И-НЕ 45, с первым входом первой и с первым входом пятой групп входов элемента 7И-ИЛИ-НЕ 51, Выход элемента И-НЕ 45 является инверсным выходом 59 триггера каждого разряда и соединен с вторым входом второй группы входов элемента 2И-ИЛИ-НЕ 38, с первым входом элемента И-НЕ 44, с четвертым входом второй и с первым входом шестой групп входов элемента 7И-ИЛИ-НЕ 51, инверсный выход которого является выходом 60 Отсутствие отказа триггера каждого разряда.

Разряды 1-4 являются основными разрядами двоично-десятичного счетчика, выполняющими заданный набор функций счетчика. Разряд 5 является резервным разрядом двоично-десятичного счетчика и предназначен для автоматического замещения одного из основных разрядов при его отказе.

Элемент НЕ б осуществляет инверсию сигнала на контрольном входе 28 разрешения предустанова счетчика и открывает или закрывает элементы И-НЕ 21.1-21.5 и 22.1- 22.5.

Элементы ИЛИ 7 и 8 принимают соответственно сигналы с входов 27 и 29 счетчика и согласуют их со стандартным значением логического логической 1 внутри интегральной микросхемы.

Элемент И 9 обобщает сигнал Отсутствие частичного отказа счетчика. В случае исправного состояния всех триггеров 23.1- 23.5 счетчика на его выходе присутствует сигнал логической 1. В случае отказа хотя бы одного из триггеров разрядов на его выходе формируется сигнал логического О.

Элемент НЕ 10 осуществляет инвертирование сигнала на синхровходе 31 счетчика и преобразует его реальное значение в номинальные значения логической 1 или логического О внутри интегральной микросхемы.

Элементы И 11 14 и ИЛИ 15 ррллич схему управления режимами рябого двоим но-десятичного счегчика

Элемент И 6 осуществляет обобщение

сигнала Отсутствие полного отказа .чет чика. При исправном состоянии всех тригге ров разрядов или при неисправном состоянии только одного из триггеров разрядов на его выходе присутствует сигнал

логической 1. При отказе двух и более триггеров разрядов на выходе элемента И 16 присутствует сигнал логического О .

Элементы И/И-НЕ 17 1-17.3 и 17.5 разрядов осуществляют выработку сигналов

настроечной функции, управляющей работоспособной структурой двоично-десятичного счетчика, в зависимости от исправного (неисправного) состояния триг- героа 23.1-23,5 разрядов.

Элементы 2-2И-ИЛИ 18.1-18.3, 18.5

осуществляют коммутацию сигналов с информационных входов 30.1-30.4 предустанова счетчика на I- и К-входы триггеров 23.1-23.5, в зависимости от исправного (неисправного) состояния соответствующих триггеров основных разрядов 1 -4.

Элементы И 19.1-19.5 совместно с элементами 2-2И-ИЛИ 20,1-20,3 осуществляют коммутацию синхросигналов,

поступающих на синхрозход 31 счетчика,и изменений на прямых выходах триггеров 23 1-23.5 на счетные входы триггеров последующих исправных разрядов.

Элементы И-НЕ 21.1-21.5 и 22.1-22.5

осуществляют подачу разнополярных сигналов на I- и К-зходы триггеров 23. i-23.5.

Триггеры 23,1-23.5 предназначены для хранения числа накопленных импульсов, поступивших насинхроаход31 счетчика при

разрешении их счета.

Элементы ИЛИ 24,1-24.3 и 24.5 осуществляют последовательное обобщение сигнала Отсутствие отказа в счетчике (при наличии двух отказавших триггеров на выходе соответствующего элемента ИЛИ вырабатывается сигнал логического О, который приводит к формированию сигнала логического О на зыходе элемента И 16). Элементы 2-2И-ИЛИ 25.1-25.4 осущесгвляют коммутацию сигналов с прямых выходов триггеров 23.1-23.5 на информационные выходы 35.1-35.4 счетчика в зависимости от исправного(неисправного) состояния соответствующего разряда

1-4.

Элемент 2-2И-ИЛИ 26.2 осуществляет установку счетчика в О после значения 1001 на выходах 35.1-35.4 и коммутирует этот сигнал установки в первый или второй

разряды в 3.fu.. ijL u работоспособного С Ч,Ь«-

Вход 27 предназначен для установки в исходно-., roi.ro ч/о гро,..тв Функционэль- ного контроля триггера каждого, включая и резервный, разряда.

Вход 28 разрешения предустанова предназначен для управления режимов его установки в предварительное состояние,отличное от нуля. При наличии на входе 28 сигнала низкого логического уровня счетчик устанавливается в состояние, соответствующее состояниям сигналов на входах 30.1- 30.4 счетчика.

Вход 29 предназначен для установки счетчика в О путем подачи на этот вход сигнала низкого логического уровня.

Входы 30.1-30.4 счетчика являются информационными входами предварительной установки его в состояние, отличное от нулевого состояния.

Входы 32 и 33, в совокупности с входом 28, являются входами, управляющими режимами работы счетчика. Счет импульсов производится при наличии на входах 28, 32 и 33 сигналов высокого логического уровня. Наличие этих сигналов на входах 28, 32 и 33 обеспечивает перенос импульсов в спед/ю- щий каскад двоично-десяти-жого счетчика через элемент И 14 и выход 37 счетчика.

Элементы 2И-ИЛИ-НЕ 3В и 39. И 4С и 41, НЕ 46 и И-НЕ 42 и 43 образ/ от схему вспомогательного триггера с в/одно логикой работы IK- или RS-триггера (фиг.З).

Элементы И-НЕ 44 и 45 образуют схепу основного триггера каждого разряда.

Элемент НЕ 46 предназначен для организации двухтактного режима работы универсального IK-триггера каждого разряда при наличии одного тактового входа 31. Кроме того, на выходе элемента НЕ 46 вырабатывается сигнал разрешения сравнения сигналов на противоположных плечах (выходах) основного и вспомогательного триггеров (фиг.З, т. А и Q, т. А и Q) в режиме хранения информации.

Элемент И 47 обеспечивает контроль наличия сигнала запрета работы основного триггера и формирует на своем выходе сигнал строба сравнения, задержанного относительно положительного фронта тактового сигнала на время не менее ЗТср (где Тср - время срабатывания одного логического элемента структуры триггера), т.е на время срабатывания элементов НЕ 46, И-НЕ 42 и 44, а также на время срабатывания самого элемента И 47 Особенностью элемента И 47 является то, что его время срабатывания должно быть не менее тср, г е если для остальных логических элементов структуры

универсального IK-триггера время срабатывание допускается не более ТСр, то для элемента И 47 оно должно быть не менее ТСр Данное ограничение можно выполнить при 5 разработке технологии изготовления мик росхемы.

Элемент НЕ 48 предназначен для формирования на своем выходе сигнала строба сравнения, задержанного на время 4Тср ог0 носительно отрицательного фронта тактового сигнала на С-входе 54 триггера.

Элемент И 49 предназначен для формирования сигнала запрета сравнения в пер- вой-и;естой группах входов элемента

5 7И-ИЛИ-НЕ 51 в момент асинхронной установи. IK-тр-лггера каждого разряда по его инверсным RQ- и S-входам (52 и 56 соответственно).

Элемент И/И -НЕ 50 на своих прямом и

0 инверсном выходах формирует сигнал функций I-K и IvK, которыми открываются или закрываются соответственно пятая и шестая, а тачже третья и четвертая группы входов элемента 7И-ИЛИ-НЕ 51 который

5 осуществляет на своих группах входов контроль правильности срабатывания всех ло- (ических элементов структуры IK-триггера. Б случае нарушения логики функционирования (отказ какого либо ло пческого элемен0 та структура триггера) на прямом выходе элемента 7И-ИЛИ- НЕ 51 Формируется высокий логический уровень сигнала который посредством своей обратной связи через второй зход седьмой группы входов осуще5 ствляагтзк называемый эффект самозахвата, т.е. устанавливается в устойчивое состояние логической Г на своем прямом выходе и логического О на инверсном выходе.

0В общем случае на входах элемента 7И

ИЛ4/1-НЕ 51 реализуется функционал отказа, который можно представить следующим аналитическим выражением

F (CIKRSM v(cTKRS)-Av(CIKRS)-A QV

5V(CIKRS A-O(CAQRSMCAQRS), (1)

где С, С - единичное и нулевое состояния

тактов ого сигнала на С-входе 54 IK-триггерз;

I, I - единичное и нулевое состояния

сигнала на i-входе 53 К-грипера,

0 К - единичное и нулевое состояния

сигнала на К-входе 55 IK-трипера;

R - единичное состояние сигнала нз инверсном Ro-входе 52 К-триггера,

S - единичное состояние сигнала на ин5 версно м S-входе 56 IK-три: г ера

А, А - единичное и нулевое состояния сигналов соответственно в i А и А (фиг 3);

Q, Q - состояния сигналов на прямом 58 и инверсном 59 выход.-) IK т рпп ера

Триггер каждого разряда в процессе функционирования двоично-десятичного счетчика работает следующим образом.

После включения питания на RF-ВХОД 57 триггера каждого разряда подается нулевой уровень сигнала для установки в исходное состояние средств функционального контроля, так как в силу случайного характера переходных процессов во время включения питания элемент 7И-ИЛИ-НЕ 51 с обратной связью (однофазный триггер) может установиться в единичное состояние на своем прямом выходе, соответствующее сигналу отказа любого из триггеров разрядов.

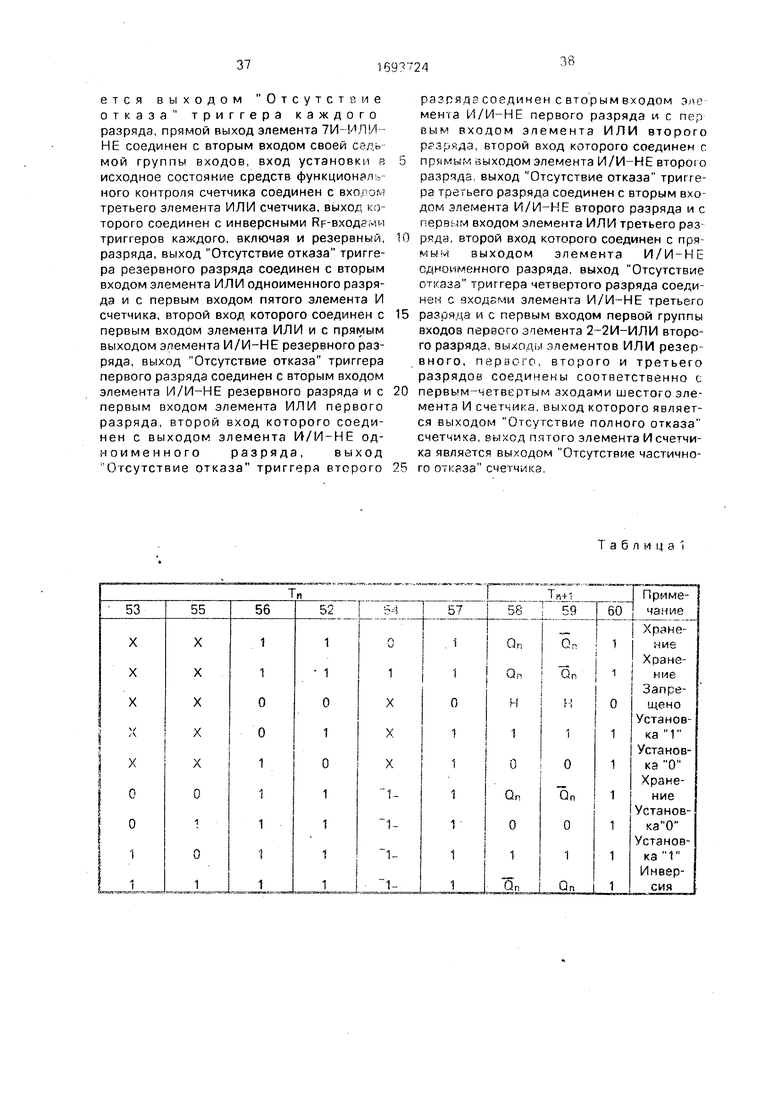

Далее при исправном состоянии всех логических элементов работа триггера каждого разряда подчиняется (соответствует) закону функционирования, приведенному в сокращенной табл. 1 переходов IK-трмггерз.

Из табл. 1 видно, что универсальный IK-триггер каждого разряда работает в двух режимах: асинхронном режиме («-триггера и в асинхронном режиме RS-триггерэ.

Рассмотрим подробнее каждый из режимов работы предлагаемого К-триггера каждого разряда и работу элементов функционального контроля-в ходе его функционирования.

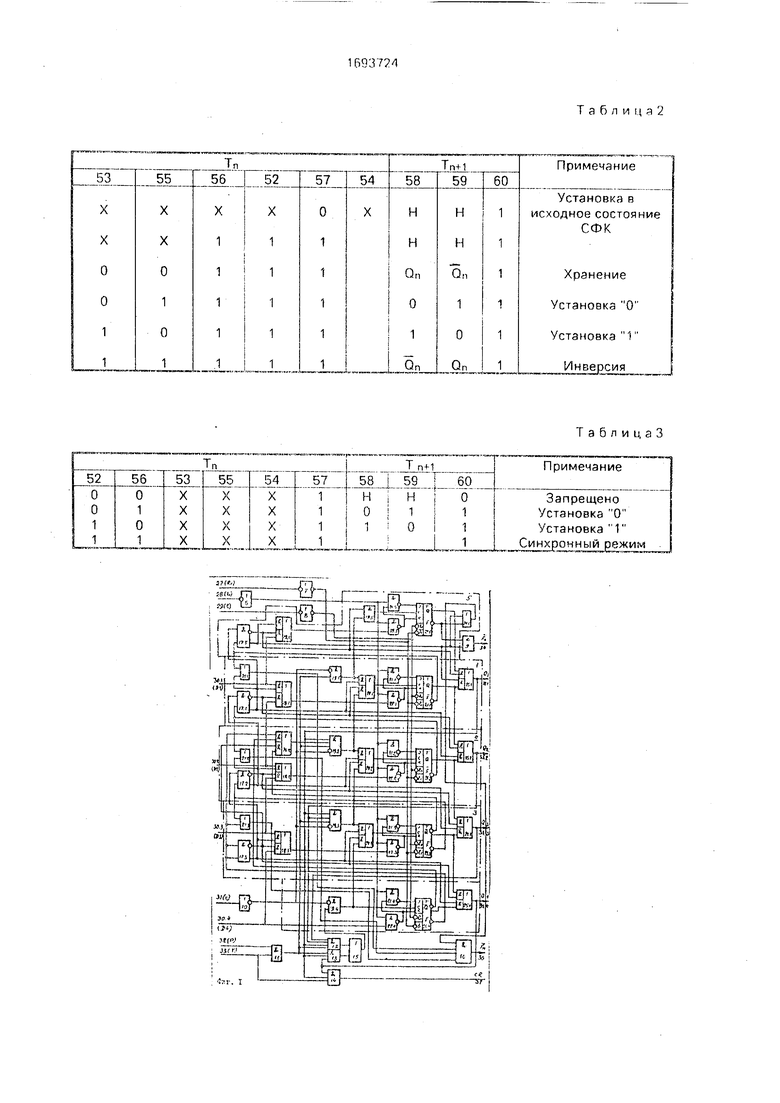

В синхронном режиме работы IK-триггер каждого разряда функционирует в соответствии с табл.2 переходов.

В табл. 1 и 2 приняты следующие сокращения:

53- -вход К-триггера;

55- К-зход К-триггера;

52 - инверсный Rrj-вход 1К-триггера;

56- инверсный S-вход IK-триггера;

57- RF-ВХОД установки в исходное состояние средств функционального контроля (СФК) 1К-триггера;

54- С-вход синхронизации (тактовый вход) 1К-триггера;

58- прямой выход К-триггера;

59 - инверсный выход 1К-триггера:

60 - выход Отсутствие отказа 1К-триг- гера;

X - информация низкого или высокого логического уровня на соответствующем входе триггера;

Qn, Qn - предыдущее состояние сигнала на прямом и инверсном выходе триггера соответственно;

Тп - момент времени до подачи отрицательного фронта тактового импульса:

Tn-ч-- момент времени после подачи отрицательного фронта тактового импульса;

Н - неопределенное состояние сигнапа на соответствующем выходе триггера;

I npppvo/i от РЫСПЮГо уровня -.иги ла к низкомуна С. 54 триггера

В процессе своего функционирлч нир первая ступень IK-триггера подчиняемся .а- кону, представленному следующими аналитическими выражениями:

С А 1 - IKC(RS /1KAC(RS), А - -FKC(RS)vlKAC(RS). (2)

где , I - единичное и нулевое соответствен- но состояния сигнапоо на 1-ьходе К-трцгге- ра;

К, К - соответственно единичное и нулевое состояния сигналов на К-входе 1К-триг- . гера;

С-единичное состояние сигнала ча тактовом входе IK-триггера:

R - единичное состояние сигнала на инверсном Ro-входе триггера;

S - единичное состояние сигнала на ин- версног/ S-входе триггера:

А, А - единичное состояние сигнала на выходах элементов И 40 и 41 IK-триггера.

За выполнением условия выражения (2) следят четвертая, пятая, шестая и третья группы входов элемента 7И-ИЛИ-НЕ 51.

В процессе своего функционирования вторая ступень IK-триггера (основной триггер) подчиняется закону, представленному следующими аналитическими выражениями:

0 1 .(3)

За выполнением условий выражения (3) следят первая и вторая группы входов элемента /V-И Л И-НЕ 51.

Функционал отказа любого из логических элементов первой ступени (вспомогательного триггера), реализованный Б предлагаемом техническом решении универсального IK-триггера каждого разряда 0 можно представить следующим аналитическим выражением

о

F IKC(RS)(R.S)-W|KAQ(RS)-CVtKAQ(RS)-C. (4)

5В случае нарушения условий функционирования, представленных в выражении (2), на прямом выходе элемента 7И-ИЛИ- НЕ 51 уже в момент срабатывания логических элементов первой ступени триггера 0 вырабатывается сигнал Отказ.

Функционал отказа любого из логических элементов второй ступени (основного триггера), реализованный в техническом решении предлагаемого IK-триггера каждого 5 разряда, можно представить выражением: F- Q-A-C«Q-A-C.(5)

В случае нарушения условий функционирования представленных а выражении (3), на прямом выходе элемента 7И-ИЛИНЕ 51 также внрабятываетг,ясигнал Отказ IK-триггера.

Рассмотрим последовательность срабатывания всех элементов предлагаемого IK- триггера в его четырех основных режимах синхронного функционирования: Хранение, Установка О, Установка 1 и Инверсия.

В режиме Хранение (табл. 2) с появлением положительного фронта тактового им- пульса на входе 54 триггера каждого разряда изменение состояния во вспомогательном триггере (первой ступени) не производится по следующим причинам. Примем, что предыдущее состояние 1К-триг- гера было единичным. Тогда при нулевых логических уровнях сигна ла и К-входах и единичных сигналах на RO-, S- и Rp-входэх закрыты вторые группы входов элементов 2И-ИЛИ-НЕ 38 и 39, а открыты первые группы входов этих элементов. Таким образом, срабатывание вспомогательного триггера не происходит.

Контроль правильности хранения предыдущего состояния в IK-триггере каждого разряда происходит следующим образом. В предлагаемом счетчике это осуществляется первой и второй группами входов злеме нгэ 7И-ИЛИ-НЕ 52 (фиг.З), на входы которых подаются сигналы с противоположных плеч основного и вспомогательного триггеров (т. А и Q, А и Q), фиг.З, а также сигнал разрешения проведения сравнения при тактовом сигнале С 0 с выхода элемента НЕ 46 и после допустимого времени срабатывания всех элементов основного и вспомогательного триггеров, равного 4Тср, с выхода элемента НЕ 48. При исправном функционировании всех основных логических элементов триггера каждого оазряда на их выходах 60 присутствует сигнал высокого логического уровня, и в противном случае триггер 51 формирует на своем инверсном выходе сигнал логического О.

При установке IK-триггера в состояние О (табл. 2) с появлением положительного фронта синхроимпульса на входе 54 производится запись нулевого состояния во вспомогательный триггер, и на время действия его высокого уровня в основном триггере хранится предыдущее состояние, так как с выхода элемента НЕ 46 на входы элементов И-НЕ 42 и 43 поступает нулевой логический уровень сигнала, блокирующий возможное воздействие переходных процессов в эле- ментах 2И-ИЛИ-НЕ 38 и 39, И 40 и 41 вспомогательного триггера на состояние основного триггера (элементы И-НЕ 44 и 45).

Срабатывание элементов вспомогательного триггера происходит следующим образом При предыдущем единичном состоянии триггера каждого разряда вторая группа элемента 2И- ИЛИ -НЕ 39 открыта, и на его выходе через время Тер установлен сигнал логического О. Первая и вторая группы входов элемента 2И-ИЛИ-НЕ 38 закрыты нулевыми сигналами с выхода элемента И-НЕ 45 и с выхода элемента 2И-ИЛИ-НЕ 39. Через время 2Тср с момента поступления положительного фронта синхроимпульса на вход 54 на выходах элементов И -НЕ 42 и 43 устанавливается высокий логический уровень сигнала. Таким образом, через время 2ТСр на входах элементов И 40 и 41 присутствуют следующие сигналы: элемент И 40 закрыт нулевым логическим уровнем сигнала с выхода элемента 2И- ИЛИ -НЕ 39: элемент И 41 пропускает на свой выход высокий логический уровень сигнала, так как на его входах присутствуют все высокие логические уровни сигналов (с выхода элемента И-НЕ 42,с выхода элемента 2И-1/1ЛИ-НЕ 38 и с S-входа триггера). Следовательно, через время ЗТср на выходе элемента И 40 (Уд, фиг.4) устанавливается сигнал нулевого логического уровня, а на выходе элемента И 41 (V/д, фиг 4) - высокий логический уровень сигнала.

Контроль правильности срабатывания основных элементов вспомогательного триггера осуществляют следующим обра зом. Через время несколько большее чем ЗТСр на выходе элемента И 47 появляется высокий логический уровень сигнала, который является стробом сравнение для третьей и четвертой групп входов элемента 7И-ИЛИ-НЕ 51, осуществляющих контроль, правильности срабатывания логических элементов вспомогательного триггера. Если в результате срабатывания основных логических элементов вспомогательного триггера выполнено условие

(RS)-G(IK)-A Г,(6)

где R - единичный уровень сигнала на ин- аерсном Ro-входе триггера:

Г - единичный уровень сигнала на инверсном S-входе триггера:

С - единичный уровень сигнала на С- входе триггера;

К - единичный уровень сигнала на К- входе триггера;

i - единичный уровень сигнала на 1-вхо- де триггера:

А-единичный уровень сигнала нэ выходе элемента И 41,

то первая ступень (элементы вспомогательного триггера) сработала правильно и на инверсном выходе элемента 7И-ИЛИ-НЕ

51 присутствует сигнал логической 1. При неправильном срабатывании (отказе какого-либо из основных элементов вспомогательного триггера) равенство (6) нарушается и элемент 7И-ИЛИ-НЕ 51 пропускает высокий логический уровень сигнала на свой прямой выход и устанавливается в устойчивое единичное состояние на прямом выходе и нулевое состояние на инверсном выходе, сигнализируя о возникновении отказа. На выходе 60 формируется нулевой логический уровень сигнала,

Функционирование и контроль правильности срабатывания основных логических элементов основного триггера в этом режиме производится следующим образом. По окончании действия сигнала на тактовом входе 54 и при правильном срабатывании элементов вспомогательного триггера на одном из элементов И-НЕ 42 и 43 формируется сигнал логического О, который устанавливает сигнал на выходе элемента И 47 в одноименное состояние, что приводит к формированию высокого логического уровня сигнала на выходе элемента НЕ 48, т.е. к формированию строба сравнения через время 4Тср с момента поступления отрицательного фронта тактового импульса. Одновременно с этим появление сигнала логического О на выходе одного из элементов И-НЕ 42 и 43, а для рассматриваемого примера сигнал логического О присутствует на выходе элемента И-НЕ 43, приводит к формированию единичного состояния на выходе элемента И-НЕ 45, что соответствует необходимому значению логического сигнала на выходе 59 (Q), т.е. режиму Установка 0, Через время 4ТСр заканчивается переходный процесс установки в нулевое состояние сигнала на выходе элемента И-НЕ 44. Таким образом, через время 4ТСр с момента поступления на вход 54 триггера каждого разряда отрицательного фронта синхросигнала в основном триггере (элементы И-НЕ 44 и 45) заканчиваются переходные процессы, и на первой и второй группах входов элемента 7И-ИЛИ-НЕ 51 производится контроль состояний сигналов на противоположных плечах вспомогательного и основного триггеров (сигнал Bj-очке А с сигналом на выходе 59 и в точке А с сигналом на выходе 58). При правильном срабатывании основного триггера на прямом выходе элемента 7И-ИЛИ--НЕ 51 присутствует сигнал логического О, в противнем случае сигнал логического О формируется на его инверсном выходе.

В режиме установки триггера каждого из разрядов в 1 (табл. 2) с приходом положительною фроту синхрпимпу/U Ca нл охпд 54 (фиг.4а) производится запись единично о состояния во вспомогательный триггер, и на время действия синхроимпульса основной

триггер переводится в режим хранения предыдущего состояния, так как с выхода элемента НЕ 46 на входы элементов И--НЕ 42 и 43 поступает нулевой логический уровень сигнала, блокирующий возможное воз0 действие переходных процессов в

логических элементах вспомогательного

триггера на состояние основного триггера.

Срабатывание логических элементов

вспомогательного триггера производится

5 следующим образом. При предыдущем нулевом состоянии IK-триггера на выходе элемента 2И-ИЛИ-НЕ 38 через время 2Тср формируется нулевой логический уровень сигнала, а на выходе элемента 2И-ИЛИ-НЕ

0 39 - высокий логический уровень сигнала. В результате этого элемент И 41 закрыт нулевым уровнем сигнала с выхода элемента 2И-ИЛИ-НЕ 38, а элемент И 40 - открыт, т.е. через время ЗТср при правильном сраба5 тывании элементов вспомогательного триггера в т. А устанавливается высокий логический уровень сигнала, а в т. А - низкий логический уровень сигнала.

Контроль правильности срабатывания

0 логических элементов вспомогательного триггера в этом режиме осуществляется следующим образом. Через такое же время ЗТСр на выходе элемента И 47 формируется высокий логический уровень сигнала, кото5 рый для пятой и шестой групп входов элемента 7И-ИЛИ-НЕ 51 является стробом сравнения. Если в результата срабатывания основных элементов вспомогательного триггера выполнено условие:

0((IK) A r, (7)

то элементы вспомогательного триггера срабатывают правильно, и на инверсном выходе элемента 7И-ИЛИ-НЕ 51 присутствует сигнал логической 1. При неправиль5 ном срабатывании (отказе) какого-либо из основных логических элементов вспомогательного триггера равенство(7) нарушается. и четвертая группа входов элемента 7И- ИЛИ-НЕ 51 пропускает на его прямой вы0 ход высокий логический уровень сигнала. что приводит к формированию устойчивого сигнала логического О на выходе 60 триггера любого из разрядов.

Функционирование и контроль пра5 вильности срабатывания основных логических элементов основного триггера в этом режиме производится следующим образом. По окончании действия сигнала на входе 54 (фиг.4, Vc) и при правильном срабатывании, вспомогательного триггера элементом И-НЕ 42 формируется сигнал логического О, который устанавливает выходы элементов И 47 и И -НЕ 44 о соответствующие состояния. На выходе элемента И 47 формируется c:ir- нал логического О, который приводит формированию на выходе элемента НЕ 48 сигнала строба сравнения. Этот сигнал формируется с задержкой на 4ТСр по отношению к моменту появления отрицательного фронта тактового импульса. На выходе эле- мента И-НЕ 44 также через время ЗТСр формируется сигнал логической 1, который через время 4Тср приводит к формированию сигнала логического О на выходе элемента И-НЕ 45. Таким образом, через время 4Тср на выходах 58 и 59 триггера формируются соответственно высокий и низкий логические уровни сигналов, что соответствует за- данному режиму функционирования IK-триггера, т.е. режиму Установка 1. Та- ким образом, через время 4ТСо с момента поступления на вход 54 IK-триггера отрицательного фронта тактового сигнала в основном триггере заканчиваются переходные процессы и на первой и второй группах вхо- дов элемента 7И-ИЛИ-НЕ 51 по стробу сравнения с выхода элемента HF 48 производится контроль правильности срабатывания его логических элементсв H-HF 44 м 5 При правильном срабатывании чэ инвер - ном выходе элемента 7И-ИЛИ-НЕ Ы остается сигнал логической 1, в противном случае - сигнал логического О.

В режиме инверсии состояния триггера каждого разряда (табл. 2), или, как его еще называют режиме счета, с приходом положительного фронта синхроимпульса на вход 54 IK-триггера производится изменение предыдущего состояния триггера на противоположное. При исправном функциониро- вании основных логических элементов IK-триггера должны быть выполнены следующие равенства :

(RS).()-A-Q-- 1,(8)

(RS}QKC E-Q r.(9)

Контроль правильности срабатываний основных логических элементов вспомогательного триггера з этом режиме о уществ- ляется пятой и шестой группами входов элемента 71/1-И Л И-НЕ 51 в момент времени ЗТСр с момента появления положительного фронта тактового импульса. Если равенства (8) и (9) не нарушаются, то сигнал Отказ на выходах 60 триггеров л юбого из разрядов не формируется. При возникновении откэза одного из основных логических элементов вспомогательного триггера равенства (3) или (9) нарушаются и на выходах 60 триггеров разрядов формируется сигнал Отказ.

Временная диаграмм работы в режиме Отказ приведена на фиг 36

Функционирование триггера каждого разряда в счетном режиме производите следующим образом. При подаче на вхо ы IK-триггера сигналов согласно табл. 2 п предыдущем единичном состоянии появ ю ние п.ол.сжительного фронта синхроимпульса нэ входе 54 приводит к срабатыванию элемента 2И-ИЛИ-НЕ 39, ча выходе KCVO- оого через время 2Тср формируется сигнал нулевого логического уровня. Через время ЗТср в т, А устанавливается одноименным логический уровень, а в точке А - высоки логичес - й уровень сигнала. Контроль гшз- вильности срабатывания этих элементов производится г.игнлгом с выхода элемента И 47, который формируется также через время ЗТСр. Если see логические элементы сработали правильно, го пятач гоуппа входов элемента 7И-ИЛИ-НЕ 51 не пропустит на его прямой выход сигнал, высокого логического урорня, в противном случае - будет сформировав сигнал Отказ тренера нз его выходе 50. Инверсия Hvieeoro состоя- ы/ триггера каждого разряда производится аналогичным образом, только в этом случае нулевой логический уровень угнана формируется Р т. А и контроль прз.--пьнзс гм срабатывания основных лсг ческих тов вспомогательного трип ера прсм зодит- сс- шестой группой ечодог- элемента И- /|Л1/1- НЕ 51 Коигоол правильности срабатывания основных логических монгол основного тоиггерп апатичен раное приведенном режимам рдбогь. К-три,гер-: при его стс носке R О и. 1

таким ооразом. no scex синхронных режимах функционирований К- триггерз каждого разряда осущеитзляетоя постоя г1ьч/| контроль за достоверностью срабатывания его основных ло ических элементов. В случае нарушения (отказа) какого- либо из основных логических элементов IK-триггерз любого из разрядов на соответствующем выходе 60 формируется сигнал (нулевой потенциал сигнала отсутствие отказа), который сигнализируемо не- дост верной работе соответствующего триггера разряда.

В асинхронном режиме функционирования iK-трчггера, при vnrjasneHin его состоянием сигналами на RQ- и S-входах. срабатывание его погических элементов подчиняется закону функционирования RS- , приведенному в табл 3 переходов.

Контроль правильности срабатывания логических элементов основного и вспомогательного триггеров в 3Tov pev;n - e полно

стыо перекрывается рг-.чт. пямнмм KOMI ролом режима хранения для синхронной ря богы IК-триггера а -акже режимами его установки в О и

„., При появлеиии нулевого потенциала на RQ- или S-входе триггера на рыходе элемента И 49 формируется запрещающий сигнал, который блокирует первую местую группы сходов элемента 7И -МЛИ -HF 51 на момент действия нулевого погенцитч на PC- ипи S-входе триггера любого из Разрядов Далее осуществляется контроль состояний сигналов на противоположных плечах основного и вспомогательного триггеров (т Л с выходом 59 и т Ас выходом 58 триггеоа)

Таким образом в процессе подсчета импульсов каждого разряда непрерывно контролируется на правильность срабатывания и, D случае отказа какого-либо из основных логических элементов своей структуры, формирует на своем выходе Отсутствие отказа сигнал низкого логическо го уровня

Двоично-десятичный счетчик содержащий в каждом разряде описанный триггер работает следующим обратом

Для установки двоично-десятичного счетчика в нулевое состояние на вход 29 (фиг 1) счетчика н/леной чо-ино ский сип зп При этом вг - pi/in ерь 3 i- 3 5 разрядов yc Si dbPHL-dioii. ь sy/iei-oe toe ояние

ДЛЯ УСТ.ЧНОПЧ1/ г ИЧНО-ЧС ЯТ ИМ (. чСТЧИКП D 1h.it С I ИЧИ Х 01 Г ТС ЗОГО

р j вход 28 p ljpc и ры т гфедусга1.о )Д г.од степ сигнал ron/ьес1 jro 0 о гч С2 14 33 состояния С /г,чпог j/oiyr Lin о любыми ь лом Cj y1 biv.N Osi ы /1 iiL / i i 21 Ь и 22 1-2 Ь открываются с. гтмсвы та элемента НГ С Состояние : мчалоо г доа 30 1 30 rj cs-seflHK ) элс.нгы И- /ШИ 1Ь 1- &3 . НГ 41 I 2 л -/ 2 1 22 4 п ода ют с 1 на I- и К-йхоцы тиите роз 23 1-234 коюрьк ЛРЛ-и.ают состоч иия, ИДЗНТИЧНЫР с входным одом при мостугпенип положа только О г рон is тактового ичпульса на вход 3 синхоонизации счетчика

При исправном состоянии ipnr ерпв ,3 1-234 основных разрядов устройства в рржиг/е счета на ил выходах 60 прис тств ют сигнала лоп чгскги 1 В этом спучае единичными разре1юющимм сигналами с выходов элемснтгв И/И НЕ 171 17 Ь открыты следующие ло ические элеизиты иметч ка переые ipynnbi входов элегюн-тов г 2И-ИЛИ 18 1 183 и 18 5 ,э пходоз элементов 2-2И ИЬИ 201 П 3 ыгорые группы входов эпемчнгов 2 ИЛИ 25 Опем«нт И 1° сч 3a pbiTHv ирым логичог иим ч рпннсм мгнялл г инг,,ч ного выхода ЭЛРМРНТЯ И/И HI 1 7 ri

Счет импульсов в счетчике ся по следующей логической ветви го счгт

нот о входа 31 счетчика через элем-от i.1 И 19 1, первую группу входоь элемрнгр п 2И-ИЛИ 20 1 - на счетный вход rpnireoa 23 1, через вторую группу входов злг егчз 2-2И-ИЛИ 25 1 - на информациончы i ыыход 35 1 счетчика С прихсдо второю им r,v,ibca измэнсние вь-хсда гоиггерэ 23 1 через вторую группу входов элемента 2 2И- ИЛИ 25 1, племент И (0 первую группу входов элемента -2И 0 2 - m счетный вход триггера 23 2 и через вторую tnyii- пу входов элемента 2 , 5 2 на информационны, выход 352 счетчисз С приходом очередного имп / 1ьс ЭЛР ы И i93 и 132 закрыты ну -еяым -„.сгнием

сигнала на ПОРТОМ тритеоа 23 1 и с/ едоеагольпо о единичное си ;т 1ячиеусгь навдивается только триггер 23 1 ipr калэле мент И 19 1 jTKObiT Четвертый имчульС устанавливает в единичное сосктянис риггер 23 3 и Р н/лсво состояние три гзры 2 i и 23 2 Триггер 23 4 установлен в едини«чое состояние при предыдущем единичном со- отопнии триггеоов 23 1-23 3 так как только з открывается элемент 194

Г.осле состоя ия двоиччо десятичною с iM-iiVc- ра но с 1001 отчрывае С элемент l/l 14 ivH-хет горедать РГ -зыиду / с етч/кч uiiMMj,v переносе Б сгярчл t;sc 1,1 ,v:tf,,ооазрядього цьо-1чно

доОЯ1И1 о.з ч(- (Ичз С прилодом ,0io ьга д онЧчо- эсяти ный счетчик устанавливает в сосгочние 0000 Это обеспечивается гем что j eMeHi Vi 4s 1 ui крь r r гя , рохохдеьия ,ca на счетный

tixoo tepa 3 1, элемент i/ 2 - закрыт сигна р; с выхода элемонгз 2 2И-ИЛИ 4.6 2 эяег-.е, И 19 3 - закрыт нулевым сигналом с триггеоа 23 2 через элемент 2 2И-ИЛ, 252 и И 19 4 - огкрыг

для прохождения оинхроимтупьсо из счет- вход фиггера 23 4

Состояние влодов и выходов счетчика при счегр о1 0 до 9 показано на сременной диа1рамме раоо.ы счетчика (Фиг 2}

0Пои неисправном состоянии одного из

основных разрядов 1 4 на соответствующем выход0 триггера Отсутствие отказа формируется с /гнал логического О

Рассмотрим г.рикцип сохранения рабо5 тиспособ.юом сиегчика ,-,а примерах когда произошел ОТКРЗ тритеоз первого и третьего рззрчдов

При л,аэс триггера 23 1 п&овсго разря да на ого выходе Отсутствие отказа фор- мируе ся ну есой потенциал и данный

разряд исключается из режима функционирования предлагаемого двоично-деся1ично- го счетчика. Это производится следующим образом.

Нулевой потенциал на выходе Отсутст- вне отказа триггера 23.1 приводит к смене состояний сигналов на прямом и инверсном выходах элемента И/И-НЕ 17.5, что, в свою очередь, приведет к открытию второй и закрытию первой групп входов элемента 2 2И-ИЛ1/1 18.5, к открытию первой и закрытию второй групп входов элемента 2- 2И-ИЛИ 25.1, а также к открытию элемента И 19.5. Таким образом, при установке счетчика в состояние, отличное от нулевого, сиг- нал с входа 30.1 поступает через вторую группу входов элемента 2-2И-ИЛИ 18.5 на вход элемента И-НЕ 22.5, а значение состояния сигнала на выходе триггера 23.5 через первую группу входов элемента 2-2И-ИЛИ 25.1 - на информационный выход 35.1 счетчика. Выход триггера 23.1 в этом случае отключен от выхода 35.1 счетчика закрытой второй группой входов элемента 2-2И-ИЛИ 25.1.

Подсчет импульсов в этом случае производится по следующей логической ветви предлагаемого двоично-десятичного счетчика: с синхровхода 31 счетчика через элемент НЕ 10, элементы И 19.1 и 19.5 нд счетный вход триггера 23.5. Значение состояний сигналов (и их изменения) на прямом выходе триггера 23.5 через первую группу входов элемента 2-2И-ИЛИ 25.1 - на информационный выход 35.1 счетчика и через элемент И 19.2, первую группу входов элемента 2-2И-ИЛИ 20.2 - на счетный вход триггера 23.2. Состояние сигнала на выходе триггера 23.2 (и его изменения) через вторую группу входов элемента 2-2И-ИЛ И 25.2 поступает на информационный выход 35.2 счетчика и через элемент И 19.3, первую группу входов элемента 2-214-ИЛ И 20.3 - на счетный вход триггера 23.3. Состояние сигнала (и его изменения) на выходе триггера 23.3 через вторую группу входов элемента 2-2И-ИЛИ 25.3 поступает на информационный выход 35.3 счетчика и через элементы И 12, ИЛИ 15 и И 19.4 - на счетный вход триггера 23.4, состояние сигнала на прямом выходе которого через вторую группу входов элемента 2-2И-ИЛИ 25.4 поступает на выход 35.4 счетчика. Таким образом, в результате формирования нулевого потенциала на выходе Отсутствие отказа триггера 23.1 происходит исключение его из работоспособной структуры предлагаемого двоично-десятичного счетчика, как в режиме его предустанова, так и в режиме подсчета импульсов,

При отказе триггера 23.3 на его выходе Отсутствие отказа также формируется нулевой логический уровень сигнала, который приводит к изменению состояний сигналов на прямых и инверсных выходах элементов И/И-НЕ 17.2, 17.1 и 17.5. Единичными потенциалами с их инверсных выходов открываются следующие логические элементы счетчика: вторая группа входов элемента 2- 2И-ИЛИ 18.5 (разрешается прохождение сигнала с входа 30.1 счетчика на I- и К-входы триггера 23.5), элемент И 19.5 (разрешается прохождение синхроимпульсов на счетный вход триггера 23.5), первая группа входов элемента 2--2И-ИЛИ 25.1 (разрешается прохождение сигнала с выхода триггера 23.5 на информационный выход 35.1 счетчика), вторая группа входов элемента 2-2И-ИЛЙ 18.1 (разрешается прохождение сигнала с входа

30.2на I- и К-входы триггера 23.1), вторая группа входов элемента 2-2И-ИЛИ 20.1 (разрешается прохождение синхроимпульсов с выхода элемента И 19.2 на счетный вход триггера 23.1), первая группа входов элемента 2-2И-ИЛИ 25.2 (разрешается прохождение сигнала с выхода триггера 23.1 на информационный выход 35.2 счетчика), вторая группа входов элемента 2-2И-ИЛИ 18.2 (разрешается прохождение сигнала с входа

30.3счетчика на I- и К-входы триггера 23.2), вторая группа входов элемента 2-2И-ИЛИ 20.2 (разрешается прохождение синхроимпульса -с- выхода элемента И 19.3 на счетный вход триггера 23.2), первая группа входов элемента 2-2И-ИЛИ 25.3 (разрешается прохождение сигнала с выхода триггера 23.2 на информационный выход 35.3 счетчика). Состояние логических элементов четвертого разряда остается прежним. Таким образом,- при формировании сигнала логического О на выходе Отсутствие отказа триггера 23,3, логическая структура двоично-десятичного счетчика перестраивается на такую работоспособную структуру, при которой триггер 23.3 вытесняется из режима функционирования.

Замена отказавших триггеров 23.2 и

23.4производится аналогичным образом.

рассматриваемом первом режиме (Отказ триггера 23.1) на выходе 34 Отсутствие частичного отказа счетчика формируется сигнал логического О, так как элемент И 9 закрывается нулевым потенциалом с выхода Отсутствие отказа триггера 23.1 через элемент И-И-Н Е 17.5. В случае отказа триггера 23.3 элемент И 9 также закрыт ну-, левым потенциалом с выхода триггера 23.3 через элементы И/И-НЕ 17.2, 17.1 и 17.5.

При отказе двух триггеров, например первого и третьего разряда одновременно.

При отказе двух триггеров, например первого и третьего разряда одновременно, кроме формирования нулевого сигнала, на выходе 34 счетчика формируется и нулевой сигнал на выходе 36 Отсутствие полного отказа счетчика, сигнализируя о том, что резерв исчерпан и устройство неработоспособно. Формирование нулевого сигнала на выходе 36 устройства производится следующим образом.

Так как на выходе (прямом) элемента И/И-НЕ 17.1 нулевой логический уровень сигнала, а на выходе Отсутствие отказа триггера 23.1 сформирован также нулевой уровень сигнала, то на выходе элемента ИЛИ 24.1 формируется также нулевой логический уровень сигнала, который, поступая на второй вход элемента И 16, закрывает его.

Таким образом, в предлагаемом двоично-десятичном счетчике осуществляется автоматическая реконфигурация его работоспособной структуры при отказе одного из основных разрядов, что создает возможность обеспечения как непрерывного контроля правильности его функционирования, так и автоматическое восстановление работоспособности.

Формула изобретения Двоично-десятичный счетчик, содержащий два элемента НЕ, два элемента ИЛИ, четыре элемента И, основные и резервный разряды, резервный разряд содержит триггер, элемент И/И-НЕ элемент 2-2И-ИЛИ, элемент И и два элемента И-НЕ, первый разряд содержит триггер, элемент И/И-НЕ, три элемента 2-2И-ИЛИ, элемент И и два элемента И-НЕ, второй разряд - триггер, элемент И/И-НЕ, четыре элемента 2-2И- ИЛИ, элемент И и два элемента И-НЕ, третий разряд - триггер, элемент И/И-НЕ, три элемента 2--2И-ИЛИ, элемент И и два элемента И-НЕ, четвертый разряд - триггер, элемент И, элемент 2-2И-ИЛИ и два элемента И-НЕ, контрольный L-вход счетчика соединен с входом первого элемента НЕ счетчика, выход которого соединен с первыми входами первого и второго элементов И-НЕ каждого, включая и резервный, разряда, вход установки в О счетчика соединен с входом первого элемента ИЛИ счетчика, выход которого соединен с RO-BXO- дом триггера каждого, включая и резервный, разряда, синхровход счегчика соединен с входом второго элемента НЕ счетчика, выход которого соединен с инверсными входами элементов И первого-чет- вертого разрядов, R-вход счетчика соединен с первым входом первого элемента И счетчика, второй вход которого соединен с Твходом счетчика и с третьим входом четвертого элемента И счетчика, выход первого элемента И-НЕ каждого, включая и резервный, разряда соединен с l-входом триггера

одноименного разряда, выход второго элемента И-НЕ каждого, включая и резервный, разряда соединен с вторым входом первого элемента И-НЕ и с К-входом триггера одноименного разряда, выход первого элемента

0 И счетчика соединен с первым входом третьего и с четвертым входом второго элементов И счетчика, с прямым входом элемента И первого разряда, с третьим входом элемента И второго разряда и с третьим

5 входом элемента И третьего разряда, инверсный выход элемента И/И-НЕ резервного разряда соединен с первым входом второй группы входов элемента 2-2И-ИЛИ, с первым входом элемента И одноименного и с

0 вторым входом первой группы входов третьего элемента 2-2И-ИЛИ первого разрядов, прямой выход элемента И/И-НЕ резервного разряда соединен с входом первой группы входов элеэмента 2-2И-ИЛИ

5 одноименного и с первым входом второй группы входов третьего элемента 2-2И- ИЛИ первого разрядов, информационный вход предустанова первого разряда соединен с первым входом первой группы входов

0 первого элемента 2-2И-ИЛИ одноименного и с вторым входом второй группы входов элемента 2-2И-ИЛИ резервного разряда, выход которого соединен с вторым входом второго элемента И-НЕ одноименного раз5 ряда, выход элемента И резервного разряда соединен со счетным входом триггера одноименного разряда, прямой выход которого соединен с первым входом первой группы входов третьего элемента 2-2И-ИЛИ пер0 вого разряда, инверсный выход элемента И/И-НЕ первого разряда соединен с первым входом второй группы входов первого, с первым входом второй группы входов второго элементов 2-2И-ИЛИ одноименного и

5 с вторым входом первой группы входов четвёртого элемента 2- 2И-ИЛИ второго разряда, прямой выход элемента И/И-НЕ первого разряда соединен с первым входом элемента И/И-НЕ резервного разряда, с

0 вторым входом первой группы входов первого, с вторым входом первой группы входов второго элементов 2-2И-ИЛИ одноименного и с первым входом второй группы входов четвертого элемента 2-2И5 ИЛИ второго разряда, информационный вход предустанова второго разряда соединен с первым входом первой группы входов второго элемента 2-2И-ИЛИ одноименного разряда и с вторым входом второй группы входов первого элемента 2-2И-ИЛИ первого разряда , выход которого соединен с вторым входом второго элемента И-НЕ одноименного разряда, выход элемента И первого разряда соединен с первым входом первой группы входов вто- рого элемента 2-2И-ИЛИ одноименного и с вторым входом элемента И резервного разряда , выход второго элемента 2-2И-ИЛИ первого разряда соединен со счетным входом триггера одноименного разряда, пря- мой выход которого соединен с вторым входом вт орой группы входов третьего элемента 2-2И-ИЛИ одноименного и с первым входом первой группы входов четвертого элемента 2-2И-ИЛИ второго разряда, ин- версный выход элемента И/И-НЕ второго разряда соединен с первым входом второй группы входов второго элемента 2-2И- ИЛИ, с первым входом второй группы входов третьего элемента 2-2И-ИЛИ одноименного и с вторым входом первой группы входов третьего элемента 2-2И- ИЛИ третьего разряда, прямой выход элемента И/И-НЕ второго разряда соединен с первым входом элемента И/И-НЕ первого разряда, с вторым входом первой группы входов второго, с вторым входом первой группы входов третьего элементов 2-2И- ИЛИ второго разряда и с первым входом второй группы входов третьего элемента 2- 2И-ИЛИ третьего разряда, выход второго элемента 2-2И-ИЛ.И второго разряда соединен с вторым входом второго элемента И-НЕ одноименного разряда, выход первого элемента 2-2И-ИЛИ второго разряда со- единен с вторым входом элемента И одноименного разряда, выход которого соединен с первым входом первой группы входов третьего элемента 2-2И-ИЛИ одноименного и с вторым входом второй группы входов второго элемента 2-2И-ИЛИ первого разряда, выход третьего элемента 2-2И-ИЛИ второго разряда соединен со счетным входом триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов четвертого элемента 2-2И-ИЛИ одноименного и с первым входом первой группы входов третьего элемента 2-2И-ИЛИ третьего разряда, инверсный выход элемента И/И-НЕ третьего разряда соединен с первым входом второй группы входов первого элемента 2-2И-ИЛИ второго разряда, с первым входом второй группы входов первого, с первым входом второй группы входов вто- рого элементов 2-2И-ИЛИ третьего разряда и с вторым входом первой группы входов элемента 2-2И-ИЛИ четвертого разряда, прямой выход элемента И/И-НЕ

третьего разряда соединен с первым входом элемента И/И-НЕ второго разряда, с вторым входом первой группы входов первого, с вторым входом первой группы входов второго элементов 2-2И-ИЛИ третьего разряда и с первым входом второй группы входов элемента 2-2И-ИЛИ четвертого разряда, информационный вход предустанова третьего разряда соединен с вторым входом второй группы входов второго элемента 2-2И-ИЛИ второго разряда и с первым входом первой группы входов первого элемента 2-2И-ИЛИ третьего разряда, информационный вход предустанова четвертого разряда соединен с вторым входом второго элемента И-НЕ одноименного разряда и с вторым входом второй группы входов первого элемента 2-2И-ИЛИ третьего разряда, выход которого соединен с вторым входом второго элемента И-НЕ третьего разряда, выход элемента И третьего разряда соединен с первым входом первой группы входов второго элемента 2-2И-ИЛИ третьего разряда и с вторым входом второй группы входов третьего элемента 2-2И-ИЛИ второго разряда, выход второго элемента 2-2И-ИЛИ третьего разряда соединен со счетным входом триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов третьего элемента 2-2И-ИЛИ третьего и с первым входом первой группы входов

зтемента 2-2И-ИЛИ четвертого разряда, инверсный выход триггера третьего разряда соединен с вторым входом второй группы входов первого элемента 2-2И-ИЛИ второго разряда, выход элемента И четвертого разряда соединен со счетным входом триггера одноименного разряда и с вторым входом второй группы входов второго элемента 2-2И-ИЛИ третьего разряда, инверсный выход триггера четвертого разряда соединен с вторым входом первой группы входов первого элемента 2-2И-И Л И второго разряда, прямой выход триггера четвертого разряда соединен с вторым входом второй группы входов элемента 2-2И-ИЛ И одноименного разряда , выход третьего элемента 2-2И-ИЛИ первого разряда является первым информационным выходом счетчика и соединен с первыми входами элементов И второго и третьего разрядов, с третьим входом второго, с вторыми входами третьего и четвертого элементов И счетчика, выход четвертого элемента 2-2И-ИЛИ второго разряда является вторым информационным выходом счетчика и соединен с вторыми входами элемента И третьего разряда и второго элемента И счетчика, выход третьего элемента 2-2И-ИЛИ третьего разряда, является третьим информационным выходом счетчмкаисоединенспервымвходом второго элемента И счетчика, выход которого соединен с первым входом второго злемента ИЛИ счетчика, второй вход которого соединен с выходом третьего элемента И счетчика, выход элемента 2-2И-ИЛИ четвертого разряда является четвертым информационным выходом счетчика и соединен с третьим входом третьего элемента И счетчика и с первым входом четвертого элемента И счетчика, выход которого является выходом переноса максимального значения счетчика, выход второго элемента ИЛИ счетчика соединен с прямым входом элемента И четвертого разряда, отличающийся тем, что, с целью повышения достоверности функционирования и автоматизации процесса восстановления работоспособности, он дополнительно содержит пятый и шестой элементы И, третий элемент ИЛИ, а каждый, кроме четвертого, разряд дополнительно содержит элемент ИЛИ, триггер каждого, включая и резервный, разряда в своей структуре содержит два элемента 2-2И- ИЛИ, четыре элемента И, два элемента НЕ, четыре элемента И-НЕ, элемент И/И-НЕ и элемент 7И-ИЛИ-НЕ, причем В0-вход триггера каждого разряда соединен с первым входом четвертого элемента И-НЕ, с первым входом первого элемента И, с вторым входом первой и с первым входом второй групп входов первого элемента 2И-ИЛИ- НЕ, 1-вход триггера каждого разряда соединен с третьим входом второй группы входов первого элемента 2И-ИЛИ-НЕ, с вторым входом злемента И/И-НЕ и с вторым входом третьей группы входов элемента 7И--ИЛ И-НЕ, инверсный К0-вход триггера каждого разряда дополнительно соединен с первым входом четвертого элемента И, вход синхронизации триггера каждого разряда соединен с четвертым входом второй группы входов первого и с первым входом первой группы входов второго элементов 2И-ИЛИ-НЕ, а также с входом первого элемента НЕ, К-вход триггера каждого разряда соединен с вторым входом первой группы входов второго элемента 2И-ИЛИ- НЕ, с первым входом элемента И/И-НЕ и с первым входом четвертой группы входов элемента 7И-ИЛИ-НЕ, инверсный S-вход триггера каждого разряда соединен с четвертым входом первой и с первым входом второй групп входов второго элемента 2И- ИЛИ-НЕ, с вторым входом четвертого элемента И, с третьими входами второго элемента И и третьего элемента И-НЕ, RF- вход установки в исходное состояние средств функционального контроля триггера каждого разряда соединен с первым входом седьмой группы входов элемента

7И- ИЛИ- НЕ, выход перпого элемента 2И ИЛИ- НЕ соединено вторым входом второго элемента И и с вторым входом второй группы входов второго элемента 2И-ИЛИ- НЕ

выход которого соединен с вторым входом первого элемента И и с первым входом первой группы входов первого элемента 2И- ИЛИ-НЕ, выход первого элемента И соединен с первым входом первого элемента И-НЕ, с третьим входом второй, с вторым входом четвертой и с вторым входом пятой групп входов элемента 7И-ИЛИ-НЕ, выход первого элемента НЕ соединен с вторым входом первого и с первым входом второго

элементов И-НЕ, с третьим входом первой и с вторым входом второй групп входов элемента 7И-ИЛИ-НЕ, выход второго элемента И соединен с вторым входом второго элемента И-НЕ, с четвертым входом первой, с первым входом третьей и с вторым входом шестой групп входов элемента 7И- ИЛИ-НЕ, выход первого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ, с первым входом второго и с первым

входом третьего элемента И, выход второго элемента И-НЕ соединен с вторыми входами четвертого элемента И-НЕ и третьего элемента И и с третьим входом первого элемента И, выход третьего элемента И

соединен с входом второго элемента НЕ, с третьим входом третьей-шестой групп входов элемента 7И-ИЛИ-НЕ, выход второго элемента НЕ соединен с вторым входом первой и с первым входом второй групп входов элемента 7И-ИЛИ-НЕ, выход четвертого элемента И соединен с пятыми входами первой и второй, с четвертыми входами третьей-шестой групп входов элемента 7И-ИЛИ-НЕ, инверсный выход

элемента И/И-НЕ соединен с пятыми входами третьей и четвертой групп входов элемента 7И-ИЛИ-НЕ, прямой выход элемента И/И-НЕ соединен с пятыми входами пятой и шестой групп входов элемента 7И-ИЛИНЕ, выход третьего элемента И-НЕ являет- cff прямым выходом триггера каждого разряда и соединен с третьим входом четвертого элемента И-НЕ, с третьим входом первой группы входов второго элемента

0 2И-ИЛИ-НЕ, с первым входом первой и пятой групп входов элемента 7И-ИЛИ-НЕ, выход четвертого элемента И-НЕ является инверсным выходом триггера каждого разряда и соединен с первым входом третьего