Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных комплексах для связи ЦВМ.

Целью изобретения является повышение быстродействия.

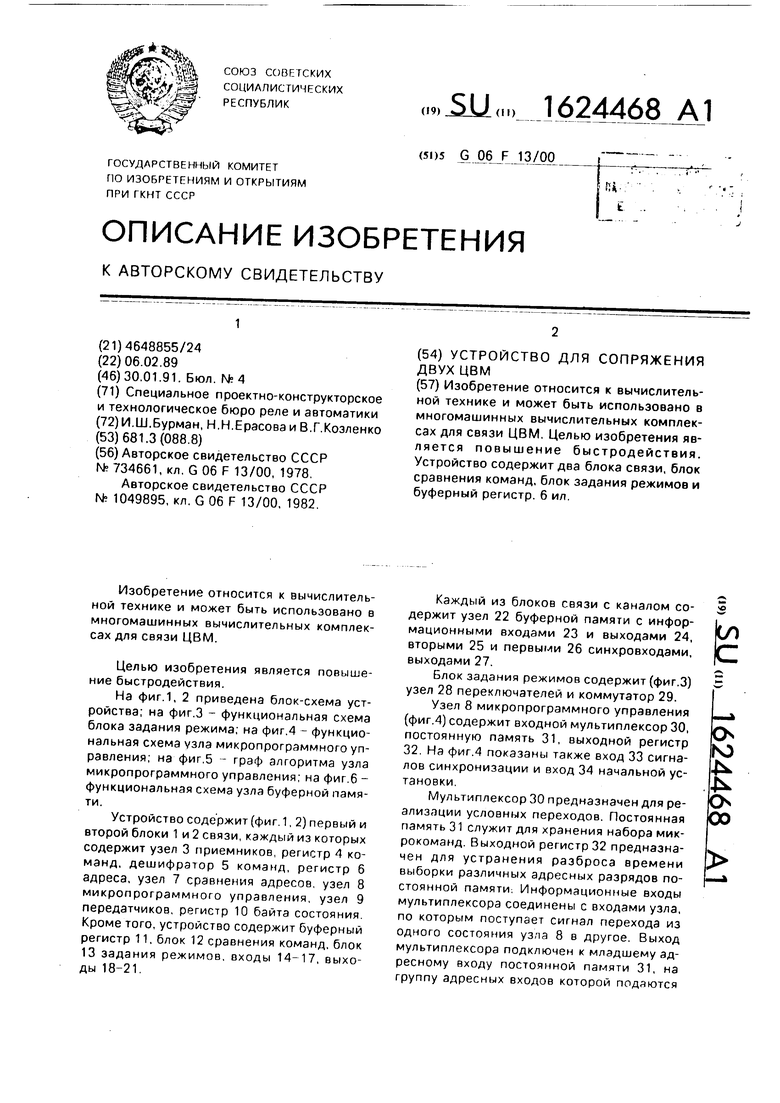

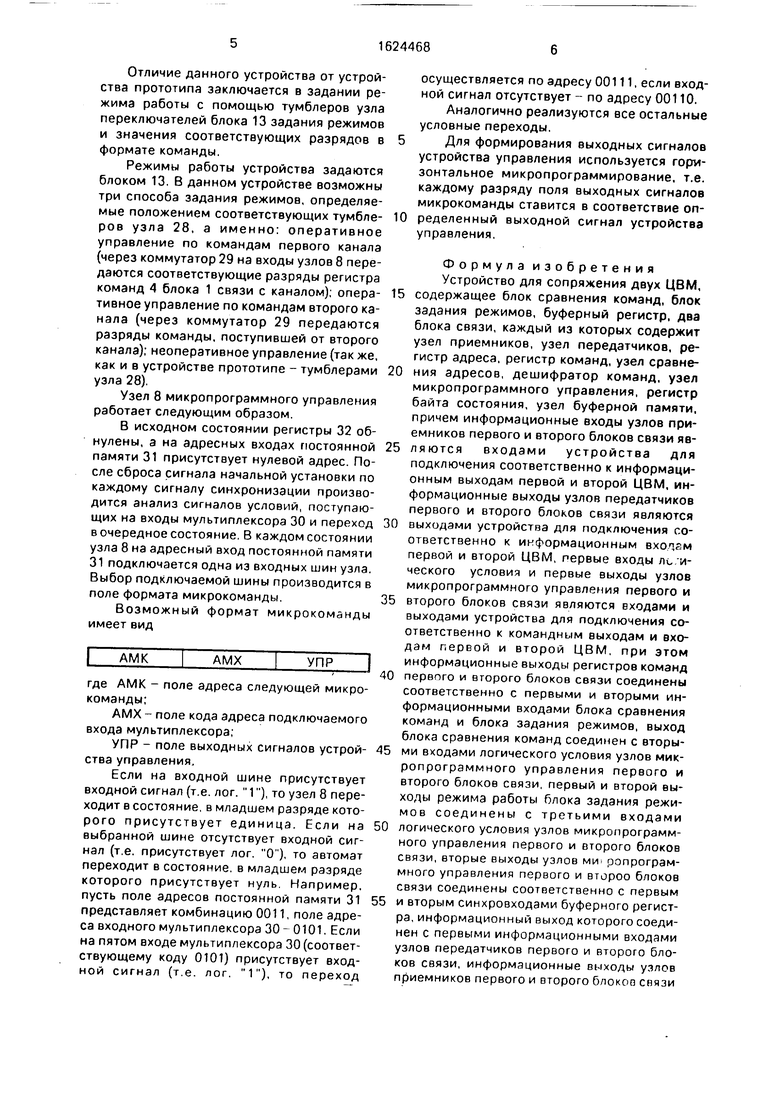

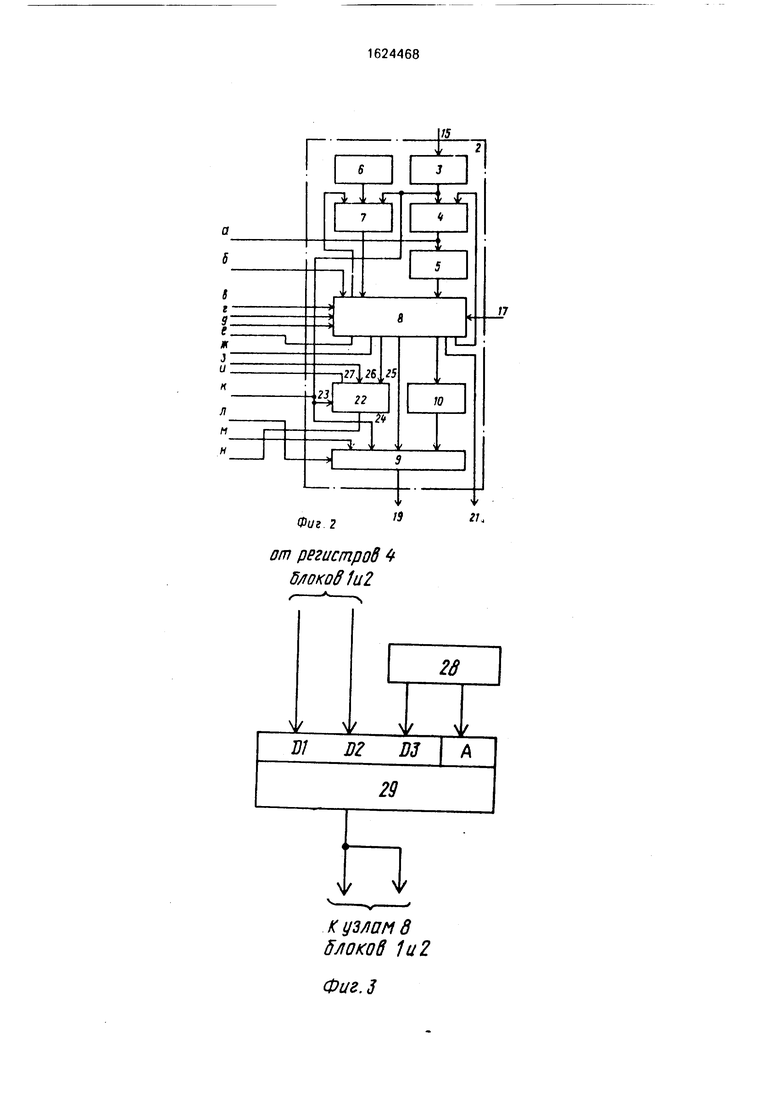

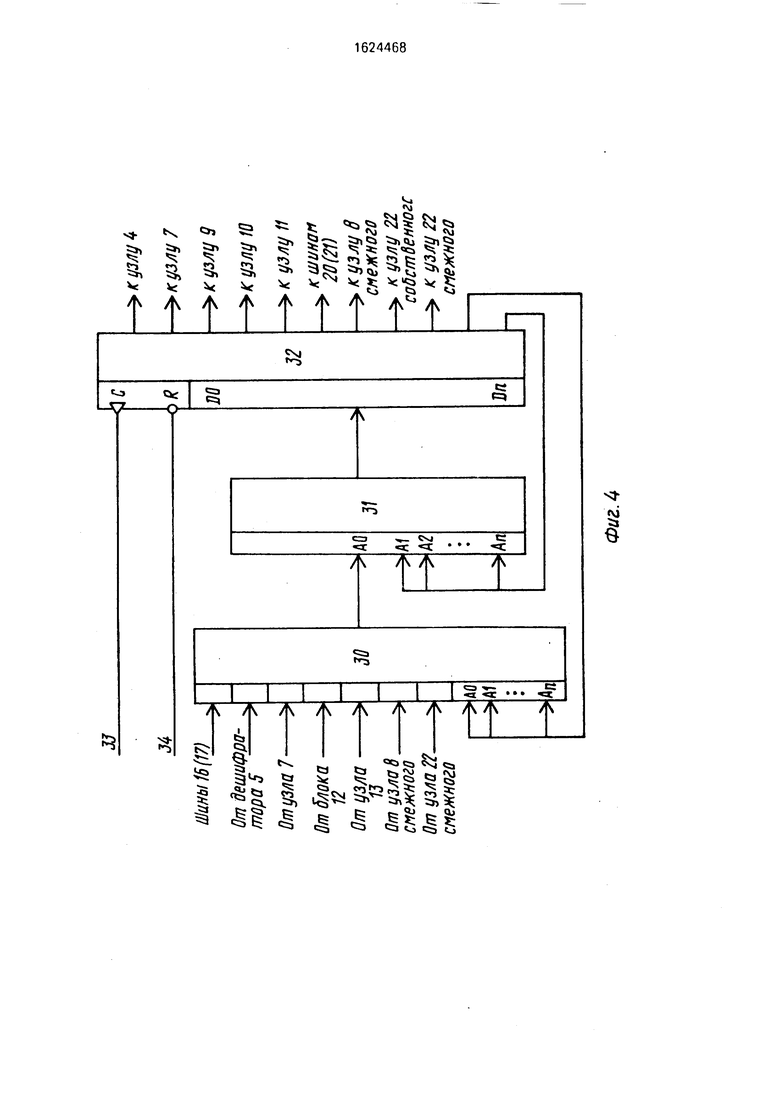

На фиг.1, 2 приведена блок-схема устройства; на фиг.З - функциональная схема блока задания режима; на фиг.4 - функциональная схема узла микропрограммного управления; на фиг.5 - граф алгоритма узла микропрограммного управления; на фиг.6 - функциональная схема узла буферной памяти.

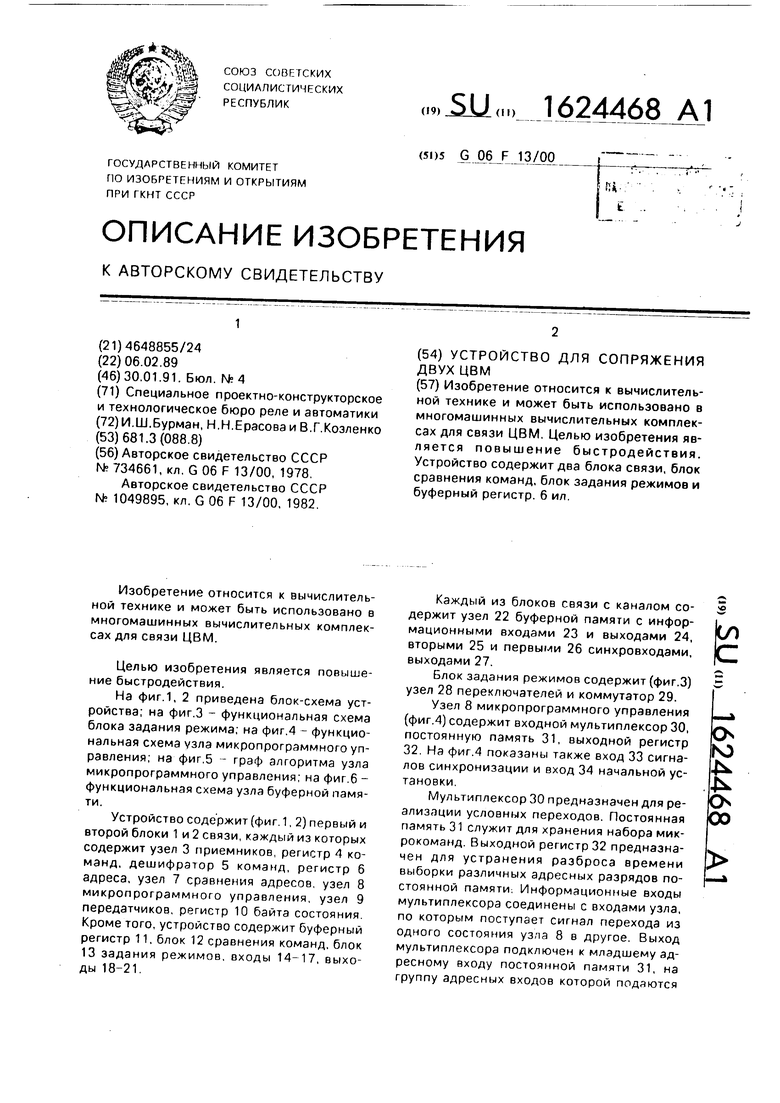

Устройство содержит (фиг. 1, 2) первый и второй блоки 1 и 2 связи, каждый из которых содержит узел 3 приемников, регистр 4 команд, дешифратор 5 команд, регистр 6 адреса, узел 7 сравнения адресов, узел 8 микропрограммного управления, узел 9 передатчиков, регистр 10 байта состояния. Кроме того, устройство содержит буферный регистр 11, блок 12 сравнения команд, блок 13 задания режимов, входы 14-17, выходы 18-21.

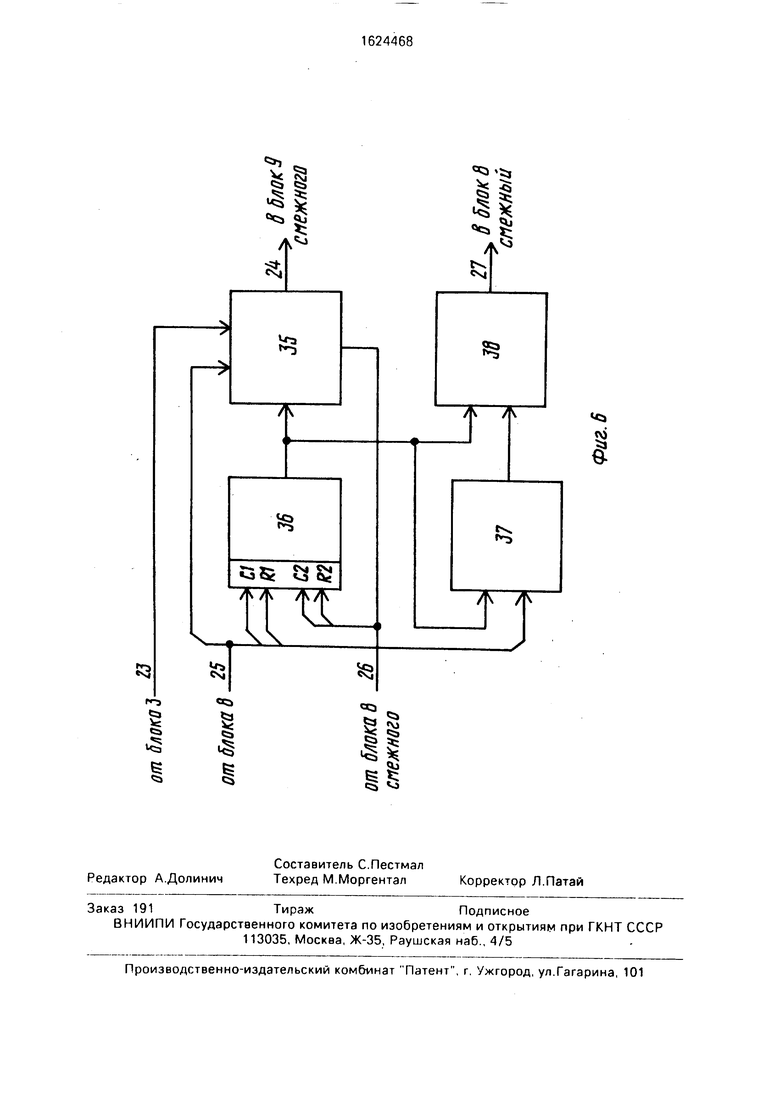

Каждый из блоков связи с каналом содержит узел 22 буферной памяти с информационными входами 23 и выходами 24, вторыми 25 и первыми 26 синхровходами, выходами 27.

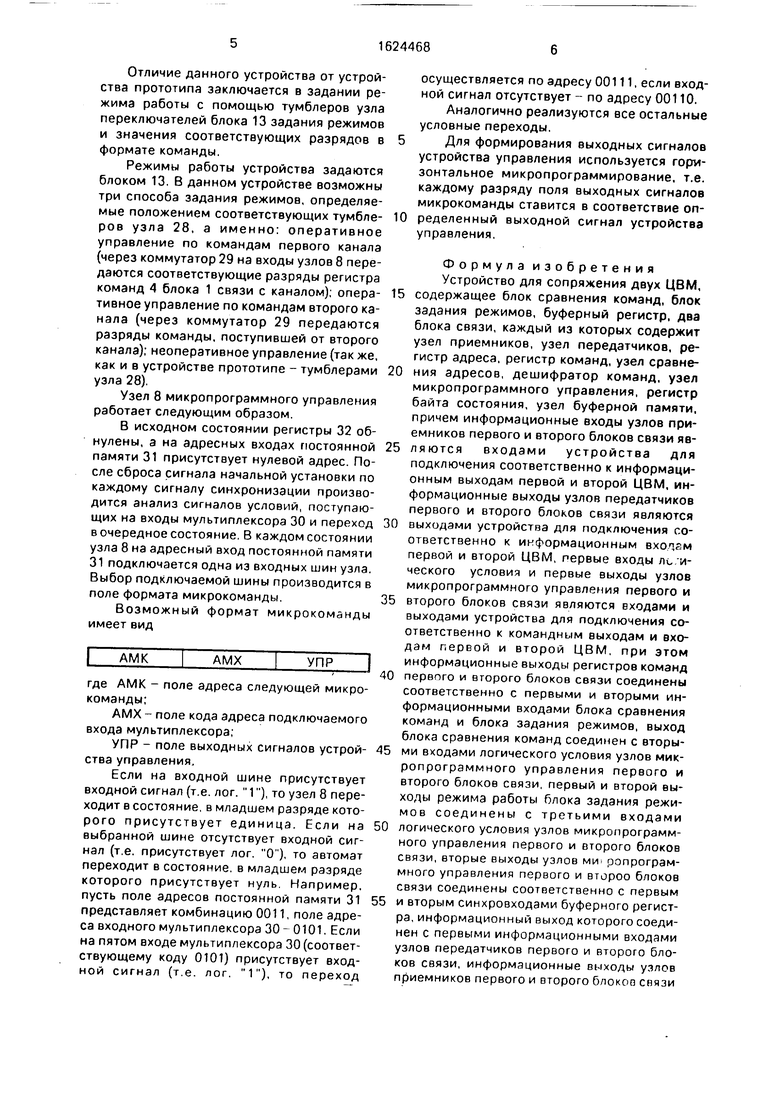

Блок задания режимов содержит (фиг.З) узел 28 переключателей и коммутатор 29.

Узел 8 микропрограммного управления (фиг.4) содержит входной мультиплексор 30, постоянную память 31, выходной регистр 32. На фиг.4 показаны также вход 33 сигналов синхронизации и вход 34 начальной установки.

Мультиплексор 30 предназначен для реализации условных переходов. Постоянная память 31 служит для хранения набора микрокоманд. Выходной регистр 32 предназначен для устранения разброса времени выборки различных адресных разрядов постоянной памяти. Информационные входы мультиплексора соединены с входами узла, по которым поступает сигнал перехода из одного состояния узла 8 в другое. Выход мультиплексора подключен к младшему адресному входу постоянной памяти 31, на группу адресных входов которой подаются

«г

Ё

О

ю

I

о со

сигналы с выходного регистра. Узел 8 реализован в виде микропрограммного автомата, граф-алгоритм которого представлен на фиг.5 (для упрощения приведена часть алгоритма, описывающая выполнение операции Запись в режиме Одна память. Остальные части алгоритма выполняются аналогичным образом. Каждая часть алгоритма может быть выполнена как отдельная микропрограмма). В этой графе в кружках изображен адрес ячейки постоянной памяти, в которой хранится микрокоманда; дугами изображены переходы из одного состояние в дру-ое1 названия сигнапов формируются в этих состояниях; переход из одного состояния (начало дуги) в другое (стрелка дуги) происходит при наличии этого сигнала.

Узлы 22 буферной памяти (фиг.6) содержат память 35, счетчик 36 адреса, регистр 37 количества байтов и узел 38 сравнения.

В режиме Одна память устройство работает следующим образом.

Канал ЦВМ (например, первый) выбирает устройство в соответствии с принципами организации еводэ-вывода интерфейса ЕС ЭВМ. При этом адрес от канала по шинам 14 канала черезузет 3 поступает вузел 7 для сравнения с адресом адаптера, хранимым в ргчистре о адреса. Результат сравнения адресов выдается в узел 8. Если адреса совпадают, из узла 3 адрес адаптера трепела руется через узел 9 на выход 18 и далее в анал.

Дешифратор 5 декодирует команду, полученную из канала и хранимую в регистре 4.

Пос ie расшифровки команды первого канала и определения режима работы по коду команды или состоянию узла 28 блока

13устройство осуществляет прием по входу

14и запись информации через узел 3 в узел 22 блока 1. При зтом узел 8 блока 1 формирует сигнал обнуления, а затем сигналы мо- д фикации счетчика 36 и сигналы обращения в память 35, которые поступают на входы управления записью узла 22 блока 1.

После окончания приема данных от первого канала (окончание определяется каналом узел 8 блока 1 формирует сигнал Записи о регистр 37, который поступав на входы управления записью узла 22 блока 1, заносит в регистр 11 команду первого канала, а узел 8 блока 2 формирует и передает зо второй канал байт состояния с указателем Внимание. В ответ второй канал вводит команду уточнения состояния, по которой ему передается содержимое регистра 11, т.е. /оманда первого канала. По содержимому регистра 11 программа второй ЦВМ определяет, какую команду необходимо ввести в устройство и через второй канал вводит ее в устройство. При сравнении команд блоком 12 (сравнению подвергаются поля модификаторов) устройство начинает передавать во второй канал данные из узла 22 блока 1 через узел 9 блока 2. При этом узел 8 блока 2 формирует сигналы обнуле0 ния, а затем сигналы модификации счетчика 36 и сигналы обращения в память 35, которые поступают на вход управления чтением узла 22 блока 1.

При сравнении значения счетчика 36 и

5 регистра 37, что свидетельствует о том, что завершена передача во второй канал данных, принятых от первого канала, на выходе узла 38 сравнения формируется сигнал, поступающий с выхода синхронизации узла 22

0 блока 1 в узел 8 блока 2. по которому оканчивается выполнение команды во втором канале.

При передаче данных из второго канала первое устройство работает также за исклю5 чением того, что данные записываются в

узел 22 блока 2, записью в узел 22 управляет

узел 8 блока 2, а считыванием - узел 8 блока 1.

В режиме Две памяти устройство

обеспечивает одновременный прием дан0 ных из первого и второго каналов в узлы 22 соответственно блоков 1 и 2 или передачу в первый и второй канал данных из узлов 22 соответственно блоков 2 и 1.

В этом режиме, если оба канала переда5 ют данные в устройство одновременно, данные первого канала записываются в узел 22 блока 1, а данные второго канала - в узел 22 блока 2. Затем во второй канал через регистр 11 и узел блока 2 передается байт

0 состояния с указателем Внимание, после этого в первый канал через регистр 11 и узел 9 блока 2 передается байт состояния с указателем Внимание, после этого в первый канал через регистр 11 и узел 9 блока 1

5 передается такой же байт. Программы первой и второй ЦВМ вводят в устройство команды уточнения состояния, определяют необходимые ответные команды и вводят их через первый и второй каналы в устройство.

0 По этим командам данные из узла 22 блока 1 передаются во второй канал, а данные из узла 22 блока 2 - в первый канал. В этом режиме блок 12 не работает и сравнение команд не производится. Узлами 8 по сигна5 лам дешифратора команд 5 производится только анализ направления передачи данных (команда записи или чтения). Собственно процедуры записи и считывания в узлы 22 осуществляются так же, как и в режиме Одна память,

Отличие данного устройства от устройства прототипа заключается в задании режима работы с помощью тумблеров узла переключателей блока 13 задания режимов и значения соответствующих разрядов в формате команды.

Режимы работы устройства задаются блоком 13. В данном устройстве возможны три способа задания режимов, определяемые положением соответствующих тумблеров узла 28, а именно: оперативное управление по командам первого канала (через коммутатор 29 на входы узлов 8 передаются соответствующие разряды регистра команд 4 блока 1 связи с каналом); оперативное управление по командам второго канала (через коммутатор 29 передаются разряды команды, поступившей от второго канала); неоперативное управление (так же, как и в устройстве прототипе - тумблерами узла 28).

Узел 8 микропрограммного управления работает следующим образом.

В исходном состоянии регистры 32 обнулены, а на адресных входах постоянной памяти 31 присутствует нулевой адрес. После сброса сигнала начальной установки по каждому сигналу синхронизации производится анализ сигналов условий, поступающих на входы мультиплексора 30 и переход в очередное состояние. В каждом состоянии узла 8 на адресный вход постоянной памяти 31 подключается одна из входных шин узла. Выбор подключаемой шины производится в поле формата микрокоманды.

Возможный формат микрокоманды имеет вид

L

АМК

АМХ

УПР

где АМК - поле адреса следующей микрокоманды;

АМХ - поле кода адреса подключаемого входа мультиплексора;

УПР - поле выходных сигналов устройства управления.

Если на входной шине присутствует входной сигнал (т.е. лог. 1), то узел 8 переходит в состояние, в младшем разряде которого присутствует единица. Если на выбранной шине отсутствует входной сигнал (т.е. присутствует лог. О), то автомат переходит в состояние, в младшем разряде которого присутствует нуль. Например, пусть поле адресов постоянной памяти 31 представляет комбинацию 0011, поле адреса входного мультиплексора 30 - 0101. Если на пятом входе мультиплексора 30 (соответствующему коду 0101) присутствует входной сигнал (т.е. лог. 1), то переход

осуществляется по адресу 00111, если входной сигнал отсутствует - по адресу 00110.

Аналогично реализуются все остальные условные переходы.

5Для формирования выходных сигналов

устройства управления используется горизонтальное микропрограммирование, т.е. каждому разряду поля выходных сигналов микрокоманды ставится в соответствие оп10 ределенный выходной сигнал устройства управления.

Формула изобретения Устройство для сопряжения двух ЦВМ,

15 содержащее блок сравнения команд, блок задания режимов, буферный регистр, два блока связи, каждый из которых содержит узел приемников, узел передатчиков, регистр адреса, регистр команд, узел сравне0 ния адресов, дешифратор команд, узел микропрограммного управления, регистр байта состояния, узел буферной памяти, причем информационные входы узлов приемников первого и второго блоков связи яв5 ляются входами устройства для подключения соответственно к информационным выходам первой и второй ЦВМ, информационные выходы узлов передатчиков первого и второго блоков связи являются

0 выходами устройства для подключения соответственно к информационным входим первой и второй ЦВМ, первые входы лс/и- ческого условия и первые выходы узлов микропрограммного управления первого и

5 второго блоков связи являются входами и выходами устройства для подключения соответственно к командным выходам и входам первой и второй ЦВМ. при этом информационные выходы регистров команд

0 первого и второго блоков связи соединены соответственно с первыми и вторыми информационными входами блока сравнения команд и блока задания режимов, выход блока сравнения команд соединен с вторы5 ми входами логического условия узлов микропрограммного управления первого и второго блоков связи, первый и второй выходы режима работы блока задания режимов соединены с третьими входами

0 логического условия узлов микропрограммного управления первого и второго блоков связи, вторые выходы узлов ми. ропрограм- много управления первого и второо блоков связи соединены соответственно с первым

5 и вторым синхровходами буферного регистра, информационный выход которого соединен с первыми информационными входами узлов передатчиков первого и второго блоков связи, информационные выходы узлов приемников первого и второго блокоо связи

соединены соответственно с первым и вторым информационными входами буферного регистра, первые информационные выходы узлов буферной памяти первого и второго блоков связи соединены с вторыми информационными входами узлов передатчиков второго и первого блоков связи соответственно, первые синхровходы узлов буферной памяти первого и второго блоков связи соединены с третьими выходами узлов микропрограммного управления второго и первого блоков связи соответственно, вторые информационные выходы узлов буферной памяти первого и второго блоков связи соединены с четвертыми входами логического условия узлов микропрограммного уп равнения второго и первого блоков связи соответствия, вход-выход логического условия узпа микропрограммного управления первого блока связи соединен с входом-выходом логического условия узла микропрог- pdMMHoro управления второго блока связи, причем в каждом блоке связи информационный выход регистра адреса соединен с пер- вым информационным входом узла сравнения адресов, второй информационный вход которого соединен с третьим информационным входом узла передатчиков, с информационным входом узла буферной памяти, с информационным выходом узла приемников и с информационным входом регистра команд, информационный выход которого соединен с информационным входом дешифратора команд, выход которого соединен с пятым входом логического условия узла микропрограммного управления, четвертый выход которого соединен с управляющим входом узла сравнения адресов, выход которого соединен с шестым входом логического условия узла микропрограммного управления, пятый выход которого соединен с информационным

входом регистра байта состояния, информационный выход которого соединен с четвертым информационным входом узла передатчиков, пятый информационный вход которого соединен с шестым выходом узла

микропрограммного управления, седьмой и восьмой выходы которого соединены соответственно с синхровходом регистра команд и вторым синхровходом узла буферной памяти, при этом блок задания

режимов содержит узел переключателей, отличающееся тем, что, с целью повышения быстродействия, в блок задания режимов введен коммутатор, при этом первый и второй информационные входы

и информационный выход коммутатора являются соответственно первым и вторым информационными входами, первый и вторым выходами режима работы блока, причем в блоке задания режимов первый и

второй выходы узла переключателей соединены соответственно с третьим информационным входом и управляющим входом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал - канал | 1988 |

|

SU1608677A2 |

| Адаптер канал-канал | 1985 |

|

SU1305697A2 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Адаптер канал-канал | 1982 |

|

SU1049895A2 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Имитатор канала | 1988 |

|

SU1520523A2 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных комплексах для связи ЦВМ. Целью изобретения является повышение быстродействия. Устройство содержит два блока связи, блок сравнения команд, блок задания режимов и буферный регистр. 6 ил.

го

18

Фие 1

Фиг. 2

от регистров 4 б/1око81и2

3L

Ш D2 DJ

к узлам 8 блоков 1и2

Фиг.З

19

21

п

i&f §s

|ЭЙ g tat §|SI

«

en

| Адаптер канал-канал | 1978 |

|

SU734661A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптер канал-канал | 1982 |

|

SU1049895A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-30—Публикация

1989-02-06—Подача