Фиг.1

Изобретение относится к вычислительной технике, может быть использовано при проектировании полупроводниковых постоянных и репрограммируемых запоминающих устройств повышенной надежности и малым потреблением мощности и является дополнительным к авт. св. № 1322376.

Цель изобретения - повышение надежности устройства.

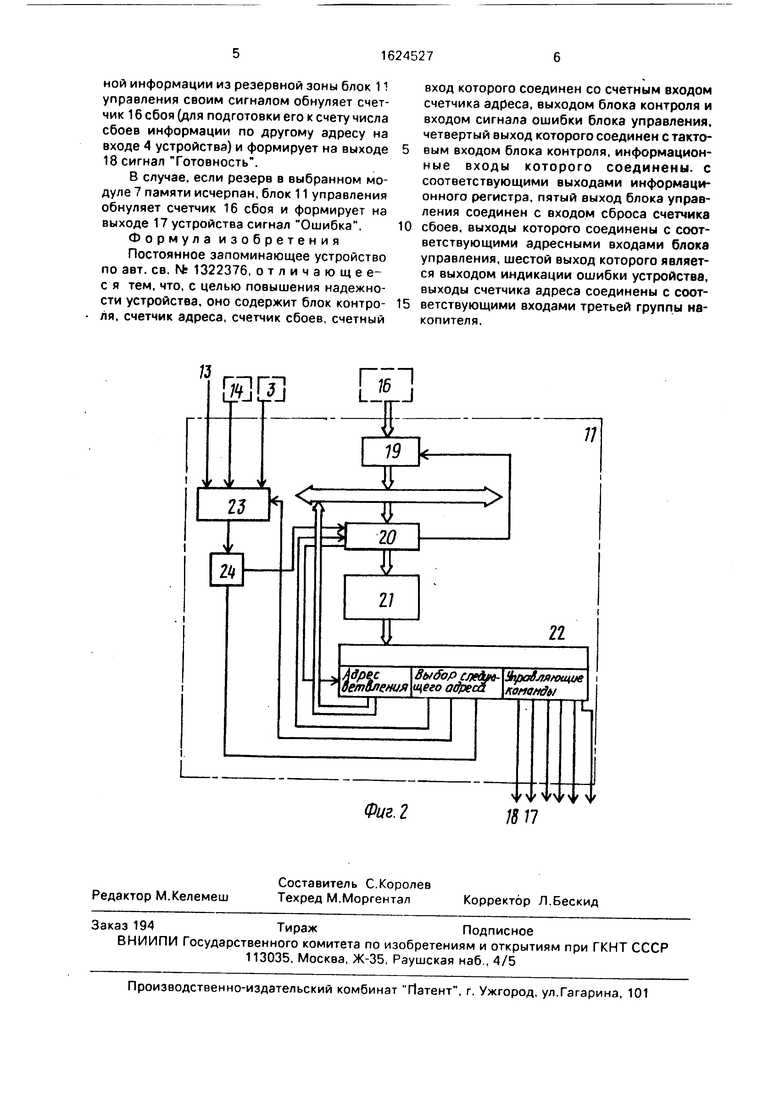

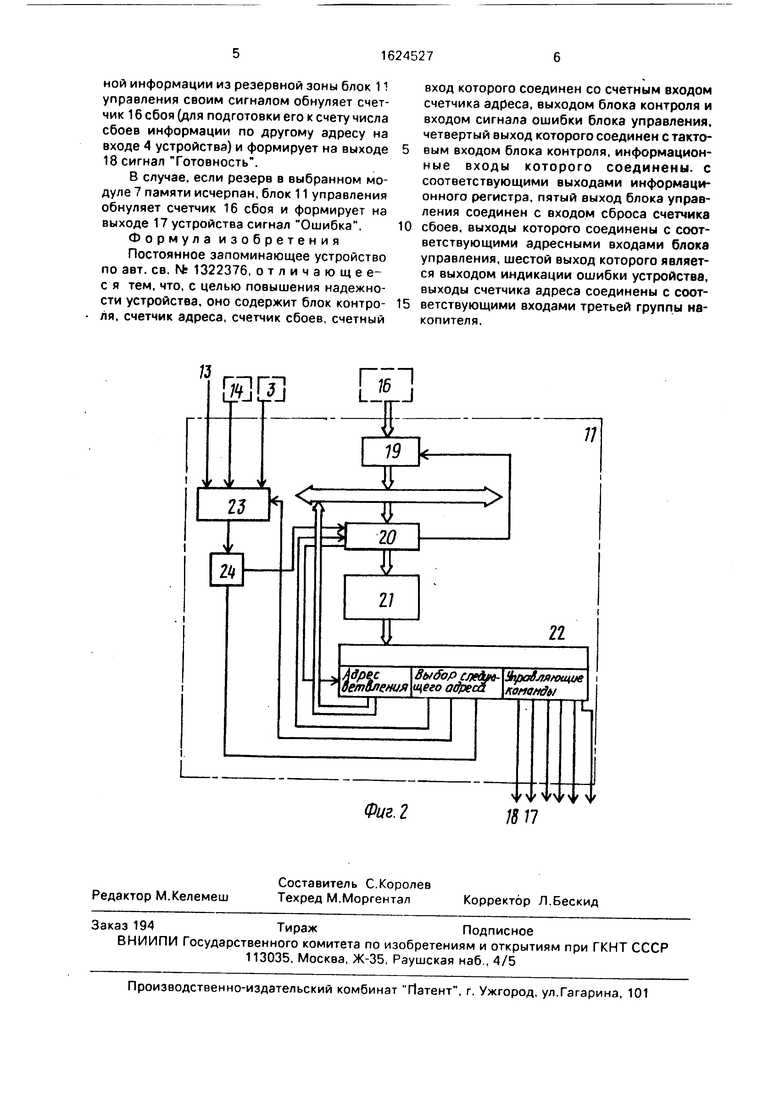

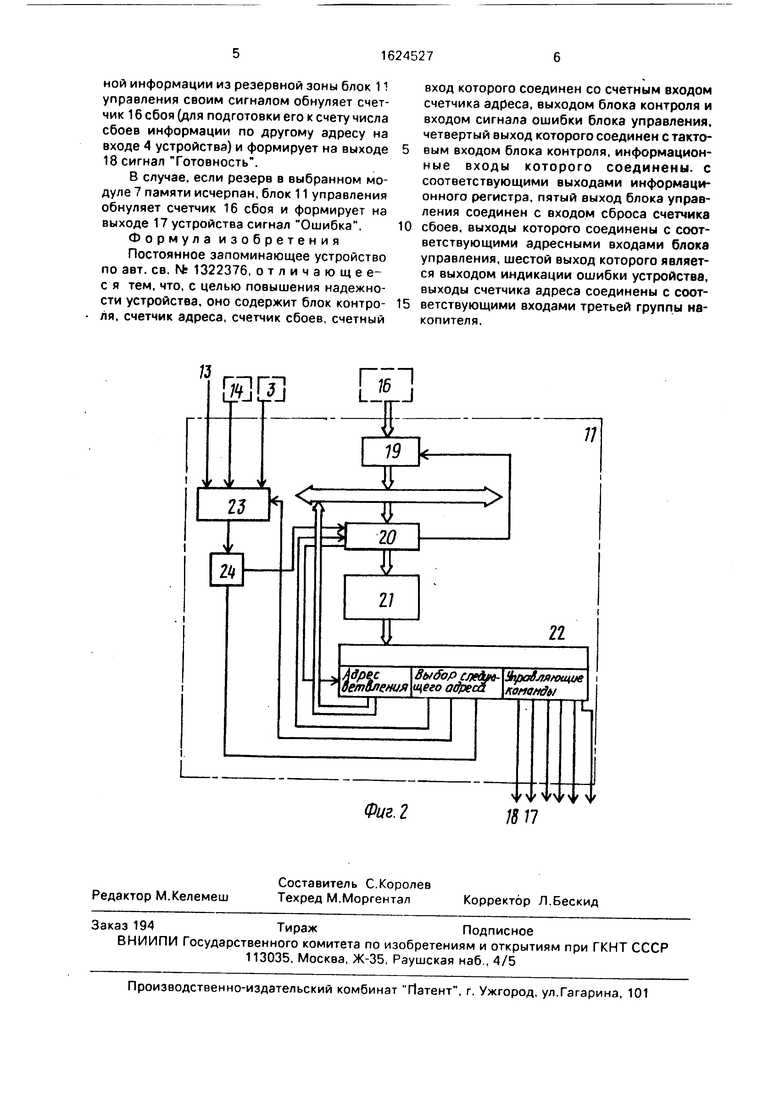

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - структурная схема ого блока управления.

Устройство содержит регистр 1 адреса старших разрядов, регистр 2 адреса младших разрядов, блок 3 сравнения, адресные входы 4, дешифратор 5, накопитель 6, состоящий из модулей 7 памяти, блок 8 ключей, информационный регистр 9, выходы 10, блок 11 управления, одновибратор 12, управляющий вход 13, блок 14 контроля, счетчик 15 адреса, счетчик 16 сбоев, выход 17 индикации ошибки, управляющий выход 18. Блок 11 управления состоит из преобразователя 19 адреса, элемента 20 управления следующим адресом, узла 21 памяти, регистра 22 микрокоманд, мультипилексора 23, инвертора 24.

Устройство работает следующим образом.

В каждом цикле считывания на входы устройства поступают: сигнал обращения - на вход 13 и код адреса - на входы 4. При этом старшие разряды кода адреса поступают на входы регистра 1 и блока 3 сравнения, а младшие разряды поступают на установочные входы регистра 2 и потом на соответствующие адресные входы модулей 7 памяти. Кроме того, на часть адресных входов модулей 7 памяти подаются сигналы с внутреннего счетчика 15 адреса.

Регистр 1 выполнен стробируемым, поэтому в нем хранится код модуля 7 памяти, к которому было обращение в предыдущем цикле считывания. Коды адресов модулей 7 памяти предыдущего обращения и настоящего поступают на входы блока 3 сравнения,на выходе которого вырабатывается признак сравнения или несравнения, поступающий в блок 11 управления. Если выраба- тывается признак несравнения, это означает, что производится обращение к другому модулю 7 памяти, блок 11 управления вырабатывает импульс записи нового кода адреса старших разрядов в регистр 1. Этот код через дешифратор 5 осуществляет включение соответствующего ключа из блока 8 ключей и осуществляет разрешение выборки с соответствующего модуля 7 памяти. Блок 11 управления стробирует прием считываемой информации в регистр 9, затем стробирует блок 14 контроля, а если на его выходе нет сигнала сбоя, что свидетельствует о правильности считанной информации на выходе 10 устройства, выдает

признак Готовность на выходе 18 устройства.

Так как счетчик 15 адреса не изменяет свое состояние при считывании информации без сбоя, это означает, что при считыва0 нии массива информации происходит обращение в одни и те же зоны в модулях 7 памяти, определяемых кодом адреса счетчика 15 (коэффициент пересчета счетчика 15 адреса определяется количеством резерв5 ных зон в модуле 7 памяти, в которых хранится одинаковая информация).

Если блок 3 сравнения вырабатывает признак сравнения, возможно ускорение выборки из накопителя, так как обращение

0 осуществляется в тот же самый модуль 7 памяти, что и в предыдущем цикле.

В том случае, когда в обращениях к постоянному запоминающему устройству наступает перерыв (например, во время

5 взаимодействия процессора с другим запоминающим устройством, устройством ввода-вывода и т. п.), то на выходе одновибратора 12 снимается сигна л, разрешающий работу дешифратора 5 и блока 3

0 сравнения, С выходов дешифратора 5 снимается сигнал включения ключа в блоке 8 ключей и снимается питание с модуля 7 памяти. При первом обращении к устройству после перерыва на выходе одновибратора

5 12 отсутствует сигнал, разрешающий работу блока 3 сравнения, и на его выходе будет сигнал несравнения даже при равенстве кодов адреса старших разрядов на входе 4 устройства и выходе регистра 1 старших

0 разрядов. По сигналу обращения, подаваемому на вход 13 устройства, блок 11 управления синхронизирует работу устройства и выдает признак Готовность на выход 18 по длинному циклу, а одновибратор 12 форми5 рует сигнал, разрешающий работу дешифратора 5 и блока 3 сравнения. Введение одновибратора 12 позволяет снизить потребляемую устройством мощность за счет снятия питания со всех модулей 7 памяти

0 при отсутствии обращения к устройству.

При сбое информации блок 14 контроля формирует сигнал ошибки, который изменяет содержание счетчиков 15 и 16 (счетчик 16 сбоя предварительно обнуляется), блок 11

5 управления анализирует код счетчика 16 сбоев на наличие резерва в выбранном модуле 7 памяти и, если он имеется, обеспечивает повторное обращение в резервную зону в соответствии с новым кодом адреса счетчика 15, а в случае считывания правильной информации из резервной зоны блок 11 управления своим сигналом обнуляет счетчик 16 сбоя (для подготовки его к счету числа сбоев информации по другому адресу на входе 4 устройства) и формирует на выходе 18 сигнал Готовность.

В случае, если резерв в выбранном модуле 7 памяти исчерпан, блок 11 управления обнуляет счетчик 16 сбоя и формирует на выходе 17 устройства сигнал Ошибка. Формула изобретения Постоянное запоминающее устройство по авт. св. N 1322376, отличающее- с я тем, что, с целью повышения надежности устройства, оно содержит блок контроля, счетчик адреса, счетчик сбоев, счетный

0

вход которого соединен со счетным входом счетчика адреса, выходом блока контроля и входом сигнала ошибки блока управления, четвертый выход которого соединен с тактовым входом блока контроля, информационные входы которого соединены, с соответствующими выходами информационного регистра, пятый выход блока управления соединен с входом сброса счетчика сбоев, выходы которого соединены с соответствующими адресными входами блока управления, шестой выход которого является выходом индикации ошибки устройства, выходы счетчика адреса соединены с соответствующими входами третьей группы накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1985 |

|

SU1322376A2 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Постоянное запоминающее устройство с самоконтролем | 1979 |

|

SU858118A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Устройство для коррекции ошибок вычислительного процесса | 1991 |

|

SU1807487A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

Изобретение относится к вычислительной технике, может быть использовано при проектировании полупроводниковых постоянных и репрограммируемых запоминающих устройств и является дополнительным к авт. св. № 1322376. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в устройство введены блок 14 контроля, счетчик 15 адреса, счетчик 16 сбоев. При сбое блок 14 формирует сигнал ошибки, который изменяет состояние счетчиков 15, 16. Блок 11 управления анализирует код счетчика 16 сбоев и обеспечивает повторное обращение в резервную зону накопителя 6 в соответствии с новым кодом адреса счетчика 15. 2 ил.

Фиг. 2

| Постоянное запоминающее устройство | 1985 |

|

SU1322376A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-01-30—Публикация

1989-01-02—Подача