Изобретение относится к вычислительной технике, может быть использовано при проектировании постоянных запоминающих устройств с малым потреблением мощности и является усоверп1енствованием устройства по авт. св. № 1014037.

Цель изобретения снижение потребляемой мощности.

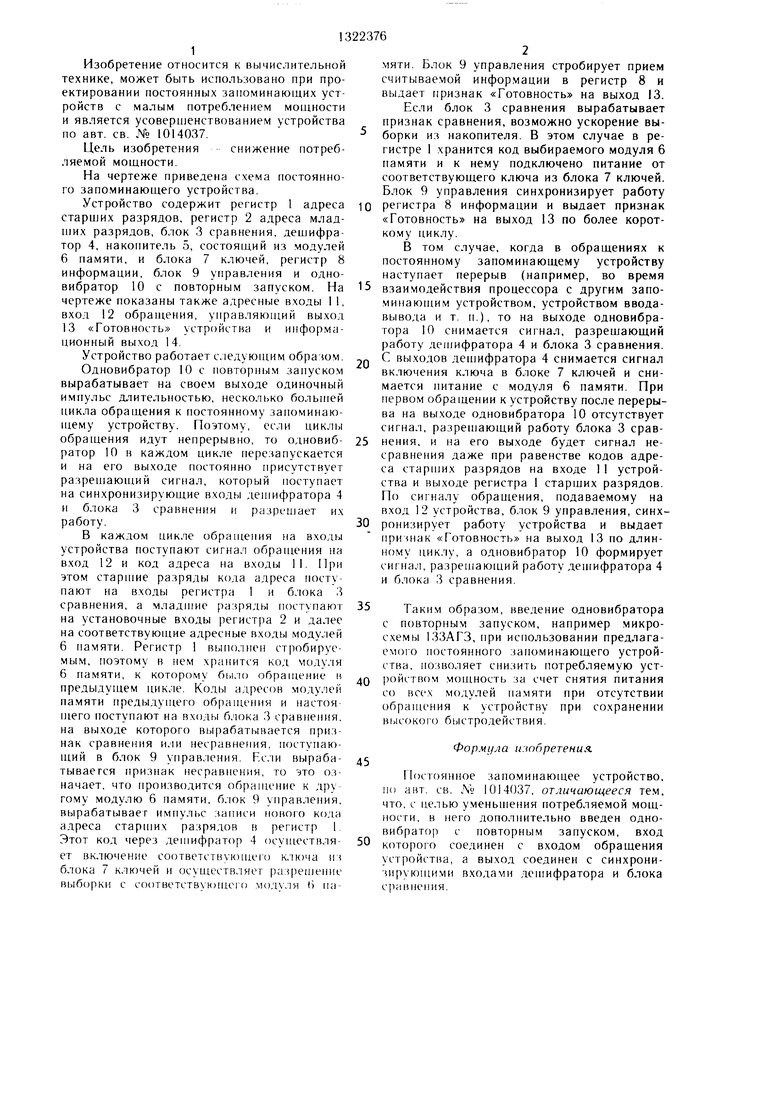

На чертеже приведена схема постоянного запоминающего устройства.

Устройство содержит регистр 1 адреса старщих разрядов, регистр 2 адреса младших разрядов, блок 3 сравнения, дешифратор 4, накопитель 5, состоящий из модулей 6 памяти, и блока 7 ключей, регистр 8 информации, блок 9 управления и одно- вибратор 10 с повторным запуском. На чертеже показаны также адресные входы 1 1, вход 12 обращения, управляющий выход 13 «Готовность устройства и информационный выход 14.

Устройство работает следующим образом.

Одновибратор 10 с повторшям запуском вырабатывает на своем выходе одиночный импульс длительностью, несколько большей цикла обращения к постоянному запоминающему устройству. Поэтому, если циклы обращения идут непрерывно, то одновиб- ратор 10 в каждом цикле перезапускается и на его выходе постоянно присутствует разрешающий сигнал, который поступает на синхронизирующие входы дешифратора 4 и блока 3 сравнения и разрешает их работу.

В каждом цикле обращения на входы устройства поступают сигнал обрап1ения на вход 12 и код адреса на входы II. При этом старпже разряды кода адреса поступают на входы регистра 1 и блока 3 сравнения, а младшие разряды поступают на установочные входы регистра 2 и далее на соответствующие адресные входы модулей 6 памяти. Регистр 1 выполнен стробируе- мым, поэтому в нем хранится код модуля 6 памяти, к которому б1,1Л() обращение и предыдущем цикле. Коды адресов модулей памяти предыдущего обрап1,ения и настоя- niero поступают на входы блока 3 сравнения, на выходе которого вырабатывается признак сравнения или несравнерщя. поступающий в блок 9 управ, 1ения. Р.сли вырабатывается признак несравнения, то это означает, что производится обрап1ение к другому модулю 6 памяти, блок 9 управления, вырабатывает импульс записи нового кода адреса стар1пих разрядов в регистр I Этот код через дешифратор 4 осуществляет включение соответствующего ключа из блока 7 ключей и осуществ, 1яег разрешение выборки с соответствующего модуля в па.мяти. Блок 9 управления стробирует прием считываемой информации в регистр 8 и выдает признак «Готовность на выход 13. Если блок 3 сравнения вырабатывает признак сравнения, возможно ускорение выборки из накопителя. В этом случае в регистре 1 хранится код выбираемого модуля 6 памяти и к нему подключено питание от соответствующего ключа из блока 7 ключей. Блок 9 управления синхронизирует работу

0 регистра 8 информации и выдает признак «Готовность на выход 13 по более короткому циклу.

в том случае, когда в обращениях к постоянному запоминающему устройству наступает перерыв (например, во время

5

взаимодействия процессора с другим запоминаюпшм устройством, устройством ввода- вывода и т. п.), то на выходе одновибра- тора 10 снимается сигнал, разрешающий работу дешифратора 4 и блока 3 сравнения.

Q С выходов дешифратора 4 снимается сигнал включения ключа в блоке 7 ключей и снимается питание с модуля 6 памяти. При первом обращении к устройству после перерыва на выходе одновибратора 10 отсутствует сигнал, разре1пающий работу блока 3 срав5 нения, и на его выходе будет сигнал несравнения даже при равенстве кодов адреса старших разрядов на входе 11 устройства и выходе регистра 1 старщих разрядов. По сигналу обращения, подаваемому на вход 12 устройства, блок 9 управления, синх0 ронизирует работу устройства и выдает признак «Готовность на выход 13 по длинному циклу, а Одновибратор 10 формирует сигнал, разрешающий работу денжфратора 4 и блока 3 сравнения.

5 Таким образом, введение одновибратора с повторным запуском, например микросхемы 133АГЗ, при использовании предлагаемого постоянного запоминающего устройства, позволяет снизить потребляемую уст0 ройстЕотм мощность за счет снятия питания со Eicex модулей памяти при отсутствии обращения к устройству при сохранении BbicoKoro быстродействия.

Формула и:юбретения.

Постоянное запоминаю цее устройство, по ант. св. Л 1014037, отличающееся те.м, что, с це,1ью уменьшения потребляемой мощности, в него дополнительно введен одно- вибратор с повторным запуском, вход которого соединен с входом обращения устройства, а выход соединен с синхронизирующими входами дешифратора и блока с 1и непия.

6

1

Гото&ност

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1989 |

|

SU1624527A2 |

| Постоянное запоминающее устройство | 1981 |

|

SU1014037A1 |

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство индикации состояния ЭВМ | 1989 |

|

SU1667067A1 |

| Запоминающее устройство с контролем | 1988 |

|

SU1508287A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1280455A1 |

Изобретение относится к вычислительной технике и является усовершенствованием известного устройства по авт. св. № 1014037. Целью изобретения является снижение потребляемой устройством мощности за счет снятия питания со всех модулей памяти при отсутствии обращений к устройству при сохранении высокого быстродействия. Для достижения поставленной цели в устройство введен одновибратор с повторным запуском, выходы которого соединены с дополнительными входами дещифратора и блока сравнения. I ил. « сл со ю o со О) N3

| Постоянное запоминающее устройство | 1981 |

|

SU1014037A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-07-07—Публикация

1985-02-28—Подача