СХ NJ

СЛ Ю Ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный регистр | 1986 |

|

SU1411828A1 |

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ШАБЛОНОВ БИТ ПЕРЕМЕННОЙ РАЗРЯДНОСТИ | 2023 |

|

RU2809741C1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Цифровой фильтр | 1984 |

|

SU1205152A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ПЕРЕКРЫВАЮЩИХСЯ И НЕПЕРЕКРЫВАЮЩИХСЯ ШАБЛОНОВ БИТ В ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2807299C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ШАБЛОНОВ БИТ И ИНТЕРВАЛОВ МЕЖДУ ШАБЛОНАМИ БИТ | 2024 |

|

RU2824560C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ШАБЛОНОВ БИТ И ОПРЕДЕЛЕНИЕ ЧИСЛА БИТ МЕЖДУ ШАБЛОНАМИ | 2024 |

|

RU2833961C1 |

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах хранения и обработки информации. Целью изобретения является повышение быстродействия многофункционального регистра в режиме суммирования. Регистр позволяет реализовать различные логические, арифметические и специальные функции. Каждый разряд 1 регистра содер- жит RS-триггер 2, семь элементов И 3-9, два элемента ИЛИ 10-11, два элемента ИЛИ- НЕ 12-13, элемент НЕ 14. элемент НЕ 15 с увеличенной задержкой, элемент И-НЕ 16 и элемент ИЛИ-НЕ 17с увеличенной задержкой. Для достижения поставленной цели в каждый разряд регистра введены элементы 11, 13, 16 и 17 и выполнены необходимые связи между ними и другими элементами каждого разряда регистра. 2 ил. Ё

Фиг. 2

Изобретение относится к вычислительной технике и может быть использовано в устройствах хранения и обработки информации.

Цель изобретения - повышение быстродействия многофункционального регистра в режиме суммирования.

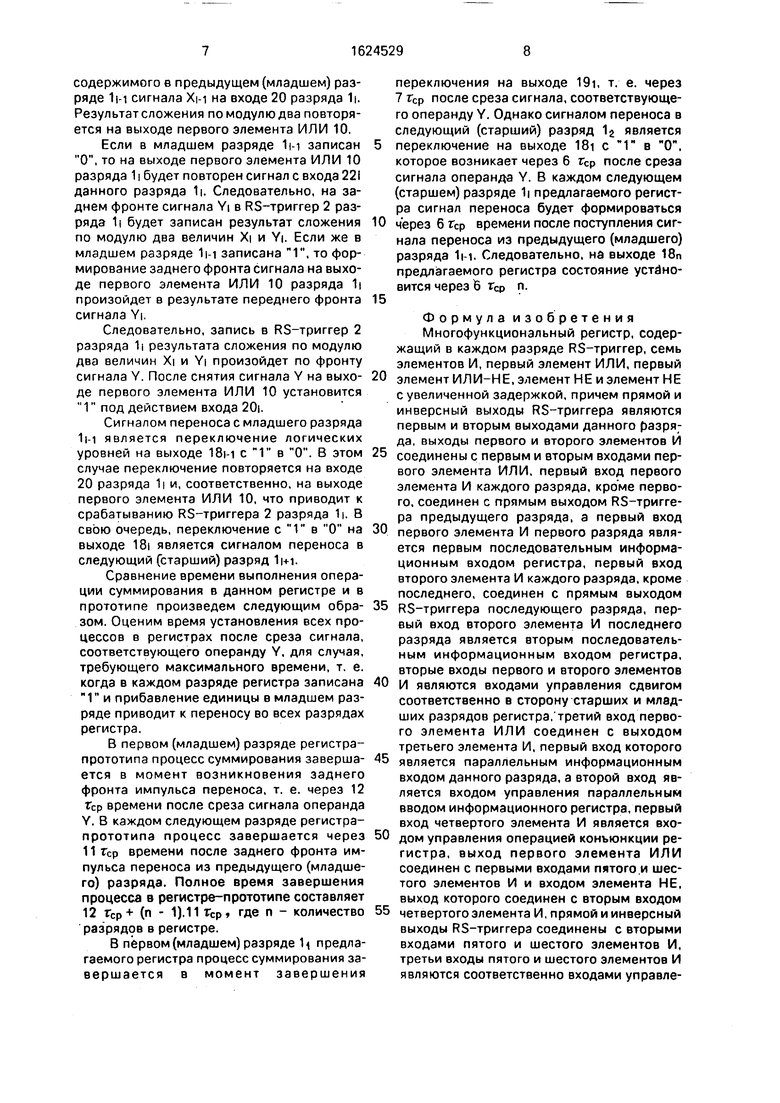

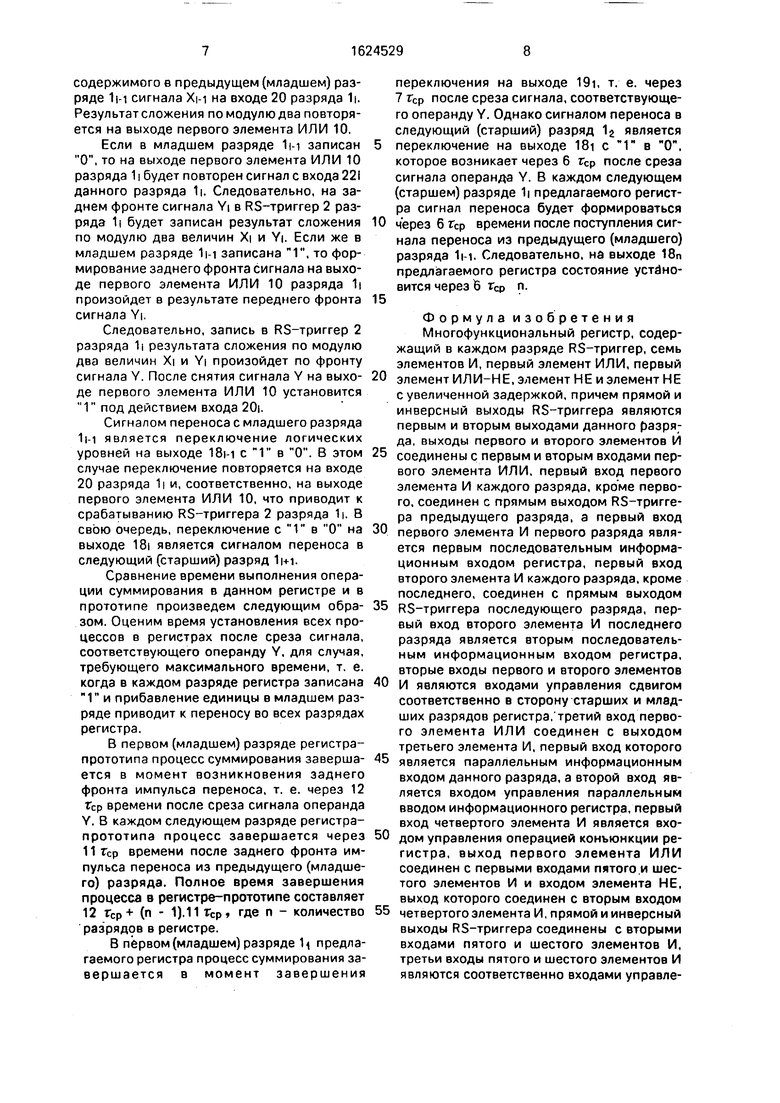

На фиг. 1 представлена структурная схема многофункционального регистра; на фиг. 2 - схема одного его разряда.

Многофункциональный регистр в каждом разряде 1 содержит RS-триггер 2, семь элементов И 3-9, два элемента ИЛИ 10-11, два элемента ИЛИ-НЕ 12-13, элемент НЕ 14, элемент НЕ 15 с увеличенной задержкой, элемент И-НЕ 16 и элемент ИЛИ-НЕ 17 с увеличенной задержкой. Прямой и инверсный выходы RS-триггера 2 являются первым 18 и вторым 19 выходами данного разряда 1.

На фиг. 1 и 2 показаны также первый 20 и второй 21 последовательные и параллельный 22 информационные входы регистра, входы управления сдвигом в сторону старших 23 и младших 24 разрядов регистра, вход управления параллельным вводом информации 25, входы управления операциями конъюнкции 26, запрета по первому операнду 27, Дизьюнкции 28 и суммирования 29 регистра.

Первый 12 и второй 13 элементы ИЛИ- НЕ, элемент НЕ 15 с увеличенной задержкой и элемент ИЛИ-НЕ 17 с увеличенной задержкой разрядов 1 предназначены для формирования кратковременных импульсов. Основное назначение элемента НЕ 15 с увеличенной задержкой и элемента ИЛИ- НЕ 17 с увеличенной задержкой - кратковременное хранение информации, полученной с выходов элементов И 6, 7 и 8. Формирование импульсов на выходе первого элемента ИЛИ-НЕ 12 происходит по срезу входного сигнала, поступающего с выхода шестого элемента И 8. Формирование импульса на выходе второго элемента ИЛИ-НЕ 13 происходит по срезу сигналов, поступающих с выходов четвертого 6, либо пятого 7 элементов И. При поступлении единичного информационного сигнала на первый вход первого элемента ИЛИ-НЕ 12 и на вход элемента НЕ 15 с увеличенной задержкой, первый элемент ИЛИ-НЕ 12 удерживается в закрытом состоянии. После прекращения информационного сигнала на обоих входах первого элемента ИЛИ-НЕ 12 устанавливаются открывающие его сигналы. Элемент находится в открытом состоянии, пока на выходе элемента НЕ 15 с увеличенной задержкой на установится единичный сигнал, закрывающий первый

элемент ИЛИ-НЕ 12. При этом на выходе последнего формируется кратковременный импульс, который подается на S-вход RS-триггера 2 и осуществляет его переключение в единичное состояние. На выходе второго элемента ИЛИ-НЕ 13 аналогично происходит формирование кратковременного импульса, который подается на R-вход RS-триггера 2 и осуществляет его переключение в нулевое состояние. Длительность кратковременного импульса ги должна быть не менее задержки переключения триггера 2 - т.т, т. е. .ь tT. Таким образом, время задержки элемента НЕ 15 с увеличенной

задержкой и элемента ИЛИ-НЕ с увеличенной задержкой определяется тз т,т + тэ , где -задержка элементов ИЛИ-НЕ 12 или 13. Чтобы исключить искажение длительности ти на выходах первого 12 и второго 13

элементов ИЛИ-НЕ требуется, чтобы сигналы на выходах четвертого б, пятого 7 и шестого 8 элементов И имели крутые срезы.

Все логические функции в многофункциональном регистре выполняются на основе характеристического уравнения RS-триггера

Qn+ 1 SvRQn .

Будем считать, что величина X находится в регистре, а на выходе первого элемента

ИЛИ 10 каждого разряда 1 находится величина Y.

Если единичный сигнал подать на вход

26управления операцией конъюнкции регистра, то предыдущее уравнение примет вид:

Qn+ , QvYX, т. е. Qn+ 1 YX. Срабатывание RS-триггера 2 каждого разряда 1 произойдет по срезу сигнала Y, либо управляющего сигнала на входе 26 управления операцией конъюнкции, и в регистре будет записана

величина YX.

Если единичный сигнал подать на вход

27управления операцией запрета по первому операнду регистра, то уравнение примет

вид:-

Qn+1 Ov(XY)X, т. е. Qn+i YX,

и в регистр будет записана величина YX. Если единичный сигнал подать на вход

28управления операцией дизъюнкции, то управление примет вид:

0Оп-м YXVOX, т. е. Qn-м Y v X.

Если единичный сигнал одновременно подавать на управляющие входы 27 и 28 регистра, то (ение примет вид:

Qn+ 1 YXV(YX)X, т. е. Qn+ 1 YX v YX, 5 Последнее выражение описывает сложение по модулю два величин X и Y.

Если единичные сигналы одновременно подать на управляющие входы 26 и 28 регистра, то уравнение примет вид:

Qn+i YX V YX, т. e. Q,vH Y.

Многофункциональный регистр в разных режимах работает следующим образом.

Рассмотрим, как происходит обнуление регистра. С этой целью на управляющий вход 26 подается единичный импульс длительностью не менее тз + гэ . Поскольку на остальных управляющих входах регистра установлены низкие уровни потенциала, то на выходе первого элемента ИЛИ 10 будет установлен О. Согласно описанному принципу действия управляющего сигнала с входа 26 регистра на заднем фронте этого сигнала в регистр будет записан результат конъюнкции О на выходе первого элемента ИЛИ 10 и содержимого RS-триггера 2 каждого разряда 1, т. е. произойдет обнуление регистра.

Для параллельного ввода информации в регистр код подается на информационные входы 221 - 22П разрядов 1 регистра.

Ввод можно осуществить двумя способами. При вводе информации первым способом регистр необходимо предварительно обнулить. Единичные управляющие сигналы подаются на входы 25, 27 и 28. Действием управляющего сигнала на входе 25 информационный сигнал устанавливается на выходе третьего элемента И 5 и затем на выходе первого элемента ИЛИ 10 каждого разряда 1. Согласно описанному принципу одновременного действия управляющих сигналов на входах 27 и 28 регистра по срезу информационного сигнала в регистр будет записан результат сложения по модулю два содержимого триггера 2 каждого разряда 1 (т. е. О) и информационного сигнала на выходе первого элемента ИЛИ 10 каждого разряда 1, т. е, в регистр будет записан код.

Для параллельного ввода информации в регистр вторым способом не обязательно предварительно его обнулять. Единичные управляющие сигналы подаются на входы 25, 26 и 28 регистра. Под действием управляющего входа 25 регистра информационный сигнал с входов 22i - 22П будет установлен на входе третьего элемента И 5 и затем на выходе первого элемента ИЛИ 10 каждого разряда 1. Согласно описанному принципу одновременного действия управляющих сигналов на входах 26 и 28 регистра по срезу информационного сигнала в регистр будет записана переменная Y. Следовательно, код будбт записан в регистр.

Сдвиг кода в сторону старших разрядов осуществляется совокупностью управляющих сигналов, которые подаются на входы 23, 26 и 28. После подачи управляющих сигналов открывается первый элемент И 3, а

затем первый элемент ИЛИ 10. В результате сигнал с предыдущего (младшего) разряда поступает через первый последовательный информационный вход 20 каждого разряда 5 1 на выход первого элемента ИЛИ 19 каждого разряда 1. После прекращения действия управляющих сигналов в регистре выполняется логическая функция переменной Y и логическое значение на выходе первого эле10 мента ИЛИ 10 каждого разряда 1 запишется в RS-триггер 2 каждого разряда 1. Следовательно, произойдетсдвиг в сторонустарших разрядов. Длительность управляющих сигналов должна быть не менее 6 гср .

5 Сдвиг кода в сторону младших разрядов осуществляется аналогично предыдущему. Сдвиг осуществляется совокупностью управляющих сигналов, которые подаются на входы 24, 26 и 28. При этом (в отличие от

0 предыдущей операции) открывается второй элемент И 4.

Двоичный счет осуществляется подачей управляющих сигналов в течение всего процесса счета на управляющие входы 23, 27 и

5 28. Счетные импульсы подаются на первый последовательный информационный вход 20i регистра.

Действием управляющего сигнала на входе 23 содержимое RS-триггера 2 каждо0 го разряда 11, кроме последнего, будет подаваться через выход 17 данного разряда 1| и информационный вход 20м-1 следующего (старшего) разряда 1|-и на выход первого элемента ИЛИ 10 старшего разряда 1|-м.

5 Согласно описанному принципу одновременного действия управляющих сигналов на входах 27 и 28 по срезу информационного сигнала на выходе первого элемента ИЛИ 10 в RS-триггер 2 будет

0 записан результат сложения по модулю два. Следовательно, действие управляющих сигналов на входах 23, 27 и 28 реализует структуру двоичного счетчика.

Сложение двух двоичных операндов X и

5 Y происходит следующим образом.

Предварительно в регистр вводится операнд X первым или вторым способом параллельного ввода информации.

Для функционирования регистра в ре0 жиме суммирования управляющие сигналы следует подать на управляющие входы 27, 28 29 регистра, а код операнда Y - на входы 221 - 22л регистра. При подаче управляющего сигнала на вход 29 элемент Й-НЕ 16 и

5 второй элемент ИЛИ 11 формируют на выходе седьмого элемента И 9 разряда логическую величину, которая является результатом сложения по модулю два информационного сигнала YI на входе 22i и

содержимого в предыдущем (младшем) разряде 1i-i сигнала Хи на входе 20 разряда 1|. Результат сложения по модулю два повторяется на выходе первого элемента ИЛИ 10.

Если в младшем разряде 1м записан О, то на выходе первого элемента ИЛИ 10 разряда 11 будет повторен сигнал с входа 22 данного разряда 1|. Следовательно, на заднем фронте сигнала YI в RS-триггер 2 разряда 1| будет записан результат сложения по модулю два величин Х| и YI. Если же в младшем разряде 1м записана 1, то формирование заднего фронта сигнала на выходе первого элемента ИЛИ 10 разряда 1| произойдет в результате переднего фронта сигнала YI,

Следовательно, запись в RS-триггер 2 разряда 1i результата сложения по модулю два величин Xi и YI произойдет по фронту сигнала Y. После снятия сигнала Y на выходе первого элемента ИЛИ 10 установится 1 под действием входа 20|.

Сигналом переноса с младшего разряда 1м является переключение логических уровней на выходе 18м с 1 в О. В этом случае переключение повторяется на входе 20 разряда 1i и, соответственно, на выходе первого элемента ИЛИ 10, что приводит к срабатыванию RS-триггера 2 разряда 1|. В свою очередь, переключение с 1 в О на выходе 18i является сигналом переноса в следующий (старший) разряд IH-L

Сравнение времени выполнения операции суммирования в данном регистре и в прототипе произведем следующим образом. Оценим время установления всех процессов в регистрах после среза сигнала, соответствующего операнду Y. для случая, требующего максимального времени, т. е. когда в каждом разряде регистра записана 1 и прибавление единицы в младшем разряде приводит к переносу во всех разрядах регистра.

В первом (младшем) разряде регистра- прототипа процесс суммирования завершается в момент возникновения заднего фронта импульса переноса, т, е. через 12 гср времени после среза сигнала операнда Y. В каждом следующем разряде регистра- прототипа процесс завершается через

11гср времени после заднего фронта импульса переноса из предыдущего (младшего) разряда. Полное время завершения процесса в регистре-прототипе составляет

12гср + (п - 1).11 гср, где п - количество разрядов в регистре.

В первом (младшем) разряде 1 предлагаемого регистра процесс суммирования за- вершается в момент завершения

переключения на выходе 19i, т. е. через 7 гср после среза сигнала, соответствующего операнду Y. Однако сигналом переноса в следующий (старший) разряд 1 является

переключение на выходе 18i с Г в О, которое возникает через 6 гср после среза сигнала операнда Y. В каждом следующем (старшем) разряде 1| предлагаемого регистра сигнал переноса будет формироваться

0 через б гср времени после поступления сигнала переноса из предыдущего (младшего) разряда 1м. Следовательно, на выходе 18п предлагаемого регистра состояние установится через В Гср п.

5

Формула изобретения Многофункциональный регистр, содержащий в каждом разряде RS-триггер, семь элементов И, первый элемент ИЛИ, первый 0 элемент ИЛИ-НЕ, элемент НЕ и элемент НЕ с увеличенной задержкой, причем прямой и инверсный выходы RS-триггера являются первым и вторым выходами данного разряда, выходы первого и второго элементов И

5

соединены с первым и вторым входами первого элемента ИЛИ, первый вход первого элемента И каждого разряда, кроме первого, соединен с прямым выходом RS-триггера предыдущего разряда, а первый вход

0 первого элемента И первого разряда является первым последовательным информационным входом регистра, первый вход второго элемента И каждого разряда, кроме последнего, соединен с прямым выходом

5 RS-триггера последующего разряда, первый вход второго элемента И последнего разряда является вторым последовательным информационным входом регистра, вторые входы первого и второго элементов

0 и являются входами управления сдвигом соответственно в сторону старших и младших разрядов регистра, третий вход первого элемента ИЛИ соединен с выходом третьего элемента И, первый вход которого

5 является параллельным информационным входом данного разряда, а второй вход является входом управления параллельным вводом информационного регистра, первый вход четвертого элемента И является вхо0 дом управления операцией конъюнкции регистра, выход первого элемента ИЛИ соединен с первыми входами пятого и шестого элементов И и входом элемента НЕ, выход которого соединен с вторым входом

5 четвертого элемента И, прямой и инверсный выходы RS-триггера соединены с вторыми входами пятого и шестого элементов И, третьи входы пятого и шестого элементов И являются соответственно входами управления операциями запрета по первому операнду и дизъюнкции регистра, первый вход седьмого элемента И является входом управления выполнением операции суммирования регистра, отличающийся тем, что, с целью повышения быстродействия регистра в режиме суммирования, в каждый разряд регистра введены второй элемент ИЛИ-НЕ, элемент И-НЕ, второй элемент ИЛИ и элемент ИЛИ-НЕ с увеличенной задержкой, причем выход шестого элемента И соединен с первым входом первого элемента ИЛИ-НЕ и входом элемента НЕ с увеличенной задержкой, выход которого соединен с вторым входом первого элемента ИЛИ-НЕ, выход которого соединен с S- входом RS-триггера, R-вход которого соединен с выходом второго элемента

ИЛИ-НЕ, первый вход которого соединен с выходом пятого элемента И и с первым входом элемента ИЛИ-НЕ с увеличенной задержкой, выход которого соединен с

вторым входом второго элемента ИЛИ-НЕ, третий вход которого соединен с выходом четвертого элемента И и с вторым входом элемента ИЛИ-НЕ с увеличенной задержкой, четвертый вход первого элемента ИЛИ

соединен с выходом седьмого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с первыми входами третьего элемента И и элемента И-НЕ, выход которого соединен с третьим входом седьмого элемента И, вторые входы второго элемента ИЛИ и элемента И-НЕ соединены с первым входом первого элемента И.

.Ъ

| Реверсивный регистр сдвига | 1983 |

|

SU1176385A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Многофункциональный регистр | 1986 |

|

SU1411828A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-01-30—Публикация

1988-09-26—Подача