1

(21) 4683259/24

(2.2) 16.03.89

(46) 28.02.91. Бюл. № 8

(71)Специальное конструкторское бюро вмчислительной техники Института кибернетики АН ЭССР

(72)Х.И.Хаак, А.Э.Ойнус и П.М.Авер

(53)681.326.7 (088.8)

(56)Авторское свидетельство СССР № 1108452, кп. G 06 F 11/16, 1984.

(54)СИГНАТУРНЫЙ АНАЛИЗАТОР

(57)Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля цифровых блоков. Целью изобретения является увеличение достоверности контроля. Сигнатурный анализатор содержит два компаратора 1,2 два формирователя 3.4 сигнатур, блок индикации 5 и делитель напряжения, выполненный на резисторах 6.7. Сигнатурный анализатор позволяет контролировать устройства с тремя состояниями выходов, уточняя при этом характер имеющихся неисправностей. 1 ил. 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1988 |

|

SU1624459A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Сигнатурный анализатор | 1987 |

|

SU1589278A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

| Сигнатурный анализатор | 1982 |

|

SU1108452A1 |

| Сигнатурный анализатор | 1989 |

|

SU1649547A1 |

| Сигнатурный анализатор | 1986 |

|

SU1343413A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

(Л

о со

СП

4ь

СО

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых узлов, в том числе для узлов, имеющих выходы с тремя состояниями.

Цель изобретения - увеличение достоверности контроля.

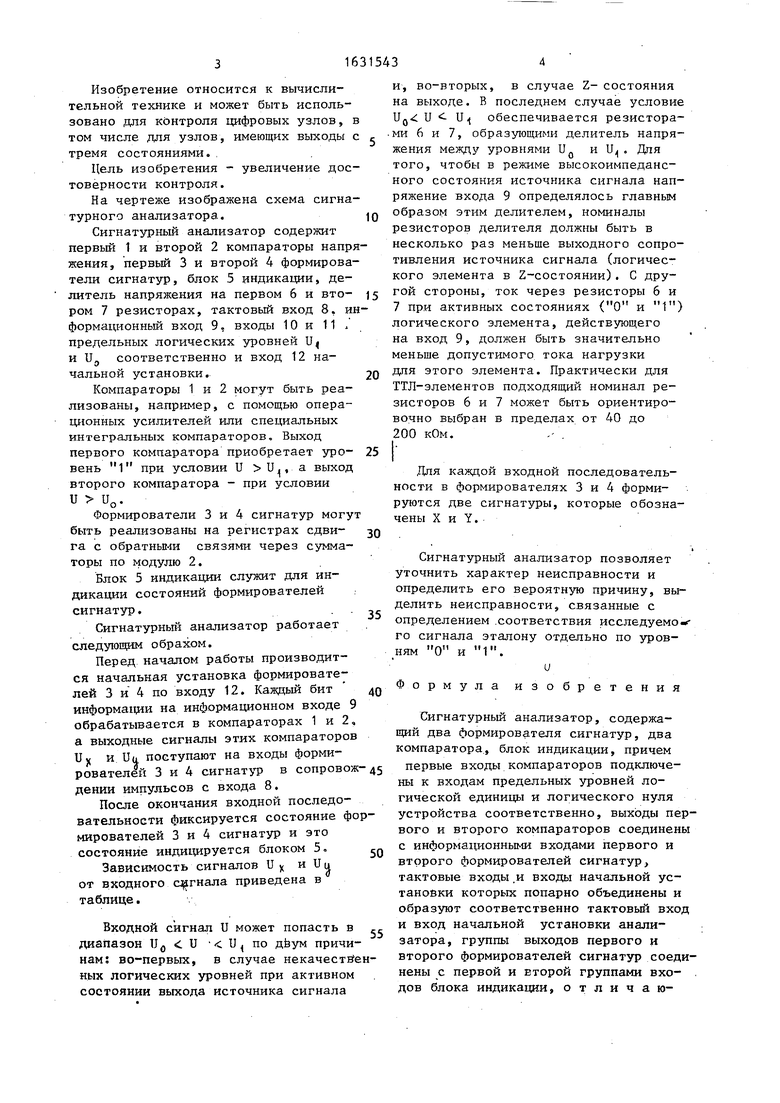

На чертеже изображена схема сигнатурного анализатора.

Сигнатурный анализатор содержит первый 1 и второй 2 компараторы напряжения, первый 3 и второй 4 формирователи сигнатур, блок 5 индикации, делитель напряжения на первом 6 и вто- ром 7 резисторах, тактовый вход 8. информационный вход 9. входы 10 и 11 , предельных логических уровней U и U. соответственно и вход 12 наУ

чальной установки.

Компараторы 1 и 2 могут быть реализованы, например, с помощью операционных усилителей или специальных интегральных компараторов. Выход первого компаратора приобретает уро-

вень 1 при условии U U, а выход второго компаратора - при условии U U0.

Формирователи 3 и 4 сигнатур могут быть реализованы на регистрах сдвига с обратными связями через сумматоры по модулю 2.

Блок 5 индикации служит для индикации состояний формирователей сигнатур.

Сигнатурный анализатор работает следующим обрахом.

Перед началом работы производится начальная установка формирователей 3 и 4 по входу 12. Каждый бит информации на информационном входе 9 обрабатывается в компараторах 1 и 2, а выходные сигналы этих компараторов U) и U а поступают на входы формирователей 3 и 4 сигнатур в сопровож дении импульсов с входа 8.

После окончания входной последовательности фиксируется состояние фомирователей 3 и 4 сигнатур и это состояние индицируется блоком 5. Зависимость сигналов U х и U от входного сигнала приведена в таблице.

Входной сигнал U может попасть в

диапазон U0 . U U по двум причинам; во-первых, в случае некачественных логических уровней при активном состоянии выхода источника сигнала

5

и, во-вторых, в случае Z- состояния на выходе. В последнем случае условие UQ U - U.) обеспечивается резисторами 6 и 7, образующими делитель напряжения между уровнями Ufl и U,, . Для того, чтобы в режиме высокоимпеданс- ного состояния источника сигнала напряжение входа 9 определялось главным образом этим делителем, номиналы резисторов делителя должны быть в несколько раз меньше выходного сопротивления источника сигнала (логического элемента в Z-состоянии). С другой стороны, ток через резисторы 6 и 7 при активных состояниях и 1) логического элемента, действующего на вход 9, должен быть значительно меньше допустимого тока нагрузки для этого элемента. Практически для ТТЛ-элементов подходящий номинал резисторов 6 и 7 может быть ориентировочно выбран в пределах от 40 до 200 кОм.

Для каждой входной последовательности в формирователях 3 и 4 формируются две сигнатуры, которые обозначены X и Y.

Сигнатурный анализатор позволяет уточнить характер неисправности и определить его вероятную причину, выделить неисправности, связанные с определением соответствия исследуемо- - го сигнала эталону отдельно по уровням О и 1.

и

изобретения

Формула

Сигнатурный анализатор, содержащий два формирователя сигнатур, два компаратора, блок индикации, причем

первые входы компараторов подключены к входам предельных уровней логической единицы я логического нуля устройства соответственно, выходы первого и второго компараторов соединены с информационными входами первого и второго формирователей сигнатур, тактовые входы .и входы начальной установки которых попарно объединены и образуют соответственно тактовый вход и вход начальной установки анализатора, группы выходов первого и второго формирователей сигнатур соединены с первой и второй группами входов блока индикации, отличающ и и с я тем, что, с целью увели- Г I чения достоверности контроля, он со- и UX U

держит делитель напряжения, первый

и второй входы которого подключеныU U0 О О

к входам предельных уровней логичес-U U U 0 1

кой единицы и логического нуля COOT- °

ветственно, а выход объединен с вто- 1ШИ высокорыми входами первого и второго ком-икпедансное

параторов и образует информационный ю состояние)

вход анализатора.U U, 1 1

Авторы

Даты

1991-02-28—Публикация

1989-03-16—Подача