Фиг.1

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики цировых устройств, содержащих элементы с тремя состояниями.

Цель изобретения - увеличение бысродействия и повышение достоверности контроля путем устранения зависимости преобразования сигнала третьего состояния в нулевой или единичный от значащих (нулевых и единичных) элементов исследуемой последовательности в предыдущих тактах работы, предшествующих появлению ана- лизируемого третьего состояния

На фиг. 1 приведена структурная схема сигнатурного анализатора; на фиг. 2 - схема шифратора.

Сигнатурный анализатор (фиг.1) содержит тактовый вход 1, информационный вход 2, вход 3 режима, группу 4 ус тановачных входов, вход 5 сброса, генератор 6 псевдослучайных последовательностей, элемент 7 за- держки, формирователь 8 сигнатур, блок 9 индикации, шифратор 10, элемент ИСКПНгёАЮЩЕЕ ИЛИ 11 , элемент ИЛИ 12 и коммутатор 13.

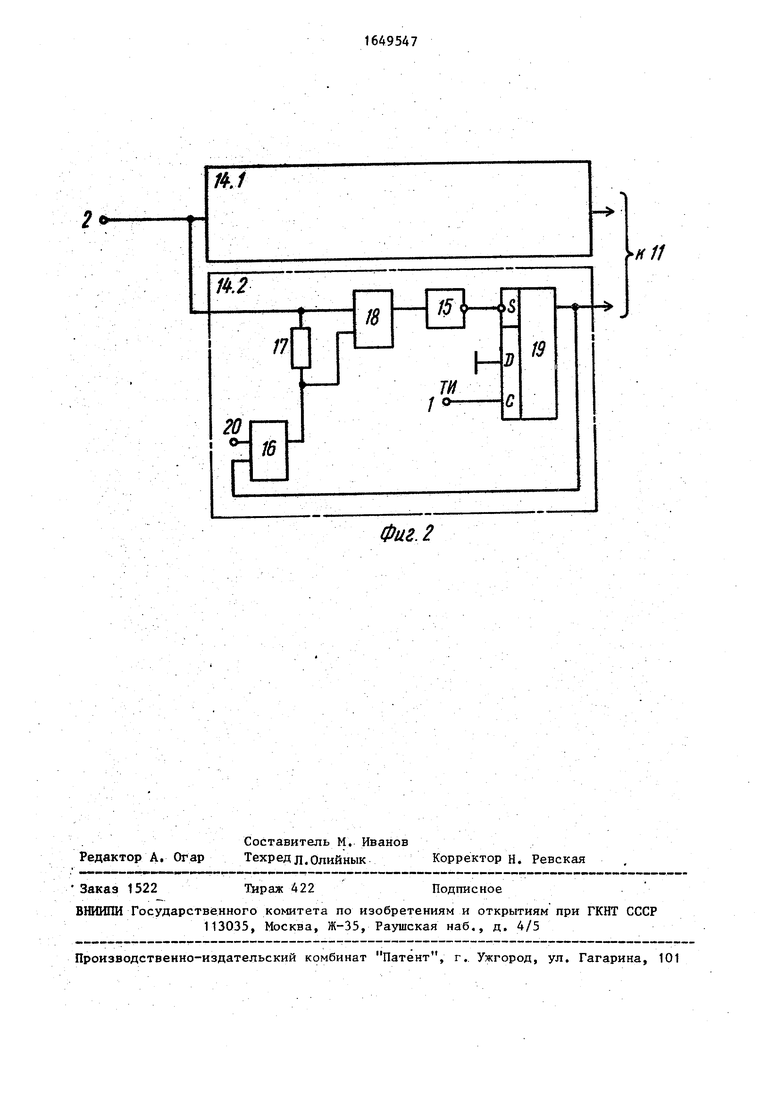

Шифратор (фиг. 2) образуют два анализатора 14.1 и 14.2 сигналов, каждый из которых содержит элемент НЕ 15, буферный элемент 16 с тремя состояниями, резистор 17, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18, триггер 19 и вход 20о Вход 20 анализатора 14.1 соединен с шиной нулевого уровня, вход 20 анализатора 14„2 - с шиной единичного уровня,

В качестве буферного элемента 16 с тремя состояниями может быть использован элемент, значение логического уровня на выходе которого равно значению логического уровня на его информационном входе при условии, что на управляющий вход устройства .подан сигнал логического нуля, в противном случае выход принимает высокоимпедансное состояние, например буферный усилитель К155 ЛП8.

Перед началом работы производится установка устройства в исходное состояние: на вход 3 сигнатурного анализатора подается логическая единица затем на установочные входы 4 подает ся некоторый двоичный код, который может быть любым, отличным от нулевого, затем на вход 5 подается положительный импульс, по которому проис

0 5

5

0

0

ходит параллельная запись в генератор 6 кода с установочных входов 4, этот же импульс поступает на вход начальной установки формирователя 8 сигнатур и устанавливает сдвиговый регистр формирователя 8 сигнатур в начальное состояние. Затем на вход 3 сигнатурного анализатора подается логический ноль. На этом начальная установка сигнатурного анализатора

заканчивается.

i

Информационный вход сигнатурного анализатора подсоединяется к контролируемой точке цифрового устройства. При поступлении на тактовый вход сигнатурного анализатора тактового импульса, тактирующего поступившую на вход 2 сигнатурного анализатора информацию о состоянии контролируемой точки, на выходах первого и второго анализаторов 14.1 и 14.2 устанавливаются логические уровни в соответствии с сигналом на информационном входе сигнатурного анализатора . Если на информационном входе сигнатурного анализатора присутствует логический ноль или активная логическая единица, то на выходах первого и второго анализаторов 14.1 и 14.2 устанавливают различные логические уровни, если третье состояние Z, то на выходах первого и второго анализаторов 14.1 и 14.2 устанавливаются уровни логической единицы. В случае установки различных логических уровней на выходах первого и второго анализаторов 14.1 и 14.2. на выходе элемента 18 присутствует уровень логической единицы. Логичес кая единица с выхода элемента 18 .поступая - на управляющий вход коммутатора 13, разрешает прохождение сигнала с информационного входа сигнатурного анализатора на информационный вход формирователя 8 сигнатур. Если уровни на выходах первого и второго анализатора 14.1 и 14.2 принимают значения логической единицы, то на выходе элемента 18 устанавливает уровень логического нуля, который разрешает прохождение через коммутатор 13 сигнала с выхбда генератора 6 на информационный вход формирователя 0 сигнатур Таким образом, если на информационном входе сигнатурного анализатора присутству-

ют уровни логического нуля или активной логической единицы, то они через коммутатор 13 поступают на информационный вход формирователя 8 сигнатур и записываются в него тактовым сигналом, задержанным элементом 7 задержки. Если на информационном входе сигнатурного анализатора присутствует третье состояние Z, то на информационный вход формирователя 8 сигнатур поступает сигнал с выхода генератора 6, который также записывается задержанным тактовым сигналом. Необходимость использования элемента 7 задержки обусловлена временем срабатывания анализатора 14, элемента 18 и коммутатора 13,

Включение в состав сигнатурного анализатора генератора 6 .позволяет повысить достоверность контроля за счет независимости способа перекодировки третьего состояния Z от значения элемента исследуемой троичной последовательности, поступившего на вход в предыдущий такт, что имеет место в известном устройстве. В случае использования известного устройства две последовательности, например, такие, как 1 OZ 0 и 1 01 0, будут нераопичимы с вероятностью, равной единице. При применении предлагаемого сигнатурного анализатора для распознавания указанных последовательностей вероятность их различения Р 0,5. Предлагаемый сигнатурный анализатор позволяет обеспечить повышение достоверности в случае априорной неопределенности о типе возможной неисправности, имеющей место в подавляющем большинстве случаев на практике.

Формула изобретения

Сигнатурный анализатор, содержа- щий шифратор, коммутатор, формирователь, сигнатур, блок индикации и элемент ИЛИ. причем вход шифратора является информационным входом анализатора, выход коммутатора соединен с информационным входом формирователя сигнатур, группа выходов которого подключена к группе входов блока ин5

0

5

0

5

0

дикации, отличающийся тем, что, с целью увеличения быстродействия и повышения достоверности контроля, он дополнительно содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, генератор псевдослучайных последовательностей и элемент задержки, вход которого объединен с первмм входом элемента ИЛИ и является тактовым входом анали- з атора, а выход подключен к тактовому входу формирователя сигнатур, вход начальной установки которого объединен с вторым входом элемента ИЛИ, и является входом сброса анализатора, первый и второй информационные входы коммутатора подключены соответственно к информационному входу анализатора и выходу генератора псевдослучайных последовательностей, тактовый вход которого подключен к выходу элемента ИЛИ, вход задания режима и группа информационных вхбдов генератора псевдослучайных последовательностей образуют соответственно вход задания режима и группу установочных входов анализатора, управляющий вход коммутатора подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого подключены к выходам тиф ратора.

ft.2

f

/8

15

W

И

19

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1990 |

|

SU1748154A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624459A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1354195A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Сигнатурный анализатор | 1987 |

|

SU1589278A1 |

d

16

Фиг. 2

| Электроника, 1977, № 5, с.23-33 | |||

| Сигнатурный анализатор | 1980 |

|

SU903898A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-15—Публикация

1989-05-24—Подача