еО

&EF&

as

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для формирования остатка по произвольному модулю от числа | 1990 |

|

SU1837401A1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2015 |

|

RU2616153C2 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

Изобретение относится к вычислительной технике и может быть использовано при контроле арифметических узлов. Цель изобретения - расширение области применения устройства. Устройство содержит входной триггер 4, рабочие триггеры 5, б, счетный триггер 7, коммутаторы 8, 14, элементы И-НЕ 9-11, элементы И-ИЛИ-НЕ 12, 13 коммутатора 8, элементы И-ИЛИ-НЕ 15, 16 коммутатора 14, выходные триггеры 17, 18. Устройство обеспечивает контроль последовательного числа в дополнительном коде. 2 ил., 2 табл.

Oi

Kfspfe

Изобретение относится к вычисли- - ельной технике и может быть использовано при контроле работы арифметических узлов.

Цель изобретения - расширение обасти применения устройства,

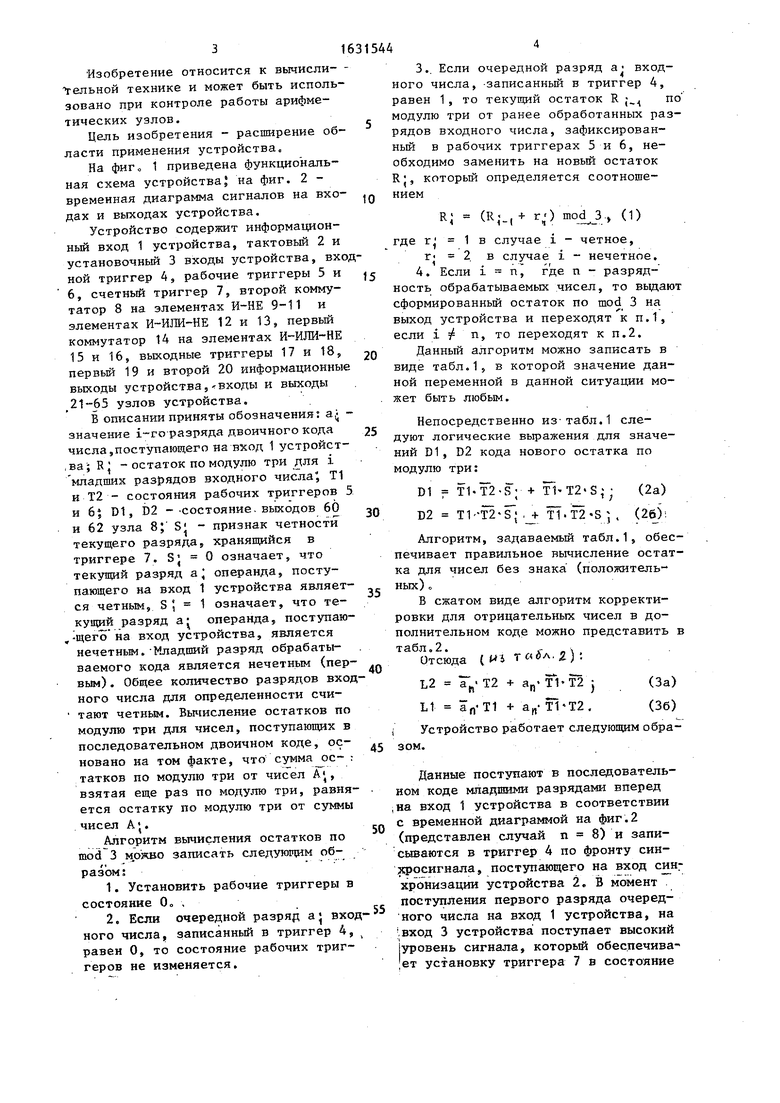

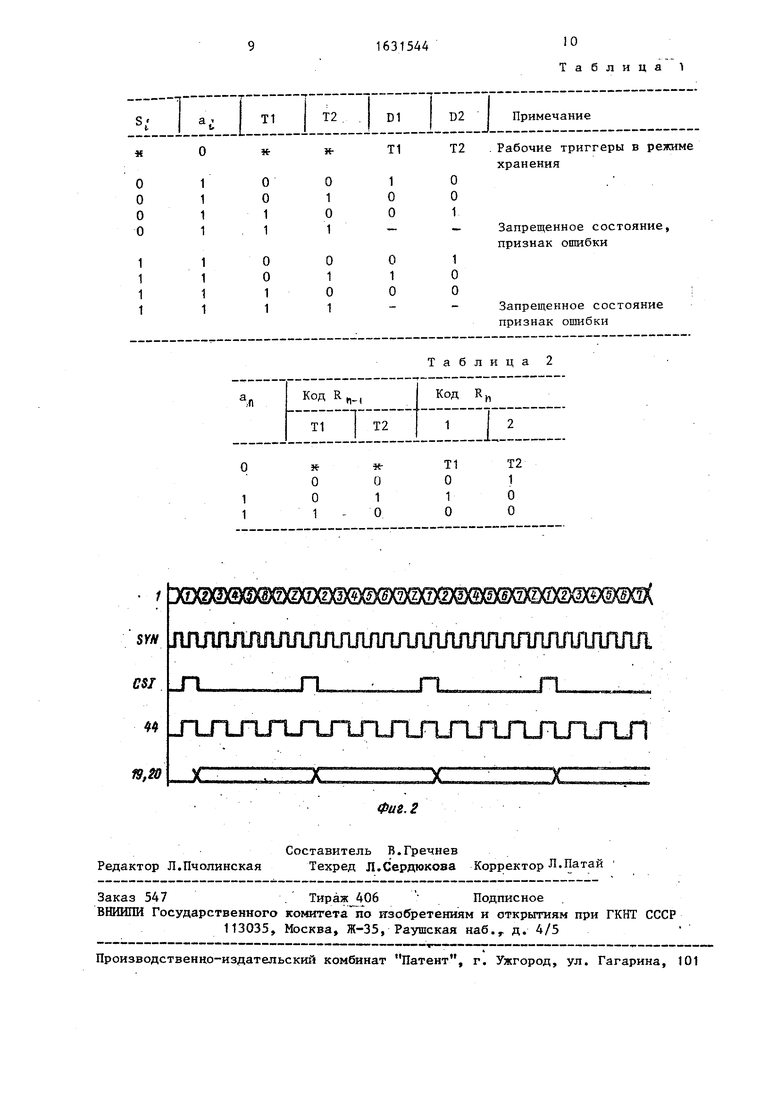

На фиг о 1 приведена функциональная схема устройстваJ на фиг. 2 - временная диаграмма сигналов на вхоах и выходах устройства.

Устройство содержит информационный вход 1 устройства, тактовый 2 и установочный 3 входы устройства, входной триггер 4, рабочие триггеры 5 и 6, счетный триггер 7, второй коммутатор 8 на элементах И-НЕ 9-11 и элементах И-ИЛИ-НЕ 12 и 13, первый коммутатор 14 на элементах И-ИЛИ-НЕ 15 и 16, выходные триггеры 17 и 18, первый 19 и второй 20 информационные выходы устройства,-входы и выходы узлов устройства.

В описании приняты обозначения: а - начение 1-го разряда двоичного кода исла,поступающего на вход 1 устройста; R - остаток по модулю три для i младших разрядов входного числа , Т1 и Т2 - состояния рабочих триггеров 5 и 6} D1, D2 - Состояние выходов 60 и 62 узла 8; S - признак четности текущего разряда, хранящийся в триггере 7. Sj 0 означает, что текущий разряд а операнда, поступающего на вход 1 устройства является четным, означает, что текущий разряд а операнда, поступаюего на вход устройства, является нечетным.Младший разряд обрабатываемого кода является нечетным (первым) . Общее количество разрядов входного числа для определенности счи- тают четным. Вычисление остатков по модулю три для чисел, поступающих в последовательном двоичном коде, основано на том факте, что сумма рс- г татков по модулю три от чисел А (, взятая еще раз по модулю три, равняется остатку по модулю три от суммы чисел А.

Алгоритм вычисления остатков по mod 3 можно записать следующим образом:

2, Если очередной разряд а| вход ного числа, записанный в триггер 4, равен 0, то состояние рабочих триггеров не изменяется.

R; (R, -,+ г,) ш°1.з (D

5

0

5

0

1в случае i - четное,

2в случае i - нечетное.

где г- г-

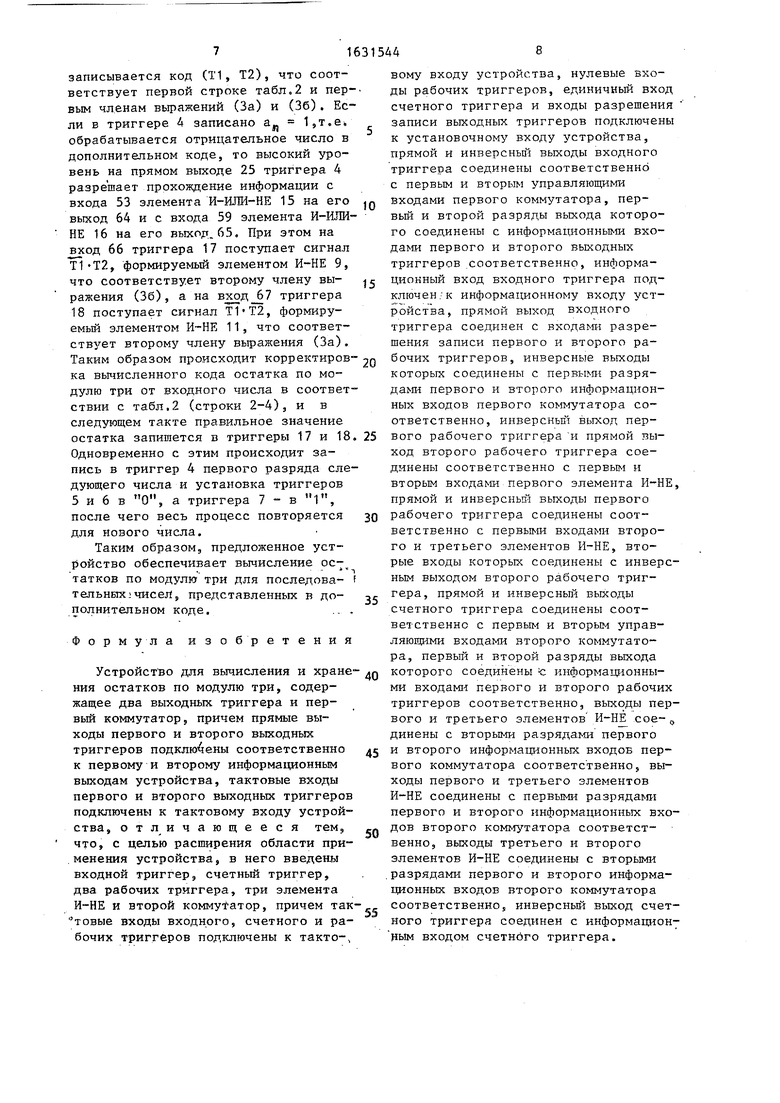

Данный алгоритм можно записать в виде табл.1., в которой значение данной переменной в данной ситуации может быть любым.

Непосредственно из табл.1 следуют логические выражения для значений D1, D2 кода нового остатка по модулю три:

D1 f T1-T2-S D2 T1-T2-S

+ TbT2«S

i ;

+

T1.T2-S

(2а) (26)

Алгоритм, задаваемый табл.1, обеспечивает правильное вычисление остатка для чисел без знака (положительных) о

В сжатом виде алгоритм корректировки для отрицательных чисел в дополнительном коде можно представить в табл.2.

Отсюда (Hi т«ол. 2) ;

п

aft- 12 + а„ ТМ2 а„-Т1

)

+ а„- ТМ2.

(За) (36)

Устройство работает следующим обра45 зон.

50

55

Данные поступают в последовательном коде младшими разрядами вперед ,на вход 1 устройства в соответствии с временной диаграммой на фиг.2 (представлен случай п 8) и записываются в триггер 4 по фронту синхросигнала, поступающего на вход синг хронизации устройства 2. В момент поступления первого разряда очередного числа на вход 1 устройства, на вход 3 устройства поступает высокий уровень сигнала, который обеспечивав ет установку триггера 7 в состояние

записывается код (Т1, Т2), что соответствует первой строке табл.2 и первым членам выражений (За) и (Зб). Если в триггере 4 записано ап 1,т.е. обрабатывается отрицательное число в дополнительном коде, то высокий уровень на прямом выходе 25 триггера 4 разрешает прохождение информации с входа 53 элемента И-ИЛИ-НЕ 15 на его выход 64 и с входа 59 элемента И-ИЛИ- НЕ 16 на его выход. 65, При этом на вход 66 триггера 17 поступает сигнал Т T2, формируемый элементом И-НЕ 9, что соответствует второму члену выражения (36), а на триггера 18 поступает сигнал , формируемый элементом И-НЕ 11, что соответствует второму члену выражения (За). Таким образом происходит корректиров- ка вычисленного кода остатка по модулю три от входного числа в соответствии с табл,2 (строки 2-4), и в следующем такте правильное значение остатка запишется в триггеры 17 и 18 Одновременно с этим происходит запись в триггер 4 первого разряда следующего числа и установка триггеров 5 и 6 в О, а триггера 7 - в 1, после чего весь процесс повторяется для нового числа.

Таким образом, предложенное устройство обеспечивает вычисление ос-т татков по модулю три для последова- тельных;чисел„ представленных в дополнительном коде.. .

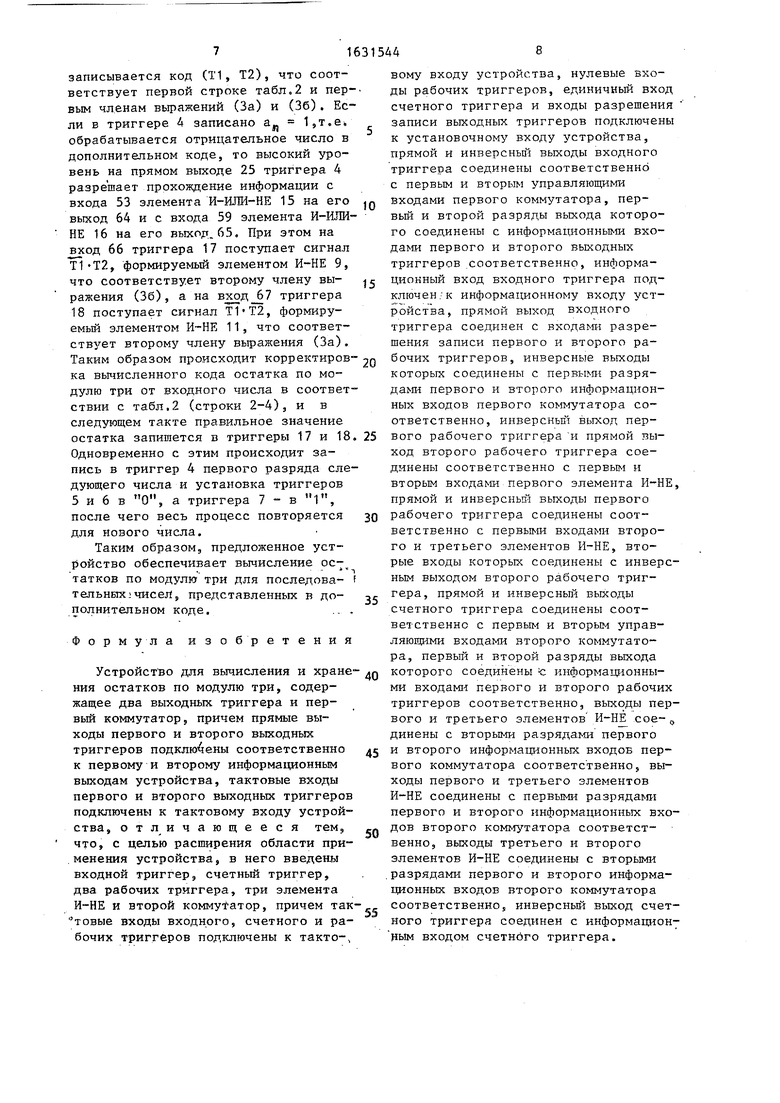

Формула изобретения

Устройство для вычисления и хране ния остатков по модулю три, содержащее два выходных триггера и первый коммутатор э причем прямые выходы первого и второго выходных триггеров подключены соответственно к первому и второму информационным выходам устройства, тактовые входы первого и второго выходных триггеров подключены к тактовому входу устройства, отличающееся тем, что, с целью расширения области применения устройства, в него введены входной триггер, счетный триггер, два рабочих триггера, три элемента И-НЕ и второй коммутатор, причем тактовые входы входного, счетного и рабочих триггеров подключены к такто-.

0

5

Q 5

Q

0

5

5

0

5

вому входу устройства, нулевые входы рабочих триггеров, единичный вход счетного триггера и входы разрешения записи выходных триггеров подключены к установочному входу устройства, прямой и инверсньй выходы входного триггера соединены соответственно с первым и вторым управляющими входами первого коммутатора, первый и второй разряды выхода которого соединены с информационными входами первого и второго выходных триггеров соответственно, информационный вход входного триггера подключен к информационному входу устройства, прямой выход входного триггера соединен с входами разрешения записи первого и второго рабочих триггеров, инверсные выходы которых соединены с первыми разрядами первого и второго информационных входов первого коммутатора соответственно, инверсньй выход первого рабочего триггера и прямой выход второго рабочего триггера соединены соответственно с первым и вторым входами первого элемента И-НЕ, прямой и инверсный выходы первого рабочего триггера соединены соответственно с первыми входами второго и третьего элементов И-НЕ, вторые входы которых соединены с инверсным выходом второго рабочего триггера, прямой и инверсньй выходы счетного триггера соединены соответственно с первым и вторым управляющими входами второго коммутатора, первый и второй разряды выхода которого соединены с информационными входами первого и второго рабочих триггеров соответственно, выходы первого и третьего элементов И-НЕ сое-0 динены с вторыми разрядами первого и второго информационных входов первого коммутатора соответственно, выходы первого и третьего элементов И-НЕ соединены с первыми разрядами первого и второго информационных входов второго коммутатора соответственно, выходы третьего и второго элементов И-НЕ соединены с вторыми разрядами первого и второго информационных входов второго коммутатора соответственноs инверсньй выход счетного триггера соединен с информацион- ным входом счетного триггера.

516

1, триггеров 5 и 6 - в состояние О и разрешает запись в выходные триггеры 17 и 18 вычисленного остатка по модулю 3 для предыдущего числа. Установка триггеров 5, 6 и 7 происходит одновременно с записью 1-го разряда очередного числа в триггер 4 по фронту синхросигнала. Коммутатор 8, элементы И-НЕ 9-11 реализуют строки с 2-й по 9-ю табл.1, т.е. формируют сигналы D1, D2 в соответствии с выражением (2).

Если триггер 7 находится в состоянии 1, т.е. в триггер 4 записался нечетный разряд входного числа (1-й, 3-й и т.д.), то низкий уровень на выходе 47 триггера 7 запрещает прохождение информации с входа 57 элемента И-ИЛИ-НЕ 12 на его выход 60 и с входа 55 элемента И-ИЛИ-НЕ 13 на его выход 62, а высокий уровень на выходе 44 триггера 7 разрешает прохождение информации с входа 52 элемента И-ИЛИ-НЕ 12 на его выход 60 и далее на вход 61 триггера 5 и разрешает прохождение информации с входа 58 элемента И-ИЛИ-НЕ 13 на его выход 62 и далее на вход 63 триггера 6 В результате этого на вход 6Д триггера 5 проходит сигнал Т1, Т2, формируемый элементом И-НЕ и дважды про инвертированный на выходе элемента И-НЕ 9 и на выходе элемента И-ИЛИ-НЕ 12, что соответствует второму члену выражения (2а). На триггера 6 проходит сигнал Т1, Т2, формируемый элементом И-НЕ 11 и дважды проин вертированный, что соответствует второму члену выражения (26). Триггер 7 по каждому очередному фронту синхросигнала переключается в противоположное состояние, что обеспечивается обратной связью с инверсного выхода 47 триггера 7 на его вход 48. Если триггер 7 находится в состоянии О, т.е. в триггер 4 записался четный разряд входного числа (2-й,4-й ит.д.) то низкий уровень на выходе 44 триг- гера 7 запрещает прохождение информации с входа 58 элемента И-ИЛИ-НЕ . 13 на его выход 62 и с входа 52 элемента И-ИЛИ-НЕ 12 на его выход 60, а высокий уровень на выходе 47 триггера 7 разрешает прохождение информации с входа 57 элемента И-ИЛИ-НЕ 12 на его выход 60 и далее на вход 61 рабочего триггера 5 и разрешает прохождение информации с входа 55

5446

элемента И-ИЛИ-НЕ 13 на его выход 62 и далее на вход 63 триггера 6. В результате этого 61 триггера 5 поступает сигнал Т1 Т2, формируемый элементом И-НЕ 11, что соответствует первому члену выражения (2а), на триггера 6 поступает сиг- нал Т1 Т2, сформированный элементом

Q И-НЕ 10, что соответствует первому члену выражения (26). Сформированные коммутатором 8 сигналы записываются в рабочие триггеры 5 и 6-в том случае, если очередной разряд вход5 ного числа, записанный в триггер 4, равен 1. В этом случае высокий уровень с выхода 25 триггера 4 поступает на входы 26 разрешения записи триггеров 5 и 6, что обеспечивает их обновление в соответствии со строками 2-9 табл.1. Если очередной разряд входного числа, записанный в триггер 4, равен О, то низкий уровень, поступающий с выхода 25 триггера 4 на входы 26 разрешения- записи триггеров 5 и 6-, блокирует прием новой информации в эти триггеры, и в них сохраняется код остатка по модулю 3, вычисленный в предыдущем такте (реализуется строка 1 табл.1). Последний (знаковый) разряд обрабатываемого числа записывается в триггер 4, после чего в следующем такте на установочный вход 3 устройства поступает высокий уровень сигнала установки, который проходит на входы 24 разрешения записи выходных триггеров 17 и 18 и разрешает прием в них информации с выходов 64 и 65 блока обработки знака (фиг.2). При этом если

0

5

0

5

0

в триггере 4 записано ап 0, т.е.

срабатывается положительное число, то высокий уровень на инверсном выходе 29 триггера 4 разрешает прохожде5 ние информации с входа 37 элемента И-ИЛИ-НЕ 15 на его выход 64 и с входа 43 элемента И-ИЛИ-НЕ 16 на его выход 65. Соответственно на вход 66 триггера 17 поступает с выхода триг-

Q гера 5 уровень, соответствующий

первому разряду Т1 вычисленного кода остатка по модулю 3 для мантиссы обрабатываемого числа, на вход 67 триггера 18 поступает с выхода триггера 6 уровень, соответствующий второму разряду Т2 вычисленного кода остатка ,|ПО модулю три для мантиссы обрабатЫ- даемого числа, в результате чего в следующе м такте в триггеры 17 и 18

5

SYN

ЛЛПШШШШШШШ

CSI

JTL

TL

44

J JTJljajnjnj JTJT

Составитель В.Гречнев Редактор Л.Пчолинская Техред Л„Сердюкова Корректор Л.Патай

Заказ 547Тираж АОб Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб.,, д. 4/5

Таблица 1

JT

n

Фаг. 2

| Устройство для формирования остатка по модулю три | 1984 |

|

SU1211733A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования и хранения вычетов по модулю три | 1986 |

|

SU1343415A1 |

Авторы

Даты

1991-02-28—Публикация

1989-03-30—Подача