о

GJ

§

о

Изобретение относится к радиотехнике и может быть использовано в приемопередающей и измерительной аппаратуре.

Цель изобретения - повышение частотной чувствительности на частотах, кратных входному числу.

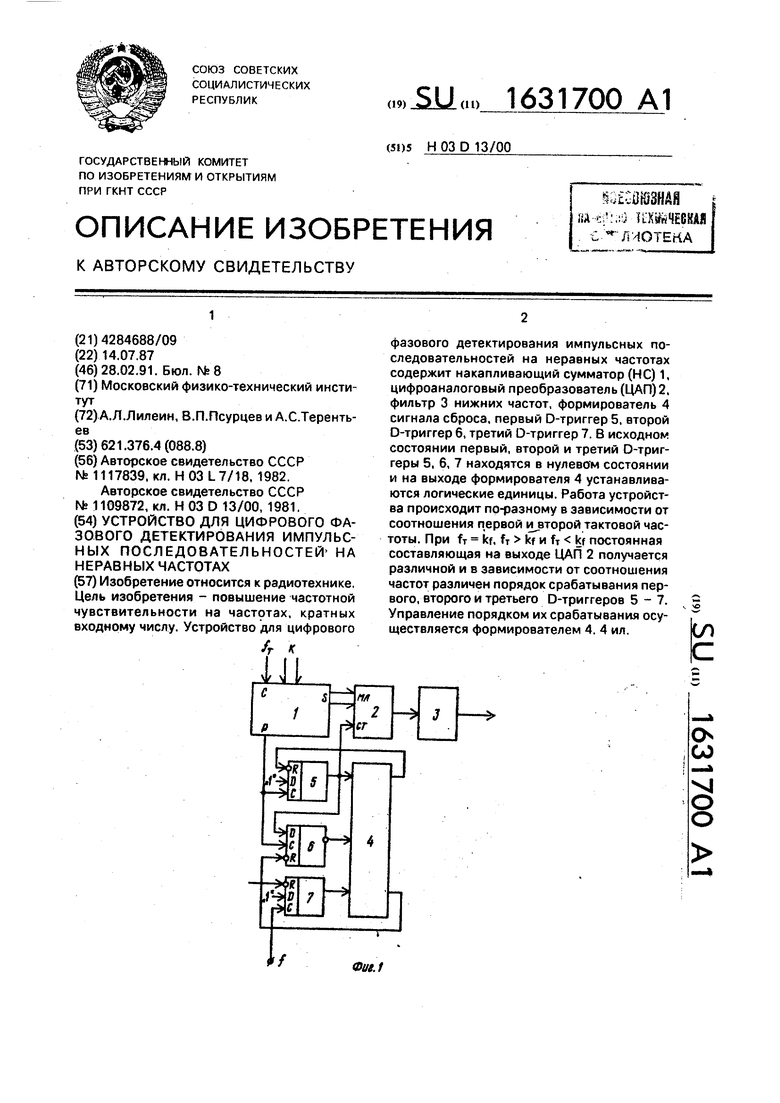

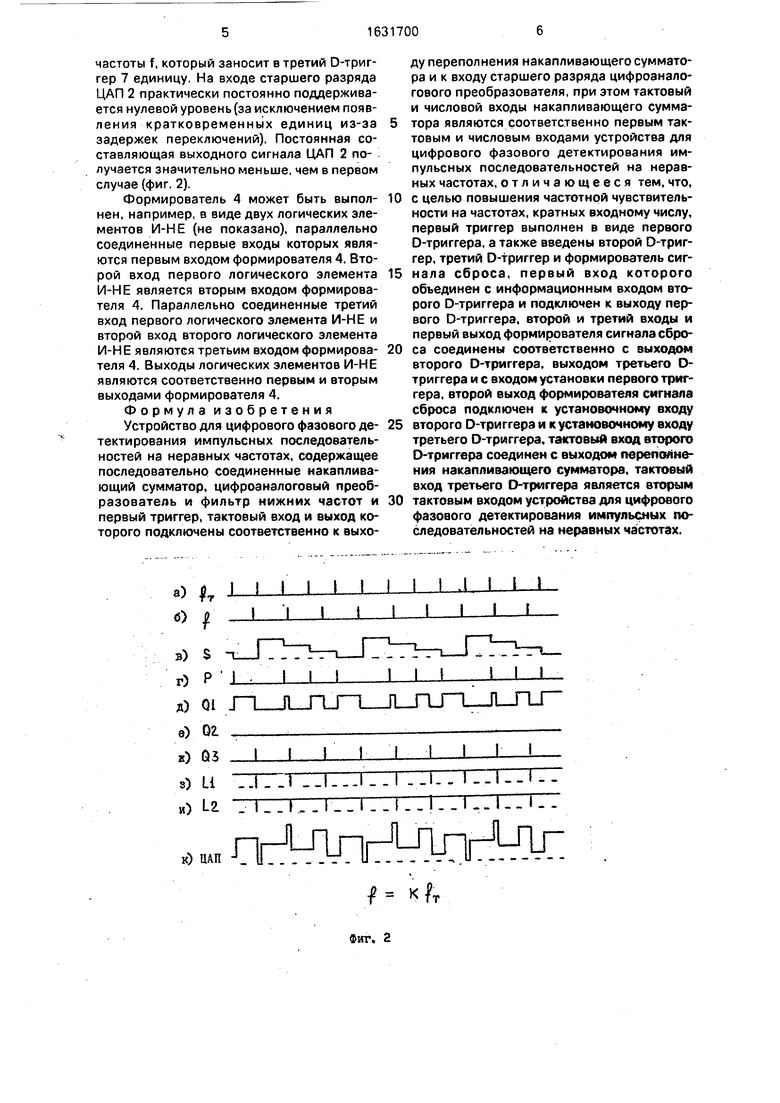

На фиг. 1 изображена структурная электрическая схема предложенного устройства; на фиг. 2 - временные диаграммы работы для случая f k . ft; на фиг. 3 - то же. для случая, f k fT; на фиг. 4 - то же, для случая f k fT.

Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах содержит накапливающий сумматор (НС) 1, цифроа- налоговый преобразователь (ЦАП) 2, фильтр 3 нижних частот, формирователь 4 сигнала сброса, первый О-триггер 5, второй D-триг- гер 6, третий D-триггер 7.

Устройство работает следующим образом.

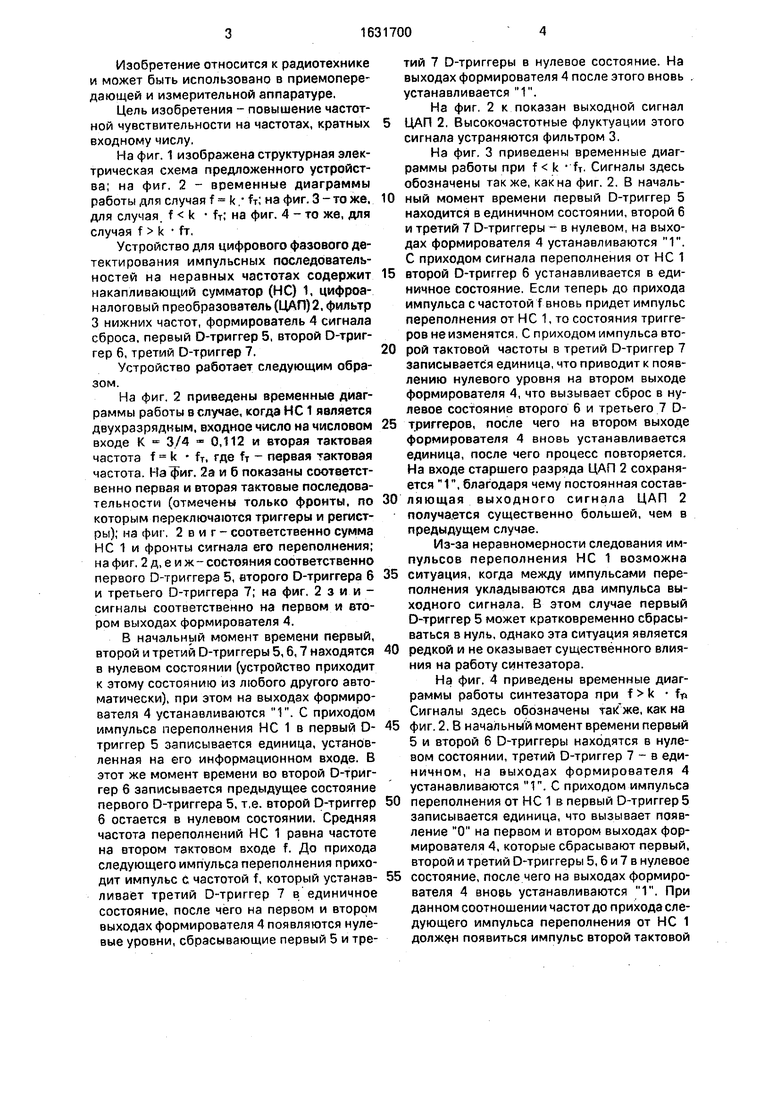

На фиг. 2 приведены временные диаграммы работы в случае, когда НС 1 является двухразрядкым. входное число на числовом входе К 3/4 0,112 и вторая тактовая частота f k fT, где ft - первая тактовая частота. НэТриг. 2а и б показаны соответственно первая и вторая тактовые последовательности (отмечены только фронты, по которым переключаются триггеры и регистры); на фиг. 2 в и г - соответственно сумма НС 1 и фронты сигнала его переполнения; на фиг. 2 д, е и ж- состояния соответственно первого D-триггера 5, второго D-триггера 6 и третьего D-триггера 7; на фиг. 2 з и и - сигналы соответственно на первом и втором выходах формирователя 4.

В начальный момент времени первый, второй и третий D-трнггеры 5,6,7 находятся в нулевом состоянии (устройство приходит к этому состоянию из любого другого автоматически), при этом на выходах формирователя 4 устанавливаются 1. С приходом импульса переполнения НС 1 в первый D- триггер 5 записывается единица, установленная на его информационном входе. В этот же момент времени во второй D-триггер б записывается предыдущее состояние первого D-триггера 5, т.е. второй D-триггер 6 остается в нулевом состоянии. Средняя частота переполнений НС 1 равна частоте на втором тактовом входе f. До прихода следующего импульса переполнения приходит импульс с частотой f, который устанавливает третий D-триггер 7 в единичное состояние, после чего на первом и втором выходах формирователя 4 появляются нулевые уровни, сбрасывающие первый 5 и третий 7 D-триггеры в нулевое состояние. На выходах формирователя 4 после этого вновь устанавливается 1.

На фиг. 2 к показан выходной сигнал

ЦАП 2, Высокочастотные флуктуации этого сигнала устраняются фильтром 3.

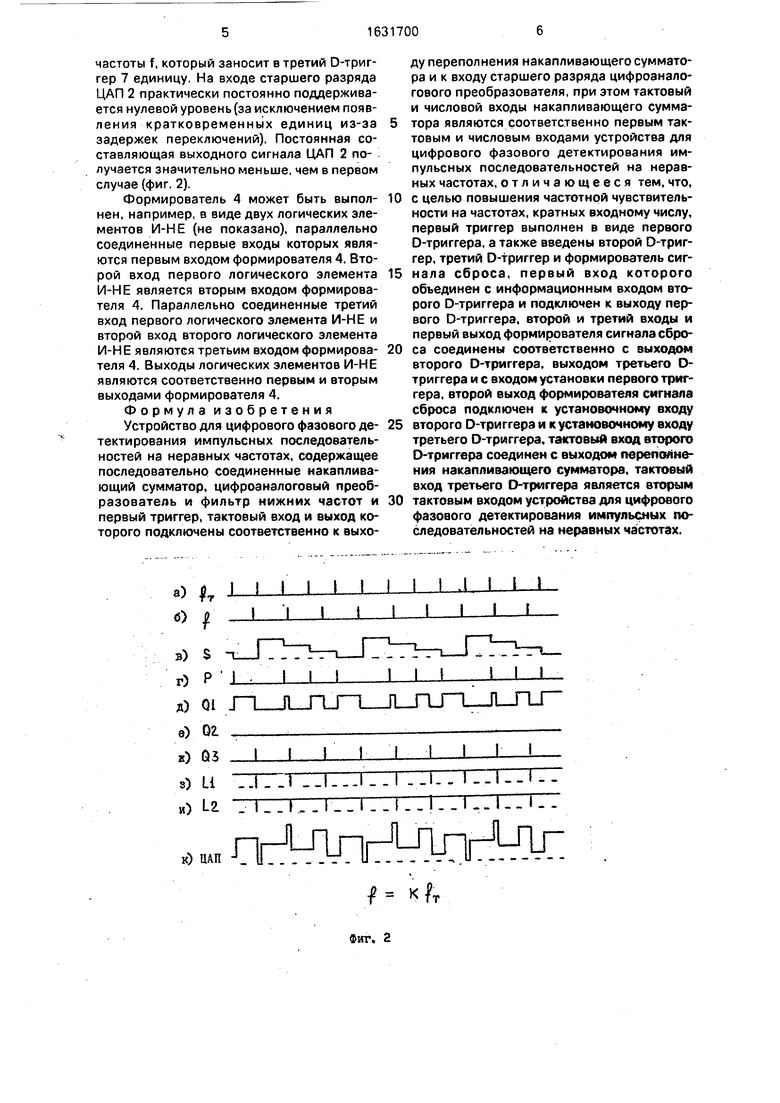

На фиг. 3 приведены временные диаграммы работы при f k fT. Сигналы здесь обозначены также, как на фиг. 2. В начальный момент времени первый D-триггер 5 находится в единичном состоянии, второй 6 и третий 7 D-триггеры - в нулевом, на выходах формирователя 4 устанавливаются 1. С приходом сигнала переполнения от НС 1

второй D-триггер б устанавливается в единичное состояние. Если теперь до прихода импульса с частотой f вновь придет импульс переполнения от НС 1, то состояния триггеров не изменятся, С приходом импульса второй тактовой частоты в третий D-триггер 7 записывается единица, что приводит к появлению нулевого уровня на втором выходе формирователя 4, что вызывает сброс в нулевое состояние второго 6 и третьего 7 Dтриггеров, после чего на втором выходе формирователя 4 вновь устанавливается единица, после чего процесс повторяется. На входе старшего разряда ЦАП 2 сохраняется 1, благодаря чему постоянная составляющая выходного сигнала ЦАП 2 получается существенно большей, чем в предыдущем случае.

Из-за неравномерности следования импульсов переполнения НС 1 возможна

ситуация, когда между импульсами переполнения укладываются два импульса выходного сигнала. В этом случае первый D-триггер 5 может кратковременно сбрасываться в нуль, однако эта ситуация является

редкой и не оказывает существенного влияния на работу синтезатора.

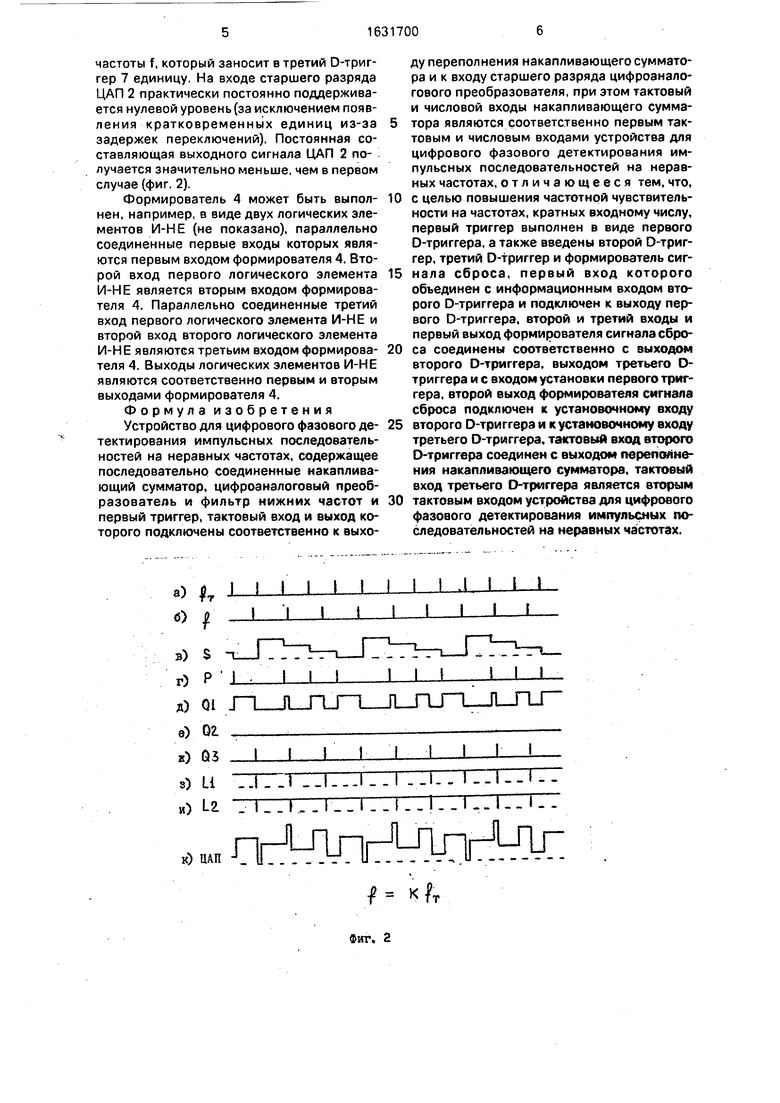

На фиг. 4 приведены временные диаграммы работы синтезатора при f k ft Сигналы здесь обозначены та/же, как на

фиг. 2. В начальный момент времени первый 5 и второй 6 D-триггеры находятся в нулевом состоянии, третий D-триггер 7 - в единичном, на выходах формирователя 4 устанавливаются 1. С приходом импульса

переполнения от НС 1 в первый D-триггер 5 записывается единица, что вызывает появление О на первом и втором выходах формирователя 4, которые сбрасывают первый, второй и третий D-триггеры 5,6 и 7 в нулевое

состояние, после чего на выходах формирователя 4 вновь устанавливаются 1, При данном соотношении частот до прихода следующего импульса переполнения от НС 1 должен появиться импульс второй тактовой

частоты f, который заносит в третий D-триг- гер 7 единицу. На входе старшего разряда ЦАП 2 практически постоянно поддерживается нулевой уровень (за исключением появ- ления кратковременных единиц из-за задержек переключений). Постоянная составляющая выходного сигнала ЦАП 2 получается значительно меньше, чем в первом случае (фиг. 2).

Формирователь 4 может быть выпол- нен, например, в виде двух логических элементов И-НЕ (не показано), параллельно соединенные первые входы которых являются первым входом формирователя 4. Второй вход первого логического элемента И-НЕ является вторым входом формирователя 4. Параллельно соединенные третий вход первого логического элемента И-НЕ и второй вход второго логического элемента И-НЕ являются третьим входом формирова- теля 4. Выходы логических элементов И-НЕ являются соответственно первым и вторым выходами формирователя 4.

Формула изобретения Устройство для цифрового фазового де- тектирования импульсных последовательностей на неравных частотах, содержащее последовательно соединенные накапливающий сумматор, цифроаналоговый преобразователь и фильтр нижних частот и первый триггер, тактовый вход и выход которого подключены соответственно к выходу переполнения накапливающего сумматора и к входу старшего разряда цифроанало- гового преобразователя, при этом тактовый и числовой входы накапливающего сумматора являются соответственно первым тактовым и числовым входами устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах,отличающееся тем,что, с целью повышения частотной чувствительности на частотах, кратных входному числу, первый триггер выполнен в виде первого D-триггера, а также введены второй D-триг- гер, третий D-триггер и формирователь сиг- нала сброса, первый вход которого объединен с информационным входом второго D-триггера и подключен к выходу первого D-триггера, второй и третий входы и первый выход формирователя сигнала сброса соединены соответственно с выходом второго D-триггера. выходом третьего D- триггера и с входом установки первого триггера, второй выход формирователя сигнала сброса подключен к установочному входу второго D-триггера и к установочному входу третьего D-триггера, тактовый вход второго D-триггера соединен с выходом переполнения накапливающего сумматора, тактовый вход третьего D-триггера является вторым тактовым входом устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1986 |

|

SU1337990A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1497704A1 |

| Частотный модулятор | 1989 |

|

SU1626320A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1988 |

|

SU1757080A1 |

| Цифровой фазовый детектор для синтезаторов частот | 1988 |

|

SU1539677A1 |

| Синтезатор частот | 1988 |

|

SU1566455A1 |

| Синтезатор частот | 1987 |

|

SU1467738A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

| Цифровой фазометр-частотомер | 1985 |

|

SU1265644A1 |

| Расходомер | 1983 |

|

SU1200126A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение частотной чувствительности на частотах, кратных входному числу. Устройство для цифрового /г -Г ш фазового детектирования импульсных последовательностей на неравных частотах содержит накапливающий сумматор (НС) 1, цифроаналоговый преобразователь (ЦАП)2, фильтр 3 нижних частот, формирователь 4 сигнала сброса, первый D-триггер 5, второй D-триггер 6, третий D-триггер 7. В исходном состоянии первый, второй и третий О-триг- геры 5, 6, 7 находятся в нулевом состоянии и на выходе формирователя 4 устанавливаются логические единицы. Работа устройства происходит по-разному в зависимости от соотношения первой и второй тактовой частоты. При tV kf, fT kf и fT kf постоянная составляющая на выходе ЦАП 2 получается различной и в зависимости от соотношения частот различен порядок срабатывания первого, второго и третьего D-триггеров 5-7. Управление порядком их срабатывания осуществляется формирователем 4. 4 ил. СО с

а) I I I I I I I I I .1 I I 1

б)ЈI I I I I I I I t

ГП П П П П П П П П.Г

I I I I I I I I I

-.1. .1 J. .

TT

.

к) ЦАП

nrJLrLnrJlJln -rlr

f xf,

Фиг. 2

а) 1-I- I i 1 1 I

б) -J II-

в)S

г)P

д)«

e)вг

ж)OS

з)U

и)

Lz

f ll

Фиг. Э

( I 1L

3) Li LJ.J

и) U L ТТТГЛ.-L-.TJ-J7.r.) ПАП

txb

U

JU j

I I I I I i I

I I I I I

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-28—Публикация

1987-07-14—Подача