(21)4455403/24

(22)18.07.88

(46) 15.03.91. Бюп. № 10 (72) С.Л.Улыбин, А.И.Ляхов и Н.Н-. Крайнева

(53)381.327.66 (088.8)

(56)Авторское свидетельство СССР № 1152034, кл. G 11 С 7/00, 1985.

(54)УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ

(57)Изобретение относится к вычислительной технике и может быть использовано для регенерации динамической памяти. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство введены второй формирователь синхросигналов, третий триггер. Блок анализа приоритетов содержит первый и второй формирова- тели импульсов. Первый формирователь синхросигналов содержит формирователь импульсов, элемент ИЛИ, распределитель импульсов, элемент задержки. 2 з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| Запоминающее устройство | 1985 |

|

SU1256096A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для сбора статистических данных о работе программ ЭВМ | 1987 |

|

SU1471202A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287238A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Многоканальное устройство для контроля памяти | 1984 |

|

SU1238164A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для управления регенерацией в полупроводниковой динамической памяти | 1991 |

|

SU1807521A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

Изобретение относится к вычислительной технике и может быть использовано для регенерации динамической памяти.

Целью изобретения является повышение быстродействия устройства.

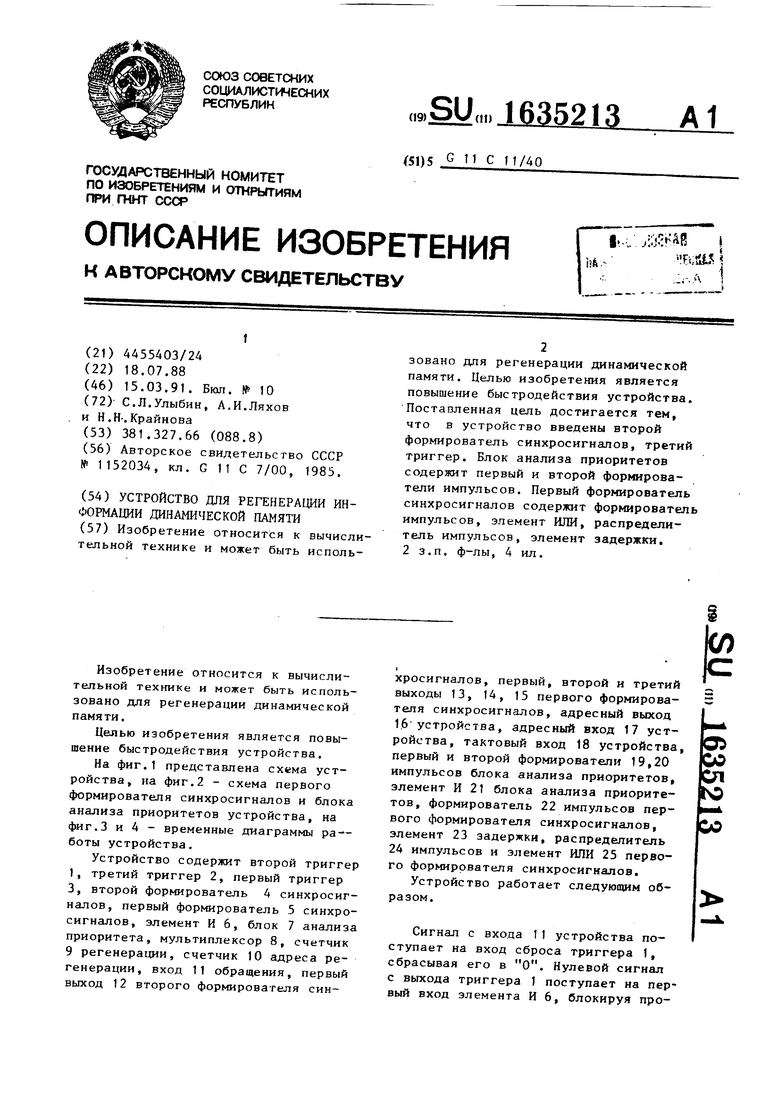

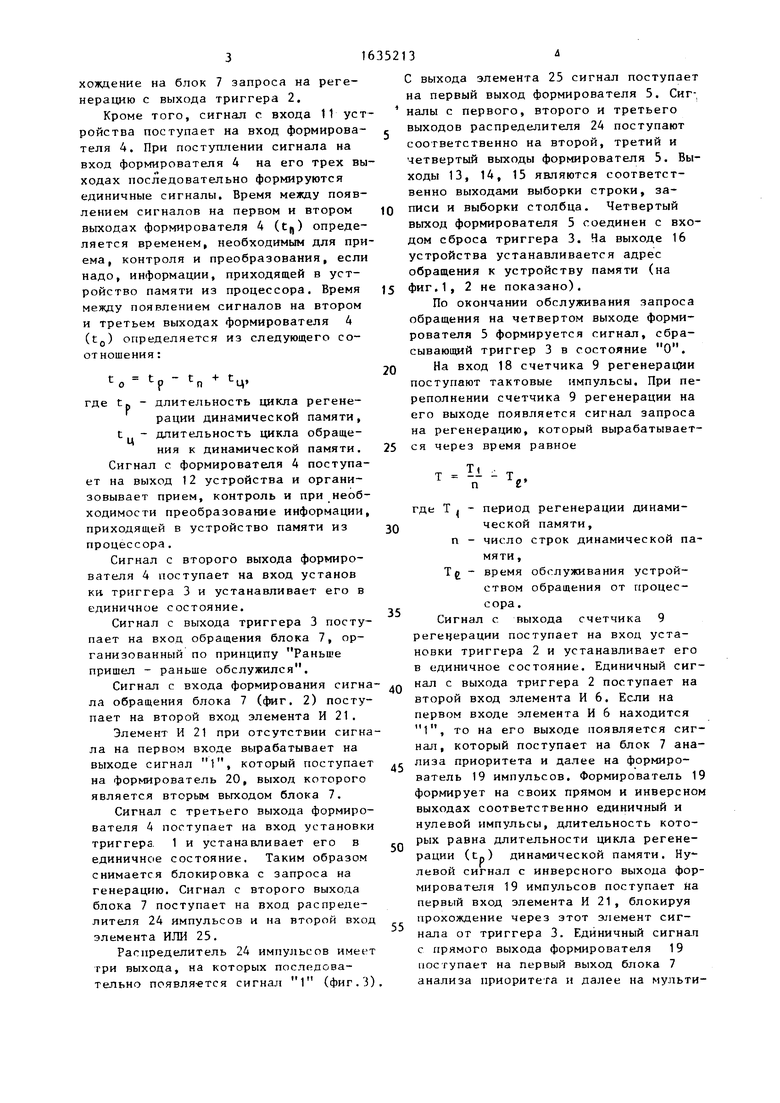

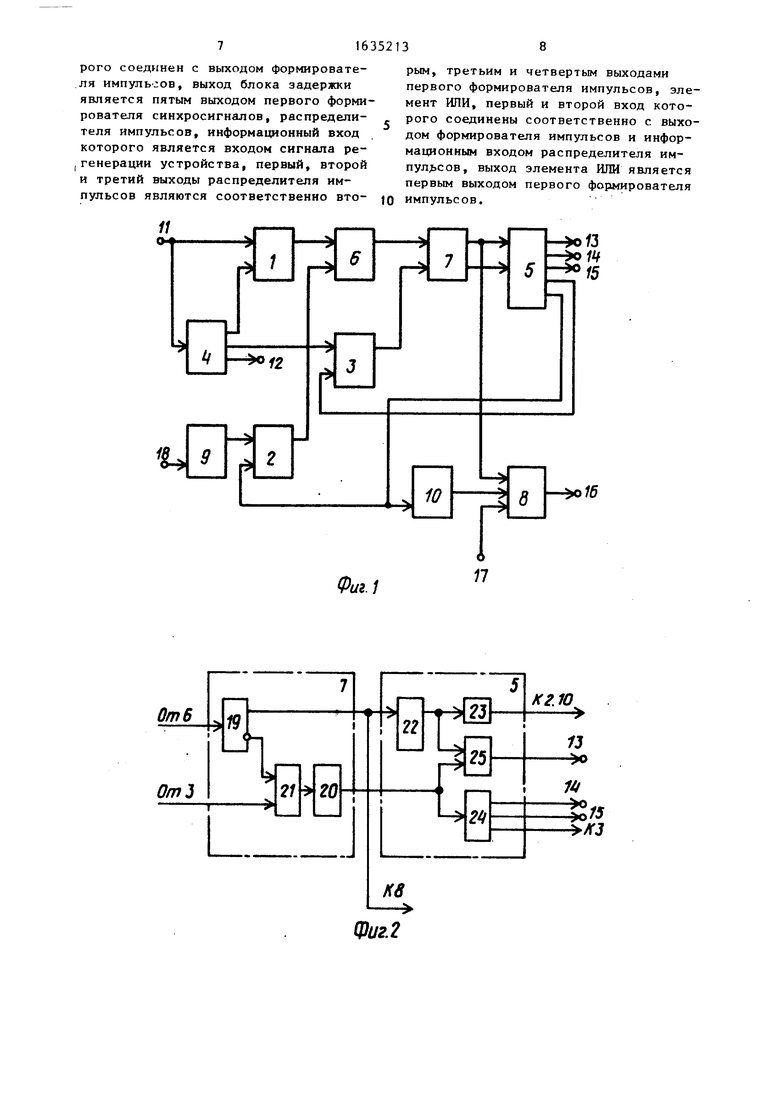

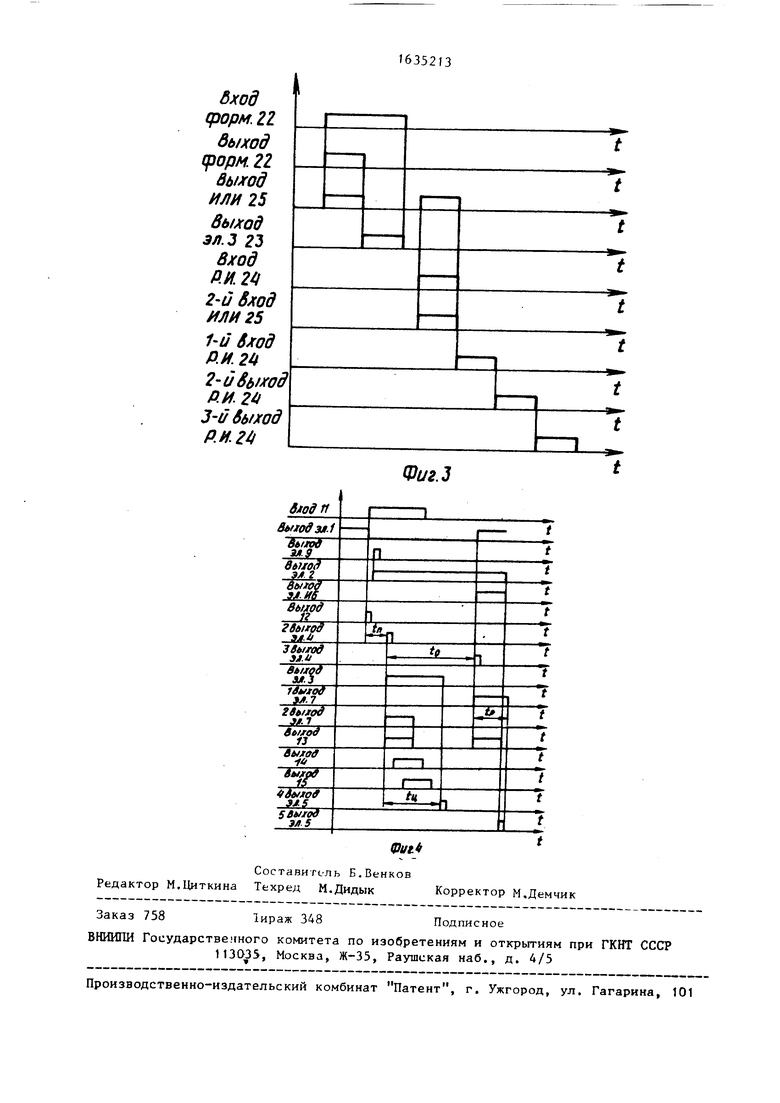

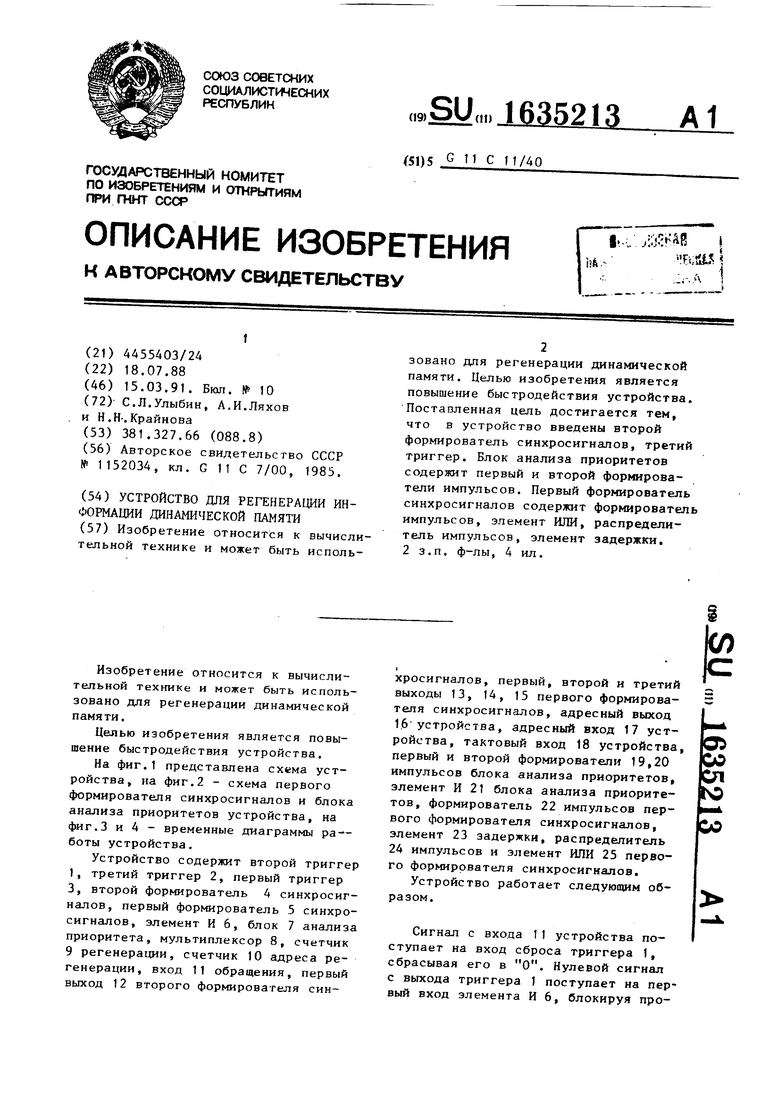

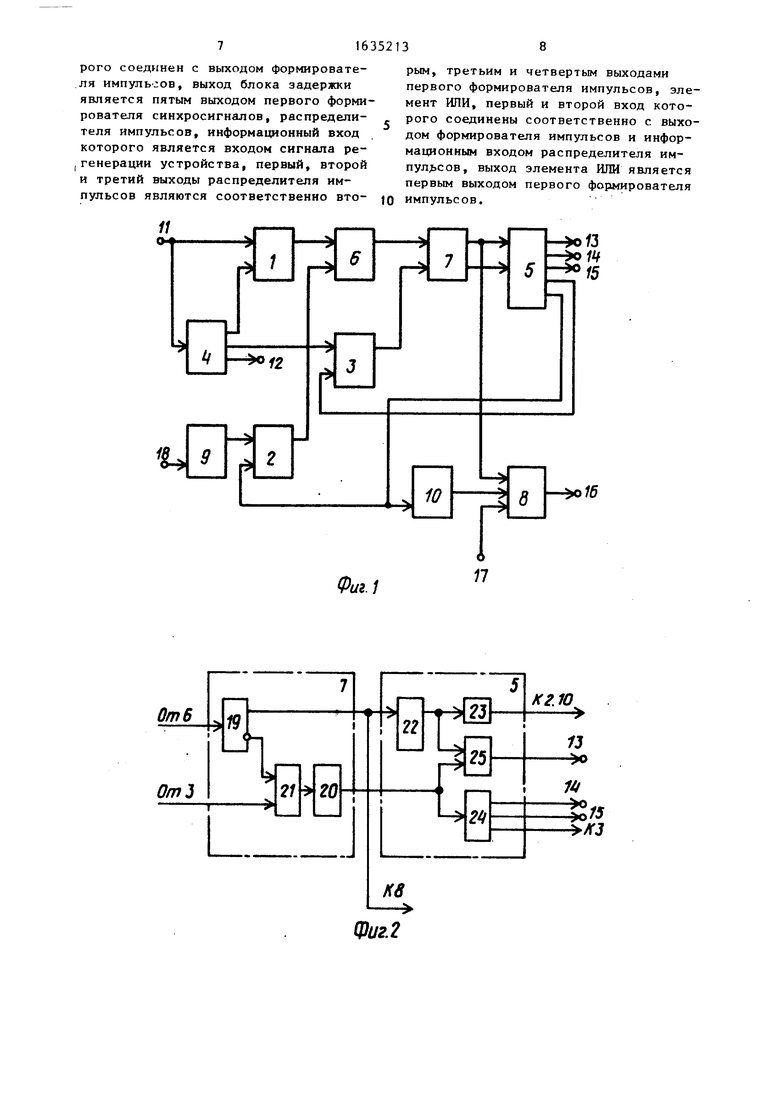

На фиг.1 представлена схема устройства, на фиг.2 - схема первого формирователя синхросигналов и блока анализа приоритетов устройства, на фиг.З и 4 - временные диаграммы работы устройства.

Устройство содержит второй триггер 1, третий триггер 2, первый триггер 3, второй формирователь 4 синхросигналов, первый формирователь 5 синхросигналов, элемент И 6, блок 7 анализа приоритета, мультиплексор 8, счетчик 9 регенерации, счетчик 10 адреса регенерации, вход 11 обращения, первый выход 12 второго формирователя синхросигналов, первый, второй и третий выходы 13, 14, 15 первого формирователя синхросигналов, адресный выход 1.6 устройства, адресный вход 17 устройства, тактовый вход 18 устройства, первый и второй формирователи 19,20 импульсов блока анализа приоритетов, элемент И 21 блока анализа приоритетов, формирователь 22 импульсов первого формирователя синхросигналов, элемент 23 задержки, распределитель 24 импульсов и элемент ИЛИ 25 первого формирователя синхросигналов.

Устройство работает следующим образом.

Сигнал с входа 11 устройства поступает на вход сброса триггера 1, сбрасывая его в О. Нулевой сигнал с выхода триггера 1 поступает на первый вход элемента И 6, блокируя прохождение на блок 7 запроса на регенерацию с выхода триггера 2.

Кроме того, сигнал с входа 11 устройства поступает на вход формирователя 4. При поступлении сигнала на вход формирователя 4 на его трех выходах последовательно формируются единичные сигналы. Время между появлением сигналов на первом и втором выходах формирователя 4 (tj) определяется временем, необходимым для приема, контроля и преобразования, если надо, информации, приходящей в устройство памяти из процессора. Время между появлением сигналов на втором и третьем выходах формирователя 4 (t0) определяется из следующего соотношения :

t + t...

Ц

где tp - длительность цикла регенерации динамической памяти, - длительность цикла обращения к динамической памяти.

Сигнал с формирователя 4 поступает на выход 12 устройства и организовывает прием, контроль и при необходимости преобразование информации, приходящей в устройство памяти из процессора.

Сигнал с второго выхода формирователя 4 поступает на вход ус танов ки. триггера 3 и устанавливает его в единичное состояние.

Сигнал с выхода триггера 3 поступает на вход обращения блока 7, организованный по принципу Раньше пришел - раньше обслужился.

Сигнал с входа формирования сигнала обращения блока 7 (фиг. 2) поступает на второй вход элемента И 21.

Элемент И 21 при отсутствии сигнала на первом входе вырабатывает на выходе сигнал 1, который поступает на формирователь 20, выход которого является вторым выходом блока 7.

Сигнал с третьего выхода формирователя 4 поступает на вход установки триггера 1 и устанавливает его в единичное состояние. Таким образом снимается блокировка с запроса на генерацию. Сигнал с второго выхода блока 7 поступает на вход распределителя 24 импульсов и на второй вход элемента ИЛИ 25.

Распределитель 24 импульсов имеет гри выхода, на которых последовательно появля-ется сигнал 1 (фиг.З)

С выхода элемента 25 сигнал поступает на первый выход формирователя 5. Сиг; налы с первого, второго и третьего выходов распределителя 24 поступают соответственно на второй, третий и четвертый выходы формирователя 5. Выходы 13, 14, 15 являются соответственно выходами выборки строки, записи и выборки столбца. Четвертый

выход формирователя 5 соединен с входом сброса триггера 3. На выходе 16 устройства устанавливается адрес обращения к устройству памяти (на

5 фиг.1, 2 не показано).

По окончании обслуживания запроса обращения на четвертом выходе формирователя 5 формируется сигнал, сбрасывающий триггер 3 в состояние О.

Q На вход 18 счетчика 9 регенерации поступают тактовые импульсы. При переполнении счетчика 9 регенерации на его выходе появляется сигнал запроса на регенерацию, который вырабатывает5 ся через время равное

т Т| . 1 - - J-«« п V

0

5

0

5

0

5

п Тс где Т j - период регенерации динамической памяти,

число строк динамической памяти,

время обслуживания устройством обращения от процессора .

Сигнал с выхода счетчика 9 регенерации поступает на вход установки триггера 2 и устанавливает его в единичное состояние. Единичный сигнал с выхода триггера 2 поступает на второй вход элемента И 6. Если на первом входе элемента И 6 находится 1, то на его выходе появляется сигнал, который поступает на блок 7 анализа приоритета и далее на формирователь 19 импульсов. Формирователь 19 формирует на своих прямом и инверсном выходах соответственно единичный и нулевой импульсы, длительность которых равна длительности цикла регенерации (t.) динамической памяти. левой сигнал с инверсного выхода формирователя 19 импульсов поступает на первый вход элемента И 21, блокируя прохождение через этот элемент сигнала от триггера 3. Единичный сигнал с прямого выхода формирователя 19 поступает на первый выход блока 7 анализа приоритета и далее на мульти51

плексор 8 и формирователь 5. Мультиплексор 8 при этом пропускает на свой выход, а следовательно, и на выход 16 устройства адрес регенерируемой строки, приходящей на его второй вход с выхода счетчика 10 адреса регенерации.

Единичный сигнал с первого выхода блока 7 поступает на формирова- тель 22, который формирует на своем выходе сигнал, длительность которого равна длительности сигнала выборки строки (фиг. 3). Сигнал с выхода формирователя 22 поступает на вход эле- мента 23 задержки и первый вход элемента ИЛИ 25. С выхода элемента ИЛИ 25 сигнал поступает на выход 13 устройства. Сигнал с выхода элемента 23 задержки поступает на пятый выход формирователя 5. Сигнал на втором, третьем и четвертом выходах формирователя 5 не формируется. По завершении цикла регенерации на пятом выходе формирователя 5 формируется сигнал, который поступает на вход сброса триггера 2 и вход счетчика 10 адреса регенерации. При этом триггер 2 сбрасывается в О, а на счетчике 10 адреса регенерации устанав- ливается адрес следующей строки, подлежащей регенерации. Таким образом, предлагаемое устройство позволяет проводить регенерацию в моменты пауз между обращениями к памяти, за счет чего повышается эффективное быс трод ейс т оие.

Формула изобретения

5

0

5

0

5 0 5

13

ные входы которого соединены соответственно с выходом счетчика адреса регенерации, первым выходом блока анализа приоритетов и с выходом счетчика адреса регенерации, адресный вход и выход мультиплексора являются адресным входом и адресным выходом устройства, счетчик регенерации, вход которого является тактовым входом устройства, элемент И, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит второй формирователь синхросигналов, вход обращения которого является входом обращения устройства, первый выход первого формирователя синхросигналов является тактовым выходом устройства, вход установки и вход сброса которого соединены соответственно с третьим выходом и входом обращения второго формирователя синхросигналов, выход второго триггера соединен с первым входом элемента И, третий триггер, вход установки и вход сброса которого соединены соответственно с выходом счетчика регенерации и пятым выходом второго формирователя синхросигналов, выход третьего триггера соединен с вторым входом элемента И, вход счетчика адреса регенерации соединен с пятым выходом второго формирователя синхросигналов, вход обращения блока анализа приоритетов соединен с выходом элемента И.

и прямой выход которого являются соответственно входом обращения и первым выходом блока анализа приоритетов, элемент И, первый вход которого соединен с инверсным выходом первого формирователя импульсов, второй вход элемента И является входом формирования сигнала обращения, второй формирователь импульсов, вход обращения которого соединен с выходом элемента И, а выход является выходом блока анализа приоритетов.

рым, третьим и четвертым выходами первого формирователя импульсов, элемент ИЛИ, первый и второй вход которого соединены соответственно с выходом формирователя импульсов и информационным входом распределителя импульсов, выход элемента ИЛИ является первым выходом первого формирователя импульсов.

Я

/4

(i П

Вход форм. 22

выход форм. 22

выход или25

Выход эл.З 23

Вход Р.И.24

2-й Вход ИЛ И 25

1-й Вход Р.И.2И 2 uBbixod АИ. 24 3-й Выход

Р.Н.24

Авторы

Даты

1991-03-15—Публикация

1988-07-18—Подача