Фаг Л

кретной фазовой синхронизации содержит формирователь 1 импульсов входной последовательности, фазовые дискриминаторы 2, 7 и 8, блоки 3 и 9 реверсивного усреднения, блок 4 добавления - исключения импульсов, генератор 5 опорной последовательности импульсов, счетчик 6 импульсов, элемент ИЛИ 10 и демультиплексор 11. В фазовом дискриминаторе 2 определяется знак фазового рассогласования между импуаьсами входной последовательности и импульсами фазируемой последовательности, поступающими с первого выхода демулмиплексора 11. На соответствующие входы блока 4 через блок 3 поступают управляюпще импульсы. В результате в опорной последовательности импульсов генератора 5 происходит изменения периода на До при каждом исключении или добавлении импульсов. При фазовом рассогласовании, большем заранее выбранной величины ± ДТ0 , параллельно с вышеописанной работой фазовыми дискрими- наторами 7 и 8 формируются импульсы, поступающие на блок 9, с выхода которого через элемент ИЛИ 10 на вход установки в О счетчика 6 поступает импульс,что вызывает формирование на первом выходе демультиплексора 11 выходной последовательности, синфазной с входной. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОНТРОЛЯ СИНХРОНИЗМА КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1993 |

|

RU2057395C1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU869074A1 |

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство выделения тактовых импульсов | 1986 |

|

SU1425864A2 |

| Устройство фазирования бинарного сигнала | 1981 |

|

SU1075431A1 |

| Устройство синхронизации | 1984 |

|

SU1223390A1 |

Изобретение относится к системам дискретной передачи информации. Цель изобретения - уменьшение времени вхождения л синхронизм при больших фазовых рассогласованиях входного и опорного сигналов. Устройство дис

Изобретение относится к системам дискретной передачи информации и может быть использовано в системах так- товой синхронизации.

Цель изобретения - сокращение времени вхождения в синхронизм при больших фазовых рассогласованиях входного и опорного сигналов.

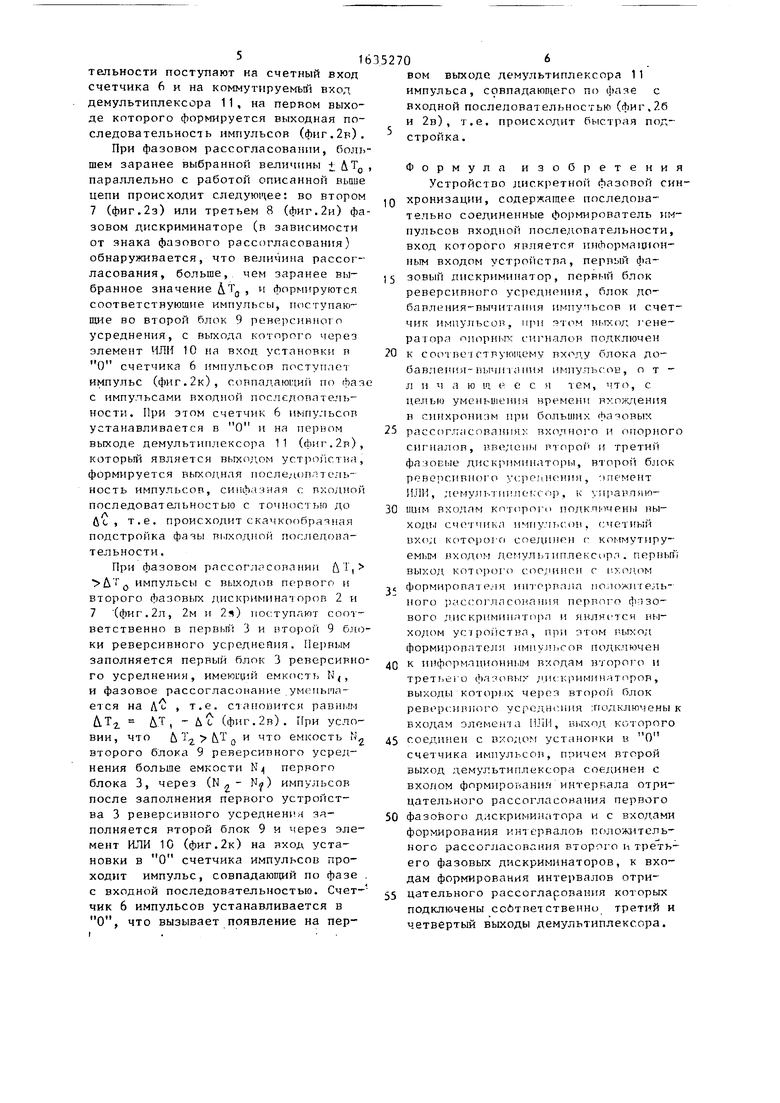

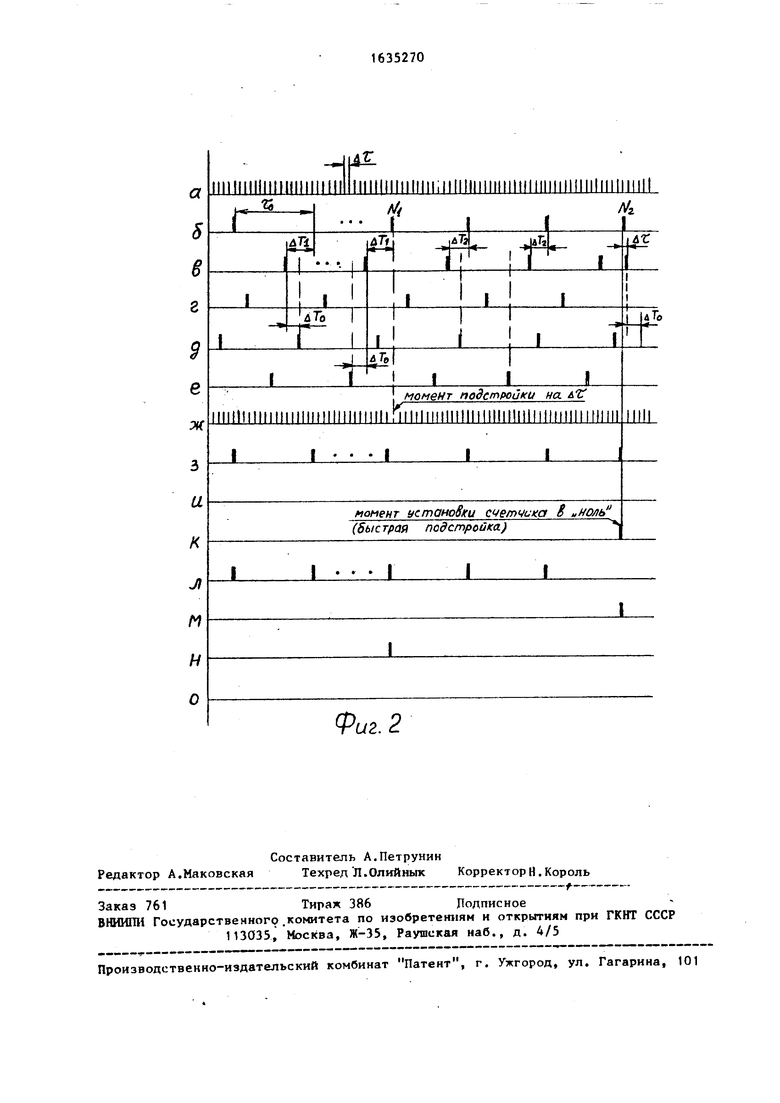

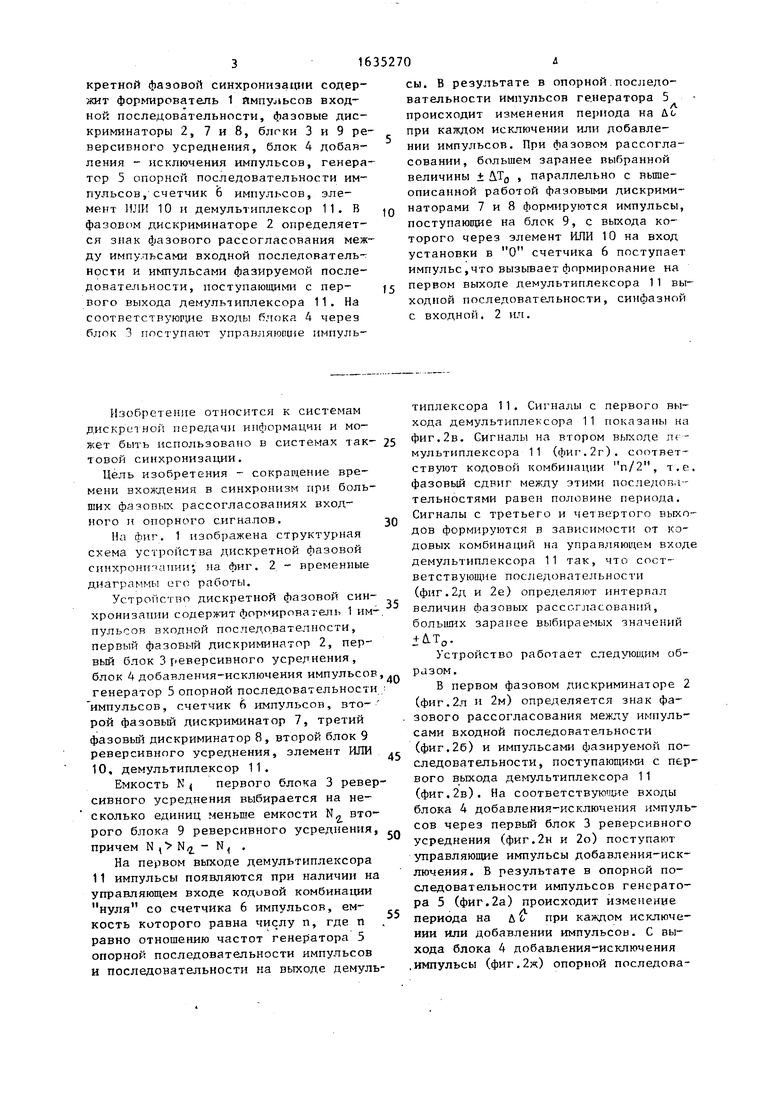

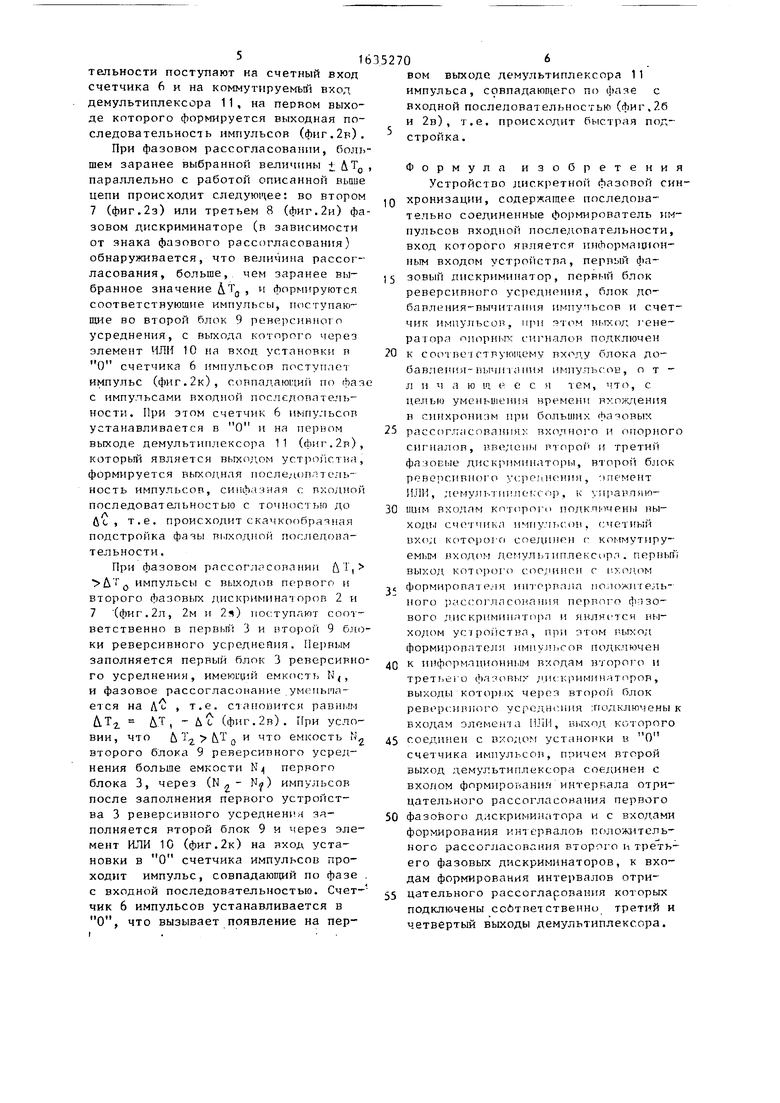

На фиг. 1 изображена структурная схема устройства дискретной фазовой синхрошпапии, на фиг. 2 - временные диаграммы его работы.

Устройство дискретной фазовой синхронизации содержит формирователь 1 импульсов входной последователности, первый фазовый дискриминатор 2, первый блок 3 реверсивного усреднения, блок 4 добавления-исключения импульсов генератор 5 опорной последовательности импульсов, счетчик 6 импульсов, вто- рой фазовый дискриминатор 7, третий фазовый дискриминатор 8, второй блок 9 реверсивного усреднения, элемент ИЛИ 10, демультиплексор 11.

Емкость N первого блока 3 реверсивного усреднения выбирается на несколько единиц меньше емкости N второго блока 9 реверсивного усреднения, причем N , М - N1 .

На первом выходе демультиплексора 11 импульсы появляются при наличии на управляющем входе кодовой комбинации

нуля со счетчика 6 импульсов, емкость которого равна числу п, где п равно отношению частот генератора 5 опорной последовательности импульсов и последовательности на выходе демуль35

5

Q

45

0

5

типлексора 11. Сигналы с первого выхода демультиплексора 11 показаны на фиг.2в. Сигналы на втором выходе л - мультиплексора 11 (фиг.2г). соответствуют кодовой комбинации п/2, т.е. фазовый сдвиг между этими последовательностями равен половине периода. Сигналы с третьего и четвертого выходов формируются в зависимости от кодовых комбинаций на управляющем входе демультиплексора 11 так, что соответствующие последовательности (фиг.2д и 2е) определяют интервал величин фазовых рассогласований, больших заранее выбираемых значений .

Устройство работает следующим образом.

В первом фазовом дискриминаторе 2 (фиг.2л и 2м) определяется знак фазового рассогласования между импульсами входной последоватепьности (фиг.2б) и импульсами фазируемой последовательности, поступающими с первого выхода демультиплексора 11 (фиг.2в). На соответствующие входы блока 4 добавления-исключения импульсов через первый блок 3 реверсивного усреднения (фиг.2н и 2о) поступают управляющие импульсы добавления-исключения. В результате в опорной последовательности импульсов генератора 5 (фиг.2а) происходит изменение периода на Д б при каждом исключении или добавлении импульсов. С выхода блока 4 добавления-исключения .импульсы (фиг.2ж) опорной последовательности поступают на счетный вход счетчика 6 и на коммутируемый вход демультиплексора 11, на первом выходе которого формируется выходная последовательность импульсов (фиг.2в).

При фазовом рассогласовании, большем заранее выбранной величины j Д.Т0 параллельно с работой описанной выше цепи происходит следующее: во втором 7 (фиг.2з) или третьем 8 (фиг.2и) фазовом дискриминаторе (в зависимости от знака фазового рассогласования) обнаруживается, что величина рассогласования, больше, чем заранее выбранное значение &Т0, и формируются соответствующие импульсы, поступающие во второй блок 9 реверсивното усреднения, с выхода которого через элемент ИЛИ 10 на вход установки в О счетчика 6 импульсов поступает импульс (фиг.2к), совпадающий по фаз с импульсами входной последовательности. При этом счетчик 6 импульсов устанавливается в О и на первом выходе демулы иплексора 11 (фиг.2в), который является выходом устройства, формируется выходная последов.п ель- ность импульсов, синфазная с входной последовательностью с точное ыо до йс, т.е. происходит скачкообразная подстройка фазы выходной последовательности .

При фазовом рассогласовании & 1, Д Г0 импульсы с выходов первого и второго фазовых дискриминаторов 2 и 7 (фиг. 2л, 2м и 2я) поступают соответственно в первый 3 и второй 9 блоки реверсивного усреднения. Первым заполняется первый блок 3 реверсивного усреднения, имеющий емкость NJ, и фазовое рассогласование уменьшается на Л т.е. становится равным &Тг &Т , - &Ј (фиг.2в). При условии, что &Т ТQ и что емкость N второго блока 9 реверсивного усреднения больше емкости N первого блока 3, через ( N) импульсов после заполнения первого устройства 3 реверсивного усреднения заполняется второй блок 9 и через элемент ИЛИ 10 (фиг.2к) на вход установки в О счетчика импульсов проходит импульс, совпадающий по фазе с входной последовательностью. Счетчик 6 импульсов устанавливается в О, что вызывает появление на пер

0

5

вом выходе демультиплексора 11 импульса, совпадающего по фазе с входной последовательностью (фиг.26 и 2в), т.е. происходит быстрая подстройка .

Формула изобретения

Устройство дискретной фазовой синхронизации, содержащее последовательно соединенные формирователь импульсов входной последовательности, вход которого является инсЬормацион- ным входом устройства, первый фа5 зовый дискриминатор, первый блок реверсивного усреднения, блок добавления-вычитания импутьсов и счетчик импульсов, при °том выход гене- раюра опорных сигналов подключен к соответствующему входу блока добавления- вычи1 а ним импульсов, о т - л и ч а ю щ е е с я тем, что, с целью уменьшения времени вхождения в синхронизм при больших фаговых рассогласованиях входного и опорного сигналов, введены второй и третий фазосые дискриминаторы, второй блок реверсивного усррлнонин, чпемент ИЛИ, демупьт иппс кч чр , к мфавпню- щим входам которого подключены выходы счетчика импучьсон, счетный вход которого соединрц с коммутируемым входом демультиплексируй . первый выход которого СОРДИНРН г .ходом формирователя интервала положительного рассогласования первого фчзо- вого дискриминатора и является ны- ходом устройства, при этом выход формирователи имнупьгов подключен к информационным входам второго и третье о фаговых дискриминаторов, выходы которых череп второй блок реверсивного усреднения -подключены к входам элемента ИЛИ, выход которого соединен с входом установки в О счетчика импульсов, причем второй выход демультиплексора соединен с вхопом формирования интерпала отрицательного рассогласования первого

0 фазового дискриминатора и с входами формирования интервалов положительного рассогласования второго и третьего фазовых дискриминаторов, к входам формирования интервалов отри5 дательного рассогласования которых подключены ссбтветственно третий и четвертый выходы демультиплексора.

0

0

5

| Бухвинер В.Е.Дискретные схемы в фазовых системах радиосвязи | |||

| М. | |||

| Связь, 1969, с.18. |

Авторы

Даты

1991-03-15—Публикация

1988-03-31—Подача