Изобретение относится к вычислительной технике и может быть использовано при создании многомашинных вычислительных систем.

Цель изобретения - расширение функциональных возможностей за счет подключения к системе более двух ЭВМ.

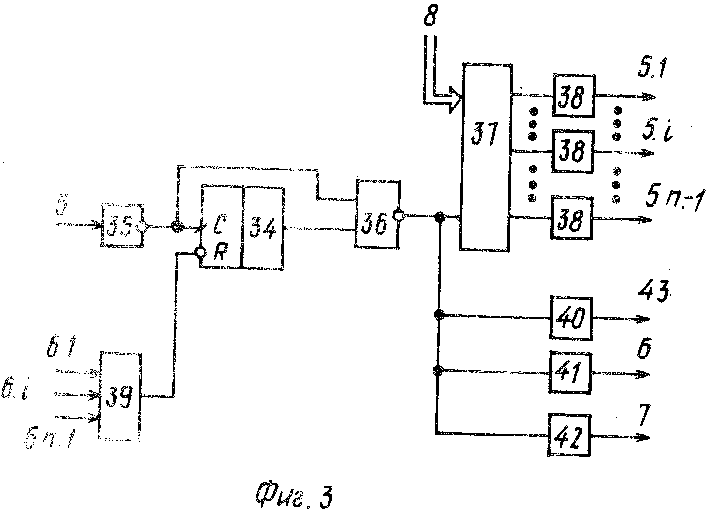

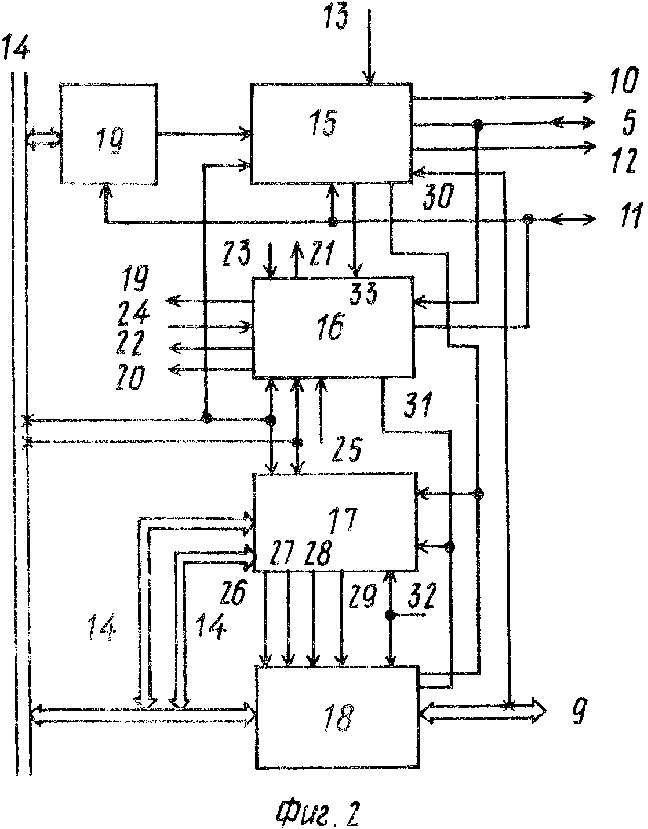

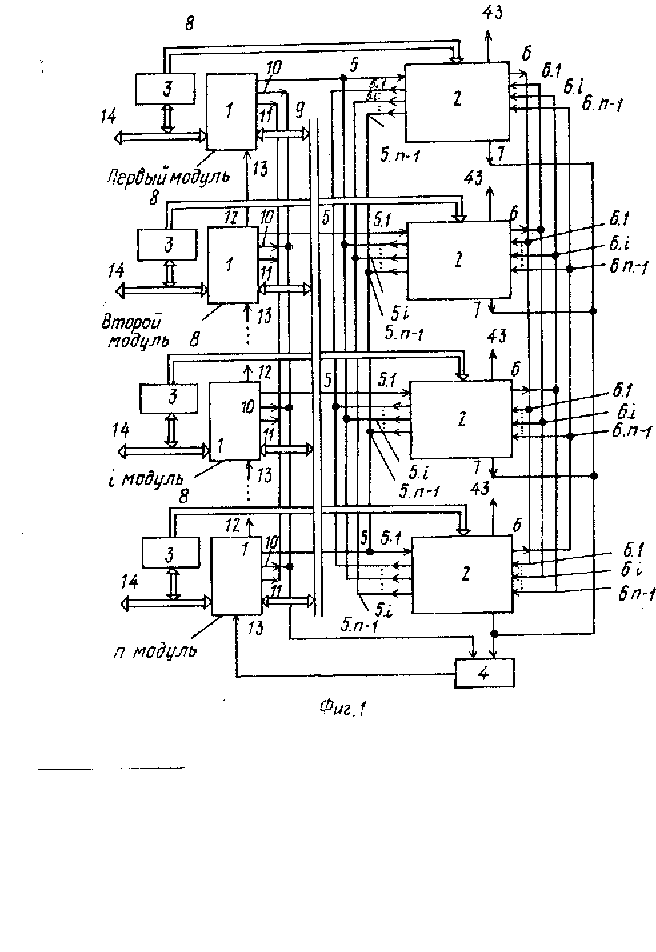

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема модуля доступа к системной магистрали; на фиг. 3 - структурная схема блока дешифрации номера абонента.

Устройство (фиг. 1) содержит модуль 1 доступа к системной магистрали, блок 2 дешифрации номера абонента, регистр 3 выбора абонента, арбитр 4, 5-14 связи блоков.

Модуль доступа к системной магистрали (фиг. 2) содержит блока 15 захвата системной магистрали, блок 16 захвата внутренней магистpали, блок 17 управления приемопередатчиками, блок 18 магистральных приемопередатчиков, регистр 19 состояния, 20-23 - внутренние и внешние связи блока.

Блок 2 дешифрации номера абонента (фиг. 3) содержит триггер 34, элемент НЕ 35, элемент И-НЕ 36, дешифратоp 37, группу шинных формирователей 38, элемент И 39, шинные формирователи 40-42, 43, выход сигнала требования прерывания.

Устройство предназначено для организации обмена между ЭВМ, подключаемых к магистралям 14 (внутренняя магистраль) через системную магистраль 9.

Устройство работает следующим образом.

Например, первый процессор, подключенный к первому модулю 1 и регистру 3, хочет произвести обмен информацией с запоминающим устройством i-го процессора, подключенного к i-му модулю 1. Он производит обращение по информационным входам-выходам и входам -выходам управления 14 к своему регистру 3, занося в него код, соответствующий коду выбранного i-го процессора. Регистр 3 выбора абонента запоминает данный код и выставляет его на выходной магистрали 8 установки абонента, соединенной с входной магистралью установки абонента блока 2 данного процессора. Затем процессор обращается к модулю 1, инициируя выработку им сигнала низким уровнем по управляющему выходу 10, сигнал с которого поступает на входу арбитра 4. Арбитр 4 на своем выходе вырабатывает сигнал низким уровнем, который поступает на вход 13 n-го модуля 1, который в случае отсутствия требования на обмен от n-го процессора транслирует данный сигнал на управляющий выход 12 n-го модуля 1 и так далее, сигнал проходит на управляющий вход 13 первого модуля 1. Получив данный сигнал, первый модуль 1 снимает сигнал низкого уровня по управляющему выходу 10 и устанавливает сигнал низким уpовнем по управляющему входу-выходу 5, поступающий на вход первого блока 2. Сигнал с этого входа блока 2 поступает на вход "С" триггера 34 через элемент НЕ 35, переводит его в состояние с высоким уровнем по выходу. Сигнал низкого уровня, появившийся на выходе элемента И-НЕ 36, разблокирует дешифратор 37, который на одном из своих выходов, соответствующих коду, поступившему на него по магистрали установки абонента 8, формирует сигнал низкого уровня, проходящий через соответствующий буферный элемент 38 на выход подтверждения выбора i-го абонента блока 2, соединенного с управляющим входом-выходом 5 i-го модуля 1 и входом i-го блока 2.

Одновременно сигнал низкого уровня с выхода элемента И-НЕ 36 блока 2 поступает на входы формирователей 40, 41, 42. Сигнал низкого уровня с выхода формирователя 40 поступает в виде сигнала требования прерывания 43 в i-й процессор, информируя его о том, что его запрос на обращение находится в стадии удовлетворения, С выхода узла 42 сигнал низким уровнем поступает на вход арбитра 4 который, получив данный сигнал, снимает сигнал низкого уровня со своего выхода.

Сигнал низкого уровня с выхода шинного формирователя 41 поступает на один из (-1) входов блокировки 6.1-6. n-1 остальных блоков 2, в том числе и i-го блока 2, тем самым формируя на выходе элемента И 39 сигнал низкого уровня, а значит и блокировку по входу R триггера 34 i-го блока 2. Данная блокировка необходима для предотвращения формирования i-м блоком 2 сигналов подтверждения выбора 5.1-5. n-1, по приходу сигнала низким уровнем по первому входу и тем самым дополнительного несанкционированного обмена.

Сигнал низкого уровня, поступающий на управляющий вход-выход 5 i-го модуля 1, инициирует формирование сигнала управления по переводу i-го процессора в режим прямого доступа к памяти подключении магистрали к системной магистрали 9 и формирование после данного захвата сигнала низким уровнем по управляющему входу-выходу 11. Получив сигнал низкого уровня по управляющему входу-выходу 11, первый модуль 1 осуществляет подключение своей магистрали 14 к магистрали 9. Первый процессор, опросив регистр 19 состояния i-го модуля 1 и убедившись в наличии сигнала низкого уровня на управляющем входе-выходе 11, производит обмен информацией с запоминающим устройством i-го процессора, подключенному к i-му модулю 1.

По окончании обмена первый процессор заносит в первый модуль 1 код, соответствующий окончанию обмена. Первый модуль 1 снимает сигнал низкого уровня с управляющего входа-выхода 5 и разрывает связь между магистралями 14 и 9.

Первый блок 2 снимает сигналы низкого уровня с i-го выхода 5, с выхода 7 i-го выхода 6 и выхода требования прерывания 43, i-й модуль 1 разрывает связь между магистралями 14 и 9, снимает сигнал низкого уровня по управляющему входу-выходу 11 и формирует сигнал требования прерывания 21 в свой i-й процессор, информируя его о том, что с ним прошел цикл обмена информацией.

Аналогичным образом производится обмен между двумя любыми из процессоров.

Блок выбора абонента представляет из себя регистр, реализованный на микросхеме типа 588ИР1, и устройство, различающее адрес обращения к данному регистру по первым информационным входам-выходам и входам-выходам управления и формирующее строб записи в регистр, выполненное на микросхеме типа 588ВТ1. (56) Фридштанд В. Д. Особенности организации межмашинного обмена в системах на базе микроЭВМ "Электроника-60". Приборы и системы управления. N 10, 1985, с, 40-41, рис. 1.

Авторское свидетельство СССР N 1549371, кл. G 06 F 15/16, 1988,

| название | год | авторы | номер документа |

|---|---|---|---|

| Отказоустойчивая вычислительная система | 1990 |

|

SU1798800A1 |

| УСТРОЙСТВО МЕЖМАШИННОГО ОБМЕНА | 1987 |

|

SU1549371A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Многомашинная вычислительная система | 1990 |

|

SU1798798A1 |

Изобретение относится к вычислительной технике и может быть использовано для создания многомашинных вычислительных систем. Цель изобретения - расширение функциональных возможностей за счет подключения к системе более двух ЭВМ. Устройство содержит модуль 1 доступа к системной магистрали, блок 2 дешифрации номера абонента, регистр 3 выбора абонента, арбитр 4. 3 ил.

УСТРОЙСТВО МЕЖМАШИННОГО ОБМЕНА, содержащее арбитр и n модулей доступа к системной магистрали (n - количество машин в системе), причем входы и выходы системной магистрали всех модулей доступа к системной магистрали объединены между собой через системную магистраль, первые управляющие выходы модулей доступа к системной магистрали объединены между собой и подключены к первому входу арбитра, выход которого соединен с управляющим входом n-го модуля, второй управляющий выход i-го (i=  ) модуля доступа к системной магистрали соединен с управляющим входом (i - 1)-го модуля доступа к системной магистрали, управляющие входы-выходы модулей доступа к системной магистрали объединены между собой, отличающееся тем, что, с целью расширения функциональных возможностей за счет подключения к системе более двух ЭВМ, в него введены n регистров выбора абонента и n блоков дешифрации номера абонента, причем входы и выходы внутренней магистрали i-го (i=

) модуля доступа к системной магистрали соединен с управляющим входом (i - 1)-го модуля доступа к системной магистрали, управляющие входы-выходы модулей доступа к системной магистрали объединены между собой, отличающееся тем, что, с целью расширения функциональных возможностей за счет подключения к системе более двух ЭВМ, в него введены n регистров выбора абонента и n блоков дешифрации номера абонента, причем входы и выходы внутренней магистрали i-го (i=  ) модуля доступа к системной магистрали соединены с магистральными входами-выходами i -го регистра выбора абонента, выходы которого соединены с информационными входами i-го блока дешифрации номера абонента, третий управляющий выход i-го модуля доступа к системной магистрали объединен с i-ми информационными выходами групп каждого блока дешифрации номера абонента, кроме i-го, и подключены к первому управляющему входу i-го блока дешифрации номера абонента, первые управляющие выходы блоков дешифрации номера абонента соединены с вторым входом арбитра, вторые управляющие выходы этих блоков являются входами требования прерывания внутренних магистралей соответствующих модулей доступа к системной магистрали, третий выход i-го (i=

) модуля доступа к системной магистрали соединены с магистральными входами-выходами i -го регистра выбора абонента, выходы которого соединены с информационными входами i-го блока дешифрации номера абонента, третий управляющий выход i-го модуля доступа к системной магистрали объединен с i-ми информационными выходами групп каждого блока дешифрации номера абонента, кроме i-го, и подключены к первому управляющему входу i-го блока дешифрации номера абонента, первые управляющие выходы блоков дешифрации номера абонента соединены с вторым входом арбитра, вторые управляющие выходы этих блоков являются входами требования прерывания внутренних магистралей соответствующих модулей доступа к системной магистрали, третий выход i-го (i=  ) блока дешифрации номера абонента соединен с i-ми входами блокировки j - x (j < i) блоков дешифрации номера абонента и (i - 1)-ми входами блокировки k - x (k > i) блоков дешифрации номера абонента.

) блока дешифрации номера абонента соединен с i-ми входами блокировки j - x (j < i) блоков дешифрации номера абонента и (i - 1)-ми входами блокировки k - x (k > i) блоков дешифрации номера абонента.

Авторы

Даты

1994-02-15—Публикация

1989-04-14—Подача