Изобретение относится к вычислительной технике и может быть использовано при создании многомашинных вычислительных систем.

Целью изобретения является повышение скорости межмашинного обмена за счет осуществления прямого доступа процессора одной микро-ЭВМ к ресурсам другой без значительного увеличения аппаратурных затрат.

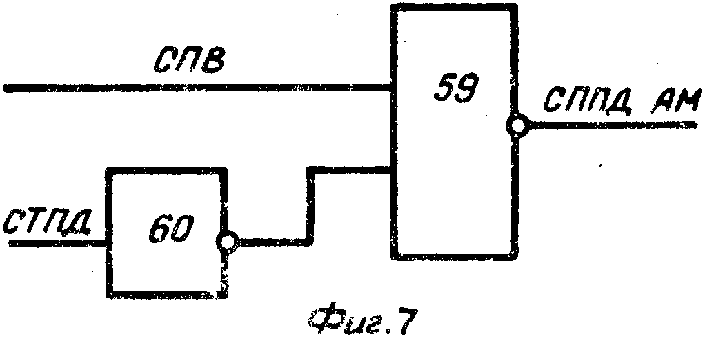

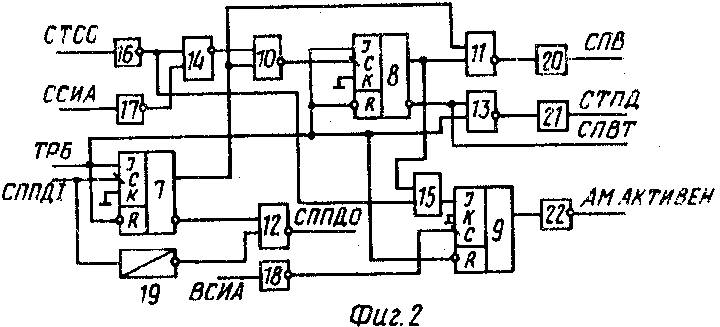

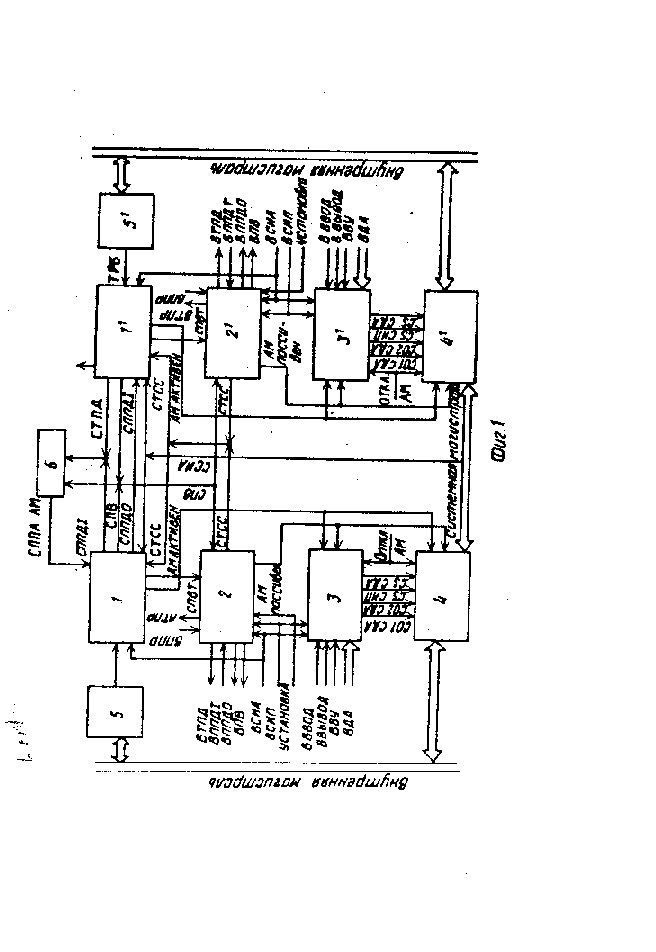

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока захвата системной магистрали; на фиг. 3 - функциональная схема блока захвата внутренней магистрали; на фиг. 4 - функциональная схема блока управления магистральными приемопередатчиками; на фиг. 5 - функциональная схема блока магистральных приемопередатчиков; на фиг. 6 - функциональная схема блока регистра состояния; на фиг. 7 - функциональная схема арбитра магистрали.

Устройство (фиг. 1) содеpжит блоки 1 захвата системной магистрали, блоки 2 захвата внутренней магистрали, блоки 3 управления магистральными приемопередатчиками, блоки 4 магистральных приемопередатчиков, блоки 5 регистров состояния, арбитр 6 магистрали.

Блок захвата системной магистрали (фиг. 2) содержит триггеры 7-9, элементы И-НЕ 10-13, элемент ИЛИ-НЕ 14, элемент И 15, элементы НЕ 16-18, линию задержки 19, буферные элементы 20, 21 и 22.

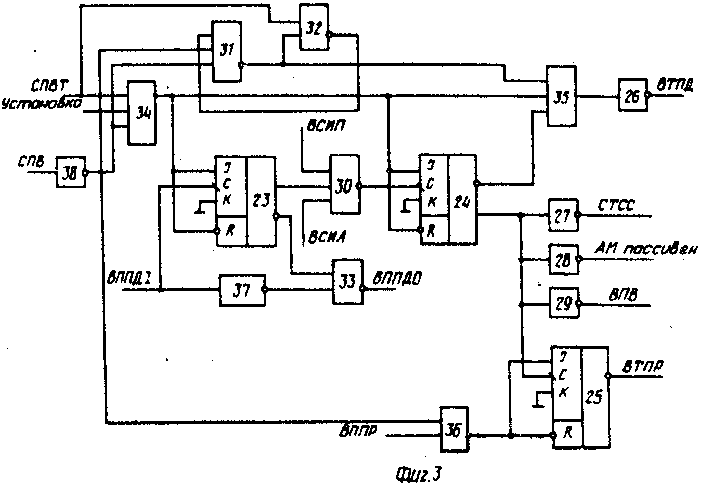

Блок захвата внутренней магистрали (фиг. 3) содержит триггеры 23 и 25, буферные элементы 26-29, элементы И-НЕ 30-33, элементы И 34-36, линию задержки 37, элемент НЕ 38.

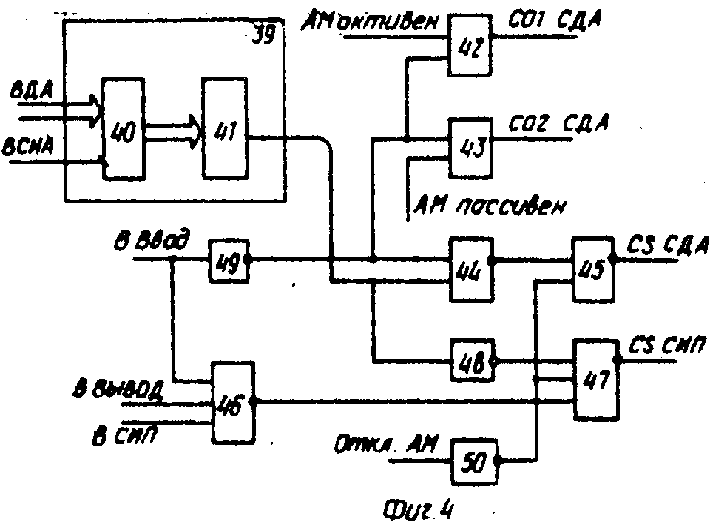

Блок управления магистральными приемопередатчиками (фиг. 4) содержит дешифратор 39, регистр 40, схему совпадения 41, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 42 и 43, элементы И-НЕ 44-47, элементы НЕ 48-50.

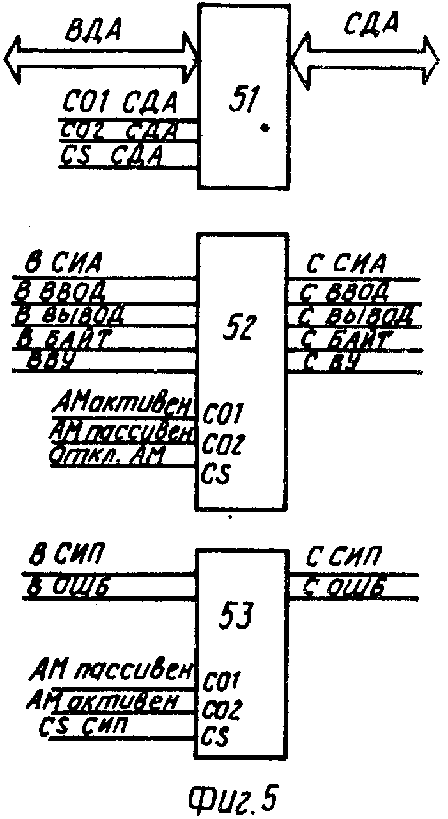

Блок магистральных приемопередатчиков (фиг. 5) содержит приемопередатчик 51 данных, приемопередатчики 52 и 53 управления.

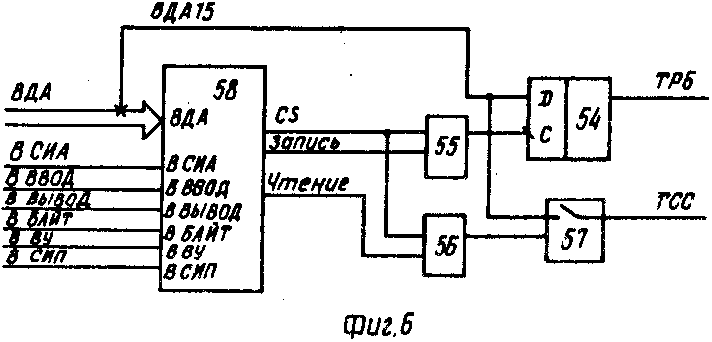

Блок регистра состояния (фиг. 6) содержит триггер 54, элемент ИЛИ 55 и 56, ключевой элемент 57, селектор 58 адреса.

Блок арбитра магистрали (фиг. 7) содержит элемент И-НЕ 59 и элемент НЕ 60.

Устройство работает следующим образом.

Например, процессор выдает по внутренней магистрали в блок 5 регистра состояния информацию о начале обмена по магистрали. Блок 5 вырабатывает сигнал ТРБ в блок 1, который вырабатывает сигнал СТПД, поступающий в арбитр 6 магистрали. Арбитр 6 магистрали форсирует сигнал СППД АМ в случае, если есть сигнал СТПД и отсутствует сигнал СПВ. Сигнал СППД АМ, поступающий с арбитра 6 магистрали на вход СППД 1 блока 1, инициирует выдачу сигнала СПВ блоком 1, а также СПВТ, который поступает в блок 2 и блокирует возможную выдачу сигналов захвата магистрали. Арбитр 6 магистрали снимает сигнал СППД АМ.

Сигнал СПВ поступает на вход блока 2 и инициирует выработку сигнала ВТПД, поступающего в процессор. Из процессора поступает сигнал ППД 1, при поступлении которого блок 2 формирует сигналы ВПВ, тем самым захватывая в свое пользование внутреннюю магистраль процессора. Сигнал "АМ пассивен", поступающий в блоки 3 и 4, инициирует работу блока 4 в качестве буфера пассивного устройства выдачей сигналов СО1 СДА, СО2 СДА, CS СИП, CS СДА и сигнала СТСС, вырабатываемого блоком 2, который поступает на вход блока 5, и при опросе последнего по внутренней магистрали процессором осуществляется чтение готовности обмена по системной магистрали. По приходе сигнала СТСС и снятию сигнала ВСИА блок 1 формирует сигнал "АМ активен", т. е. инициирует работу блока 4. Тем самым инициируется связь между внутренними магистралями и системной магистралью через блоки 4 обоих модулей. Направление обмена определяется сигналами "ВВОД" и "ВЫВОД".

Начальная установка блока 2 осуществляется по входу установки. По окончании обмена в блок 5 записывается код, соответствующий окончанию обмена. Блок 5 снимает сигнал ТРБ, а блок 1 - сигнал СПВ, тем самым в блоке 2 снимается сигнал ВПВ и вырабатывается сигнал ВТПР, который держится низким уровнем до тех пор, пока второй процессор не приступит к программе обработки прерывания и не выдает сигнал ВППР. Цикл обмена информации окончен, аналогично происходит обмен при активизации блока 5 процессором.

При поступлении сигналов "Откл. АМ" на блоки 3 и 4 обмен информацией по системной магистрали прекращается, а блок 4 переходит в состояние с высоким выходным сопротивлением.

Блок захвата системной магистрали работает следующим образом.

С блока 5 поступает сигнал ТРБ на входы триггеров 7 и 8 и на вход элемента И-НЕ 13 и на вход сброса триггера 9, происходит разблокировка триггеров 7-9. На выходе элемента И-НЕ 13 формируется низкий уровень сигнала, который усиливается на буферном элементе 21 и поступает в арбитр 6 магистрали по линии СТПД. По приходе сигнала СППД 1 с арбитра 6 магистрали на вход С триггера 7 он устанавливается в единичное состояние, сигнал с выхода триггера 7 поступает на вход элементов И-НЕ 10 и 11.

При условии, что предыдущие циклы обмена по системной магистрали окончены, т. е. сигналы ССИА и СТСС находятся в высоком уровне, на выходе элемента И-НЕ 10 формируется отрицательный фронт сигнала, поступающий на вход триггера 8, и он переворачивается в состояние с высоким логическим уровнем по выходу.

Сигнал с прямого выхода триггера 8 поступает на вход элемента И-НЕ 11, на второй вход которого поступает высоким уровнем сигнал с прямого выхода триггера 7. На выходе элемента И-НЕ 11 формируется сигнал низким уровнем, который через буферный элемент 20 поступает на линию СПВ, информируя арбитр магистрали о захвате магистрали, а также информируя блок 2 другого модуля о необходимости захвата внутренней магистрали своего процессора. С инверсного выхода триггера 8 сигнал низким уровнем поступает на вход элемента И-НЕ 13, переводя его выход в состояние с высоким уровнем, который проходит через буферный элемент 21 и информирует по линии СТПД арбитр магистрали об окончании цикла захвата системной магистрали.

По приходе положительного фронта сигнала ВСИА, проходящего через инвертор 18, происходит перевод в состояние с высоким уровнем, который, проходя через буферный элемент 22 с инверсией, формирует сигнал "АМ активен", информируя блок 3 о переводе его в режим формирования сигналов управления активного режима работы данного процессора по системной магистрали.

С инверсного выхода триггера 7 происходит по входу элемента И-НЕ 12 блокировка его по выходу, т. е. на выходе элемента И-НЕ 12 сохраняется высокий уровень сигнала СППДО. В случае, если сигнал ТРБ находится в низком уровне, а сигнал СППД 1 приходит на вход триггера 7 тоже низким уровнем, через время Т на выходе элемента задержки 19 формируется сигнал высокого уровня, который, собранный с сигналом высокого уровня с инверсного выхода триггера 7, формирует сигнал СППДО низким уровнем. Это происходит в том случае, если сигнал СТПД выработан блоком 1 другого модуля, являющегося менее приоритетным.

Сигнал низкого уровня с инверсного выхода триггера 8 поступает на линию СПВТ. По окончании обмена блок 5 устанавливает на входе ТРБ низкий уровень, переводя блок 1 в исходное состояние: СПВ, СТПД, СПВТ, АМ активен, СППДО - состояние с высоким уровнем.

Работа блока 2 захвата внутренней магистрали начинается по приходе сигнала СПВ низким уровнем на вход элемента И-НЕ 38, при условии, что сигнал на входе СПВТ, приходящий на вход элемента И 34 и вход элемента И-НЕ 32, находится в состоянии высокого уровня, т. е. сигнал СПВ выработан блоком 1 другого модуля, триггер, выполненный на элементах 31 и 32, находится в данный момент в состоянии высокого уровня по выходу элемента 31, так как до прихода низкого уровня к входу СПВ на нем был высокий уровень, который через элемент 38 поступил низким уровнем на вход элемента И-НЕ. На входе установки также поддерживается состояние высокого уровня. Таким образом по приходе низкого уровня сигнала СПВ происходит передача высокого уровня сигнала, поступающего с элемента И 34 на вход триггеров 23, 24 и 1-й вход элемента И 35.

С выхода буферного элемента 26 с инверсией поступает сигнал низкого уровня на линии ВТПД в процессор, информируя его о требовании захвата его внутренней магистрали и о приостановке его действий. Этот сигнал формируется высоким уровнем на выходе элемента И 35 при условии, что на его входах, связанных с выходами элементов И 34 и И-НЕ 31 и инверсным выходом триггера 24, находятся высокие уровни сигнала. По приходе из процессора сигнала ВППД 1 на вход С триггера 23, информирующего устройство о начале цикла захвата внутренней магистрали, происходит перевод триггера 23 в состояние с высоким уровнем по выходу и блокировка элемента И-НЕ 33 приходом низкого уровня с инверсного выхода триггера 23 на один из входов элемента И-НЕ 33.

По установлении высоких уровней сигналов ВСИП и ВСИА, поступающих на второй и третий входы элемента И-НЕ 30, на его выходе формируется сигнал низкого уровня, отрицательный фронт которого переводит триггер 24 в состояние с высоким уровнем по прямому выходу, сигнал с которого через буферный элемент с инверсией 27 поступает низким уровнем на линию СТСС, через буферный элемент 28 с инверсией - на линию "АМ активен", через буферный элемент 29 с инверсией - на линию ВПВ. С инверсного выхода триггера 24 сигнал низким уровнем поступает на вход элемента И 35, переводя его выход в состояние с низким уровнем, и сигнал по линии ВТПД в состояние с высоким уровнем.

Таким образом осуществляется захват внутренней магистрали процессора и переход блока 3 в режим управления МПП при "пассивном" процессоре.

При переводе сигналом СПВ блока 1 "активного" модуля в состояние с высоким уровнем производится установка блока 2 в исходное состояние, а кроме того, формируется сигнал ВТПР низким уровнем по приходе отрицательного фронта на вход С триггера 25 с прямого выхода триггера 24. Сигнал ВТПР информирует процессор об окончании работы в пассивном режиме.

По приходе сигнала низкого уровня по сигналу ВППР или по сигналу "Установка" на вход элемента И 36 триггер 25 устанавливает в исходное состояние высокого уровня сигнал ВТПР. В случае прихода сигнала ВППД 1 при отсутствии сигнала высокого уровня на входе триггера 24 на выходе элемента И 33 по линии ВППДО формируется сигнал низкого уровня при наличии сигнала высокого уровня на выходе линии задержки 37.

Элементы И-НЕ 31 и И-НЕ 32 предназначены для предотвращения ложной выработки сигнала ВТПД в активный процессор при окончании обмена по системной магистрали. Это может происходить в случае, если блок 1 (1) сигнал СПВТ уже установил в высокий уровень, а сигнал СПВ за счет каких-либо паразитных емкостей по линиям не достиг состояния с высоким уровнем. Такое состояние эквивалентно началу цикла захвата внутренней магистрали в пассивном режиме работы, которого на самом деле не должно быть. Это достигается тем, что в момент наличия сигнала низкого уровня на вход СПВТ (модуль "активный") триггера, выполненного на элементах 32, 31, он запоминает это состояние, устанавливая блокировку выдачей сигнала ВТПД низким уровнем по одному из входов элемента И 35, и даже при переводе сигнала СПВТ в состояние высокого уровня эта блокировка сохраняется до тех пор, пока не перейдет в состояние высокого уровня сигнал на линии СПВ. Тем самым предотвращается ложный переход из состояния "активный" в состояние "пассивный".

Арбитр магистрали работает следующим образом.

В исходном состоянии на входе СПВ сигнал высокого уровня, на входе СТПД - сигнал высокого уровня, на выходе элемента И-НЕ 59 на линии СППД АМ формируется сигнал высокого уровня. При появлении сигнала низкого уровня на входе элемента НЕ 60 (СТПД) на выходе элемента И-НЕ 59 формируется сигнал низкого уровня и держится до тех пор, пока к второму входу элемента И-НЕ 59 не придет сигнал СПВ низким уровнем.

Блок 3 работает следующим образом.

На вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 42 с инверсией поступает сигнал "АМ активен", устанавливая режим передачи сигнала через элемент либо с инверсией, либо без инверсии. Аналогично режимом передачи сигнала элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 43 управляет сигнал "АМ пасссивен". С элемента 42 и 43 поступают сигналы СО1 СДА и СО2 СДА всегда в противофазе, за исключением случая, когда не инициирован ни один режим: ни активный, ни пассивный. На вторые входы элементов 42 и 43 поступает с инвертора 49 сигнал "ВЫВОД", определяющий направление передачи информации по системной магистрали, причем при наличии либо при отсутствии сигнала ввода будет в противофазе.

С дешифратора 39 сигнал низкого уровня, вырабатываемый при совпадении адреса на внутренней магистрали адресному пространству зоны обмена по системной магистрали (запись информации в дешифратор 39 производится по сигналу ВСИА), поступает на входы элемента И-НЕ 44, на выходе которого формируется сигнал низкого уровня только тогда, когда присутствует сигнал низкого уровня на входе, соединенном с дешифратором 39, либо на входе, соединенном с выходом элемента НЕ 49 (инверсия сигнала ввода). С выхода элемента И-НЕ 44 сигнал низкого уровня поступает на вход элемента И-НЕ 45, на другой вход которого поступает проинвертированный элементом 50 сигнал "Откл. АМ", а выход элемента 45 поступает на вход выборки кристалла. Получается сигнал, при которой магистральные приемопередатчики адресов и данных будут открыты до тех пор, пока отсутствует сигнал "ВЫВОД", либо когда присутствует сигнал низкого уровня с дешифратора 39, т. е. когда идет цикл обмена информацией по системной магистрали.

Управление магистральными приемопередатчиками по выбору кристалла по сигналам ССИП и СОШБ осуществляется сигналом с выхода элемента И-НЕ 47 низким уровнем, который вырабатывается только тогда, когда на его входах присутствуют сигналы высокого уровня, проинвертированный на элементе 48 сигнал с дешифратора 39, проинвертированный на элементе 50 сигнал "Откл. АМ" и сигнал высокого уровня с элемента И-НЕ 46, на выходе которого он присутствует при наличии хотя бы одного из сигналов "В ВЫВОД", "В ВВОД" и ВСИП.

Блок магистрали приемопередатчиков 4 включает три группы МПП: МПП данных - адреса, осуществляющих физическое сопряжение магистралей данных и адресов внутренней магистрали с системой, на входы/выходы которой с той и другой стороны поступают сигналы об адресах и данных передаваемой и принимаемой информации.

МПП по сигналам управления осуществляет информационное сопряжение сигналов ВСНА с ССИА, В ВВОД с ВВОД, с ВЫВОД с В ВЫВОД, В БАЙТ с С БАЙТ, СВУ с ВВУ соответственно внутренней и системой магистралей, МПП по сигналам ССИП - ВСИП, СОШБ с ВРШБ, МПП по магистрали данных адресов выбираются (открываются) по приходе сигнала CS СДА низким уровнем. Направление передачи определяется наличием сигналов низкого и высокого уровней по входам СО1 СДА и СО2 СДА.

Направление передачи по МПП управления и сигналам ССИП и СОШБ определяется уровнями сигналов по входам "АМ активен" и "АМ пассивен". Открытие МПП управления определяет сигнал "Откл. АМ", поступающий из процессора, и наличие низкого уровня хотя бы на одном из входов СО1 и СО2, на которые поступают сигналы "АМ активен" или "АМ пассивен" на БУМПП.

Блок 5 регистров состояния содержит селектор адреса, на выходе которого формируется сигнал низкого уровня при совпадении информации, приходящей по входу ВДА в момент отрицательного фронта по сигналу СИА с заранее закодированным в селекторе адреса адресом. В селекторе адреса сигналы низким уровнем формируют по выходам чтения или записи соответственно по приходе сигналов низким уровнем на входе "В ВВОД" или "В ВЫВОД" отрицательным уровнем.

С выхода элемента ИЛИ 55, связанного с входом D-триггера 54, осуществляется запись в D-триггер 54 либо низкого уровня, либо высокого уровня в зависимости от уровня в этот момент сигнала по линии ВДА 15, тем самым вырабатывая с выхода D-триггера 54 сигнал ТРБ.

Низким уровнем по входу управления элемента 57 осуществляется чтение сигнала СТСС через ключевой элемент 57 информации по этому сигналу на линию ВДА и далее в процессор, Сигнал низкого уровня на вход С триггера 54 поступает с выхода элемента ИЛИ 55 при наличии низких уровней на обоих входах элемента ИЛИ 55 (CS и запись) с селектора 58 адреса. По окончании циклов записи или чтения селектор 58 адреса формирует сигнал СИП в процессор. (56) Лопатин В. С. , Юрочкин А. Г. , Баранов Н. Д. Адаптер магистралей СМ ЭВМ и микро-ЭВМ "Электроника-60". - Микропроцессорные средства и системы, N 1, 1985.

Фридштанд В. Д. Особенности организации межмашинного обмена в системах на базе микро-ЭВМ "Электроника-60". - Приборы и системы управления, N 10, 1985.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО МЕЖМАШИННОГО ОБМЕНА | 1989 |

|

SU1635782A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство связи в вычислительной системе | 1987 |

|

SU1425700A1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство для сопряжения процессора с общей магистралью | 1988 |

|

SU1606976A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Многопроцессорная система | 1989 |

|

SU1647597A1 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

Изобретение относится к вычислительной технике и может быть использовано при создании многомашинных вычислительных систем. Целью изобретения является повышение скорости межмашинного обмена за счет осуществления прямого доступа процессора одной микро-ЭВМ к ресурсам другой без значительного увеличения аппаратных затрат. Указанная цель достигается тем, что к каждой микро-ЭВМ подключается модуль межмашинного обмена, содержащий блок 1 захвата системной магистрали, блок 2 захвата внутренней магистрали, блок 3 управления магистральными приемопередатчиками, блок 4 магистральных приемопередатчиков, блок 5 регистра состояния. 6 з. п. ф-лы, 7 ил.

Авторы

Даты

1994-02-15—Публикация

1987-12-11—Подача