Изобретение относится к области вычислительной техники, предназначено для параллельного вычисления разрядными срезами сумм парных произведений комплексных чисел и может быть использовано для решения задач цифровой обработки сигналов, решения задач спектрального анализа и гидролокации, систем автоматического управления и др.

Известно арифметическое устройство вычисления суммы произведений А.С. 553613 (СССР), БИ №13, 1977 г., содержащее два регистра множимых, два регистра множителей, регистр суммы множимых, накапливающий сумматор, дешифратор, логические элементы И, ИЛИ.

Признаками аналога, совпадающими с существенными признаками заявляемого изобретения, являются регистры, сумматор.

Недостатком является то, что в устройстве невозможно параллельно вычислить сумму парных произведений комплексных чисел.

Причиной, предшествующей получению технического результата, является низкая степень распараллеливания вычислительного процесса.

Известно также множительное устройство комплексных чисел (Введение в кибернетическую технику. Под редакцией Б.Н.Малиновского. - Киев.: Наукова думка. 1979 г., с.143, рис.46), содержащие регистры, преобразователь кодов, коммутаторы, дешифратор, сумматоры.

Признаками аналога, совпадающими с существенными признаками заявляемого изобретения, являются регистры, сумматоры.

Недостатком является то, что в устройстве невозможно параллельно вычислить сумму парных произведений комплексных чисел.

Причиной, препятствующей получению технического результата, является низкая степень распараллеливания вычислительного процесса.

Наиболее близким является устройство цифровой обработки сигналов разрядными срезами PIPE (Е.Ф.Очин. Вычислительные системы обработки изображений - Л.: Энергоатомиздат. 1988, с.74, рис.4.5), содержащие регистры, регистры преобразования кодов, сдвигатель-аккумулятор, мультиплексор адреса, программируемое ПЗУ.

Признаками прототипа, совпадающими с существенными признаками заявляемого изобретения, являются регистры.

Недостатком является ограничения функциональных возможностей, т.к. в известном устройстве обработки сигналов невозможно параллельно вычислять разрядными срезами сумму парных произведений комплексных чисел.

Причиной, препятствующей получению требуемого технического результата, является низкая степень распараллеливания вычислительного процесса.

Задача, на решение которой направленно предлагаемое изобретение, заключается в создании устройства параллельного вычисления разрядными срезами суммы М парных произведений комплексных чисел.

Технический результат, достигаемый при осуществлении изобретения, состоит в расширении функциональных возможностей, повышении быстродействия вычисления суммы М парных произведений комплексных чисел.

Для достижения указанного технического результата в вычислительное устройство, содержащее регистры, введены сумматор-вычислитель, два блока матричных вычислителей сумм произведений, каждый из которых содержит матричный сумматор, параллельные преобразователи равновесных кодов в позиционные коды, М-матричных умножителей, каждый из которых содержит регистр множимого и регистр множителя, входы которых подключены ко входам устройства, (n+1) групп по (n+1) элементов И выделения весовых разрядных произведений, (n+1) элементов И выделения корректирующих разрядных произведений по знаку множителя, группы элементов И выделения корректирующих разрядных произведений по знаку множимого. При этом одни входы (n+1) элементов И выделения весовых разрядных произведений соединены с выходами выдачи значащих разрядов регистра множителя, вторые входы этих элементов И соединены с выходами выдачи значащих разрядов регистра множимого. Одни входы (n+1) элементов И выделения корректирующих разрядных произведений по знаку множителя соединены через инверторы с выходами выдачи значащих разрядов регистра множимого, вторые входы (n+1) элементов И соединены с выходом регистра выдачи знакового разряда множителя. При этом одни входы группы элементов И выделения корректирующих разрядных произведений по знаку множимого соединены с выходами значащих разрядов регистра множителя, вторые входы группы элементов И соединены с выходом выдачи знакового разряда регистра множимого. При этом выходы элементов И выделения весовых разрядных произведений с равными весами и выходы элементов И выделения корректирующих разрядных произведений подключены соответствующим образом ко входам преобразователей кодов. Выходы преобразователей кодов соединены со входами матричного сумматора соответствующим образом.

Выходы матричных сумматоров соединены соответственно со входами сумматора-вычитателя, выходы которого соединены с выходом устройства.

Причинно-следственная связь между совокупностью признаков заявленного изобретения и достигаемым техническим результатом заключается в следующем: введение М-матричных умножителей, параллельных преобразователей равновесовых кодов в позиционные коды, соединенных соответствующим образом, позволяет расширить функциональные возможности, повысить быстродействие вычисления суммы М парных произведений комплексных чисел.

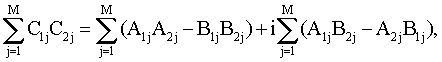

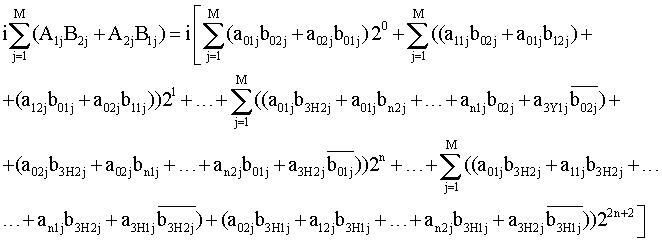

В основу работы устройства положен алгоритм параллельного вычисления разрядными срезами суммы произведений комплексных чисел:

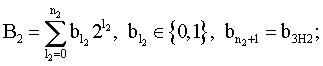

где C1=A1+iB1, C2=A2+iB2 - комплексные числа;

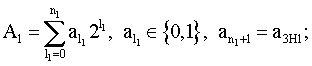

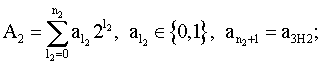

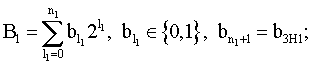

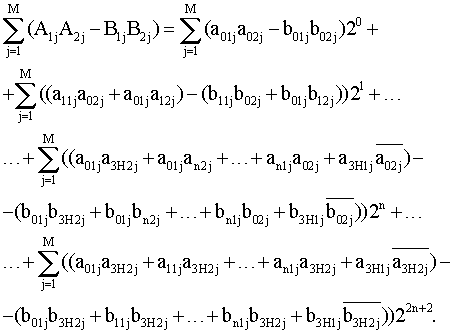

Алгоритм параллельного вычисления разрядными срезами действительной части суммы М-парных произведений комплексных чисел на основе параллельной вертикальной арифметики запишем в виде:

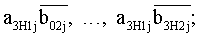

Здесь a01jan2j, ..., an1ja02j; b01jbn2j, ..., bn1jb02j - весовые разрядные произведения; a01ja3H2j; an1ja3H2j, ..., b01jb3H2j; bn1jb3H2j - коррекция разрядных произведений по знакам множимых a3H2j, b3H2j.

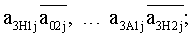

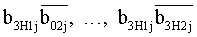

- коррекция разрядных произведений по знакам множителей a3H1j, b3H1j.

- коррекция разрядных произведений по знакам множителей a3H1j, b3H1j.

Алгоритм параллельного вычисления разрядными срезами мнимой части суммы М-парных произведений комплексных чисел запишется в виде:

Здесь a01jbn2j, ..., an1jb02j - весовые разрядные произволения;

a01jb3H2j, ..., an1jb3H2j; a02jb3H1j, ..., an2jb3H1j - коррекция разрядных произведений по знакам множимых b3H1j, b3H2j;

- коррекция разрядных произведений по знакам множителей a3H1j, a3H2j.

- коррекция разрядных произведений по знакам множителей a3H1j, a3H2j.

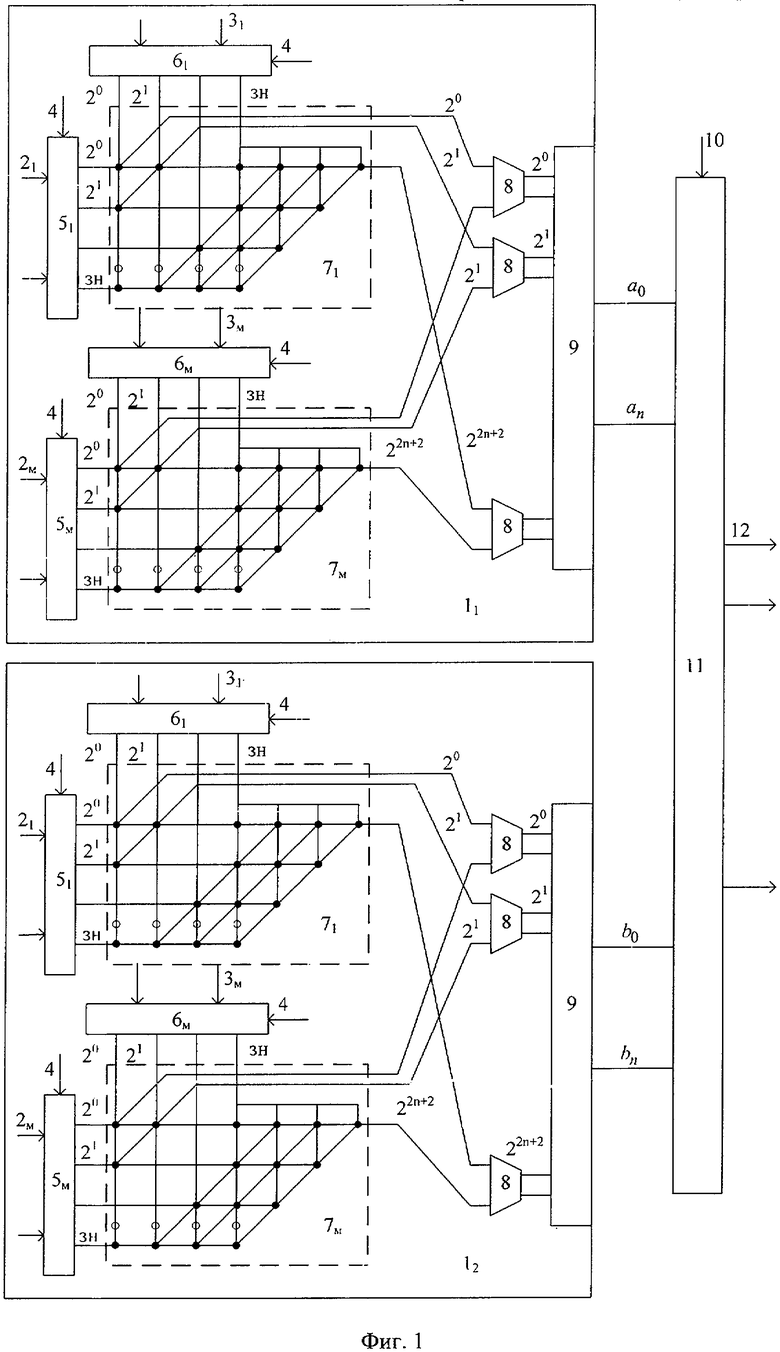

Сущность предлагаемого изобретения поясняется устройством вычисления сумм произведений, приведенным на фиг.1.

Устройство вычисления (фиг.1) содержит:

11 - первый блок вычисления сумм произведений;

12 - второй блок вычисления сумм произведений;

21, ..., 2м - информационные входы приема параллельными кодами множителей a01, a11, ..., a3H1j; a02j, a12j, ..., a3H2j; b01j, b11j, ..., b3H1j,  ;

;

31, ..., 3м - информационные входы приема параллельными кодами множимых b01j, b11i, ..., b3Hj; b02j, b12j, ..., b3H2j; aj, a12j, ..., a3H2j,  ;

;

4 - управляющий вход поступления импульса записи;

51-5м - регистры множителей с информационными выходами выдачи параллельными кодами значащих и знаковых разрядов множителей (на фиг.1 обозначены, как: 20, 21, ..., 3н);

61-6м - регистры множимых с информационными выходами выдачи параллельными кодами значащих и знаковых разрядов множимых (на фиг.1 обозначены, как: 20, 21, ..., 3н);

71-7м - матричные умножители;

8 - преобразователи равновесных кодов в позиционные коды;

9 - матричные (параллельно- параллельные) сумматоры;

10 - управляющий вход, поступления режимного признака вычтания ПВЧ=1; суммирования ПВЧ=0;

11 - многоразрядный сумматор-вычитатель;

12 - информационные выходы, выдачи параллельным кодом результата вычисления.

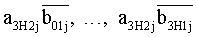

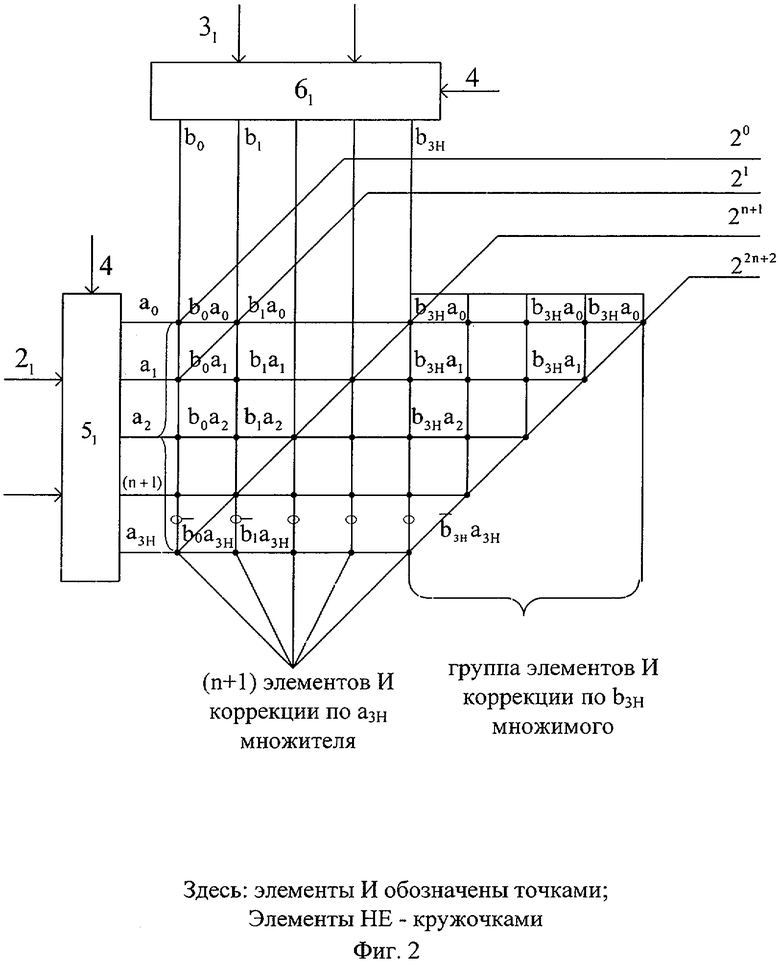

Матричный умножитель (Фиг.2) состоит из: регистра множителя (51, ..., 5м); информационных входов приема множителей (21); регистра множимого (61, ..., 6м); информационных входов приема множимых (31); управляющего входа, поступления импульса записи (4);

(n+1) групп (n+1) элементов И (элементы И обозначены точками) выделения весовых разрядных произведений, (n+1) элементов И выделения разрядных корректирующих разрядных произведений по знаку множителя; группы элементов И выделения корректирующих разрядных произведений по знаку множимого; (n+1) элементов НЕ (элементы НЕ обозначены кружочками).

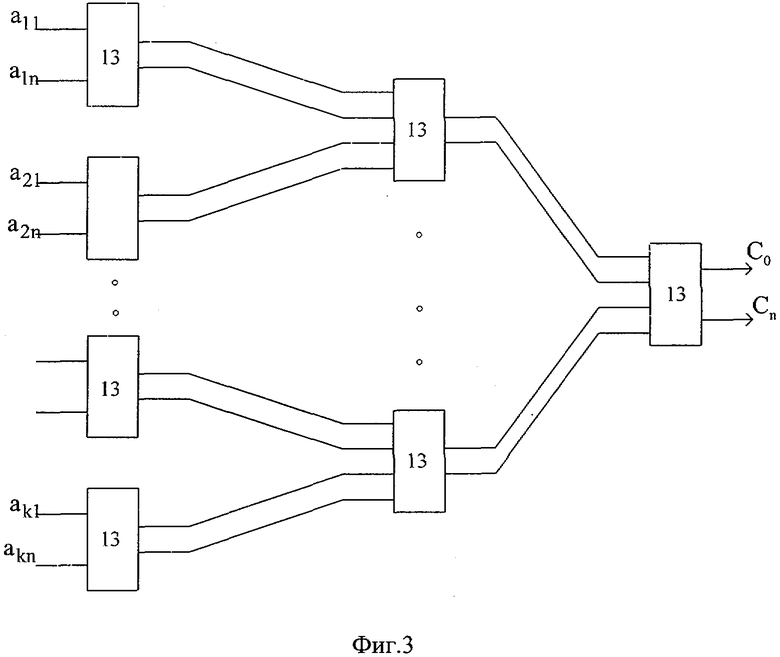

Матричный (параллельно-параллельный) сумматор (Фиг.3) описан (Введение в кибернетическую технику. Под редакцией Б.Н.Малиновского. Киев.: Наукова думка. 1979, с.118, рис.33), состоит из L-рядов комбинационных параллельных сумматоров (13), L=]log2K[, ]log2K[ - округление до ближайшего большего целого величины log2K, имеет входы а11, ..., а1n, ..., аk1, ..., аkn приема позиционных кодов, выходы с0, ..., cn выдачи результата.

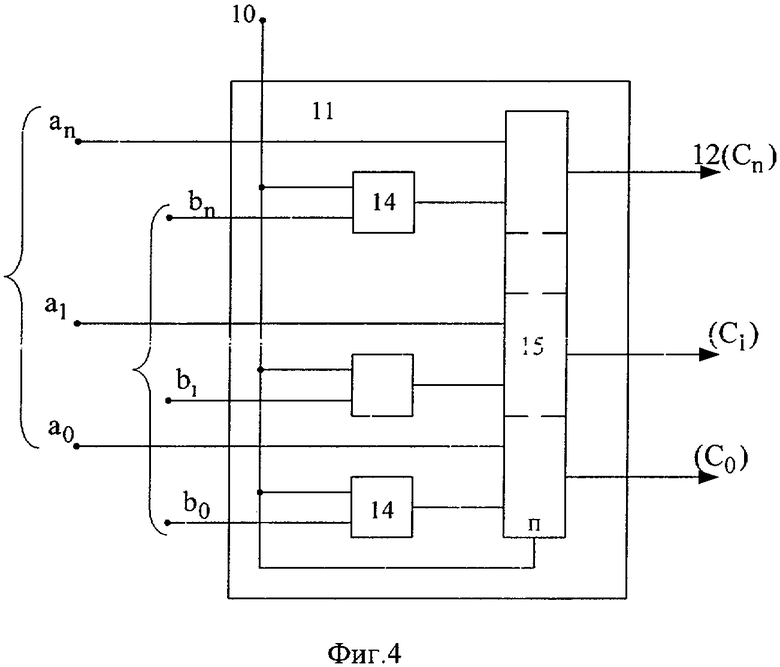

Сумматор-вычитатель (Фиг.4) описан (Г.И.Пухальский, Т.Я.Новосельцева. Цифровые устройства. Санкт-Петербург: Политехника, 1996, с.531, рис.6.104б) состоит из сумматоров по модулю два 14, многоразрядного сумматора 15, имеет входы a0...an приема первых слагаемых (уменьшаемых), входы b0, ... bn приема вторых слагаемых (вычитаемых), выходы с0...cn выдачи результата, управляющий вход (10), поступления признаков режимов вычитания (ПВЧ=1) или суммирования (ПВЧ=0).

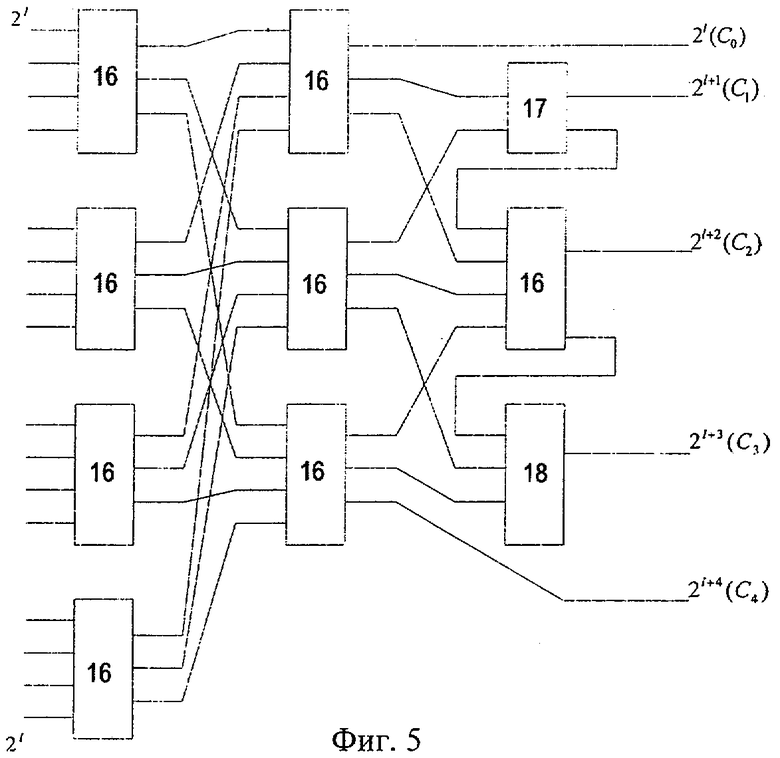

Параллельный преобразователь равновесных кодов в позиционные коды (узел одноразрядного суммирования) (Фиг.5) описан (Авт. Свид. 1557684 №14, 1994 г. или патент SU 1679483 A1, кл. G06F, 1995 г.) состоит из четырех входовых элементов суммирования 16, полусумматора 17, элементы ИЛИ 18 имеет входы 2l приема равновесных разрядов, выходы 2l(C0), 2l+1(С1), ..., 2l+4(С4) выдачи результата.

Поясним принцип работы устройства вычисления сумм произведений (Фиг.1). Для параллельного вычисления разрядными срезами действительной части суммы М-парных произведений комплексных чисел предварительно записываются в регистры множителей 51, ..., 5M первого блока 11 по импульсу записи, поступающему на вход 4, действительные a01j, a11j, ..., а3H1j части j-комплексных чисел,  , а в регистры множимых 61, ...,6М записываются действительные a02j, а12j, ..., а3Н2j части j-комплексных чисел.

, а в регистры множимых 61, ...,6М записываются действительные a02j, а12j, ..., а3Н2j части j-комплексных чисел.

В регистры множителей 51, ..., 5М второго блока (12) записываются мнимые b01j, b11j, ..., b3H1j части j-комплексных чисел, а в регистры множимых 61, ..., 6М записываются мнимые b02j, b12j, ..., b3Н2j части j-комплексных чисел.

Для параллельного вычисления разрядными срезами мнимой части суммы М-парных произведений комплексных чисел предварительно записываются в регистры множителей 51, ..., 5М первого блока 11 по импульсу записи, поступающему на вход 4, действительные а01jа11j, ..., а3H1j части j-комплексных чисел, а в регистры множимых 61, ..., 6М записываются мнимые b02j, b12j, ..., b3H2j части j-комплексных чисел.

В регистры множителей 51, ..., 5М второго блока 12 записываются действительные a02ja12j, ..., a3H2j части j-комплексных чисел, а в регистры множимых 61, ..., 6М записываются мнимые b02j, b12j, ..., b3Н2j части j-комплексных чисел.

В множительных матрицах 71, ..., 7М первого и второго блоков параллельно вычисляются элементами И разрядные произведения (фиг.1).

Принцип формирования элементами И множительной матрицы равновесных разрядных произведений поясняется примером

Здесь b0a020, b1a021, b1a122, ..., b3a326 - весовые разрядные произведения;

b3Hа0, b3Hа1, ..., b3Hа3 - корректирующие разрядные произведения по знакам множимого (b3H);

- корректирующие разрядные произведения по знакам множителя (a3H).

- корректирующие разрядные произведения по знакам множителя (a3H).

Весовые и корректирующие разрядные произведения формируются элементами И (условно обозначены элементы И в множительной матрице точками) и выдаются (по диагональным шинам) из матричных умножителей 71...7М на входы соответствующих преобразователей кодов (8) в виде равновесных кодов (равновесные разряды) с весами 20, ..., 22n+2 (фиг.1).

В преобразователях кодов 8 формируются разрядные суммы. Результаты из преобразователей кодов 8 подаются параллельно на входы матричных сумматоров 9, в которых вычисляются суммы произведений.

В многоразрядном вычитателе 11 по признаку Пвч=1, поступающему на вход 10, параллельно вычисляется действительная часть суммы М-парных произведений комплексных чисел в виде  , а по признаку Пвч=0 параллельно вычисляется мнимая часть суммы М-парных произведений комплексных чисел в виде:

, а по признаку Пвч=0 параллельно вычисляется мнимая часть суммы М-парных произведений комплексных чисел в виде:

Введение в устройство новых элементов параллельных преобразователей кодов, М-матричных умножителей, соединенных соответствующим образом, позволяет расширить функциональные возможности, повысить быстродействие на порядок по сравнению с известным вычислительным устройствами за счет высокой степени распараллеливания вычислительного процесса до уровня разрядных сумм.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU550637A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения | 1985 |

|

SU1290301A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

Изобретение относится к вычислительной технике, предназначено для параллельного вычисления разрядными срезами сумм парных произведений комплексных чисел и может быть использовано для решения задач цифровой обработки сигналов, решения задач спектрального анализа и гидролокации, систем автоматического управления. Техническим результатом является расширение функциональных возможностей, повышение быстродействия. Устройство содержит сумматор-вычитатель, два блока вычисления сумм произведений, каждый из которых состоит из регистров множителей, регистров множимых, матричных умножителей, преобразователей равновесных кодов в позиционные коды, матричных сумматоров. 5 ил.

Устройство вычисления сумм произведений, содержащее сумматор-вычитатель, два блока матричных вычислителей сумм произведений, каждый из которых содержит матричный сумматор, параллельные преобразователи равновесных кодов в позиционные коды, М-матричных умножителей, каждый из которых содержит регистр множимого и регистр множителя, входы которых подключены ко входам устройства, (n+1) групп по (n+1) элементов И выделения весовых разрядных произведений, (n+1) элементов И выделения корректирующих разрядных произведений по знаку множителя, группы элементов И выделения корректирующих разрядных произведений по знаку множимого, при этом одни входы (n+1) элементов И выделения весовых разрядных произведений соединены с выходами выдачи значащих разрядов регистра множителя, вторые входа этих элементов И соединены с выходами выдачи значащих разрядов регистра множимого, одни входы (n+1) элементов И выделения корректирующих разрядных произведений по знаку множителя соединены через инверторы с выходами выдачи значащих разрядов регистра множимого, вторые входы (n+1) элементов И соединены с выходом регистра выдачи знакового разряда множителя, при этом одни входы группы элементов И выделения корректирующих разрядных произведений по знаку множимого соединены с выходами выдачи значащих разрядов регистра множителя, вторые входы группы элементов И соединены с выходом выдачи знакового разряда регистра множимого, при этом выходы элементов И выделения весовых разрядных произведений с равными весами и выходы элементов И выделения корректирующих разрядных произведений подключены соответствующим образом ко входам преобразователей кодов, выходы преобразователей кодов соединены со входами матричного сумматора соответствующим образом, выходы матричных сумматоров соединены соответственно со входами сумматора-вычитателя, выходы которого соединены с выходом устройства.

| ОЧИН Е.Ф | |||

| Вычислительные системы обработки изображений | |||

| - Л.: Энергоатомиздат, 1988, с.74, рис.4.5 | |||

| МНОГОУРОВНЕВАЯ M-МЕРНАЯ МАТРИЧНАЯ ВЫЧИСЛИТЕЛЬНАЯ СТРУКТУРА ВЕРТИКАЛЬНОЙ АРИФМЕТИКИ В.М. ТАРАНУХИ | 2003 |

|

RU2265239C2 |

| Арифметическое устройство | 1976 |

|

SU553613A1 |

| Устройство для вычисления суммы произведений двух массивов чисел | 1980 |

|

SU985782A1 |

| JP 9153028, 10.06.1997. | |||

Авторы

Даты

2007-09-20—Публикация

2006-02-13—Подача