1

(21)4680824/24

(22)18.04.89

(46) 23.04.91. Бюл. 15

(72) В.В.Куванов, В.В.Андриенко

и А.Г.Ручко

(53) 681.325 (088.8)

(56)Авторское свидетельство СССР №,855651, кл. Н 03 М 9/00, 1979. (54)ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ

(57)Изобретение относится к вычислительной технике и автоматике, а именно к устройствам для преобразования параллельного кода в последовательный, удовлетворяющим требованиям

контролепригодности аппаратуры и повышенной надежности. Цель иэобрете- ния - расширение функциональных возможностей за счет обеспечения контроля преобразования и повышение надежности. Преобразователь содержит N регистров сдвига, выходной мультиплексор 2, элемент ИЗ, контрольный регистр 4, группу из N+1 элементов И 5, управляющий дешифратор 6, входной счетчик 7, первый 8 и второй 9 управляющие счетчики, контрольный мультиплексор 10 и адресный дешифратор 11. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1979 |

|

SU855651A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Преобразователь последовательного биполярного кода в параллельный униполярный код | 1989 |

|

SU1695511A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

Изобретение относится к вычислительной технике и автоматике и предназначено для использования в различного типа счетно-решающих устройствах, системах и приборах автоматического контроля и регулирования, а также в других устройствах, осуществляющих преобразование дискретной информации.

Цель изобретения - расширение функциональных возможностей за счет возможности контроля преобразования и повышение надежности преобразователя.

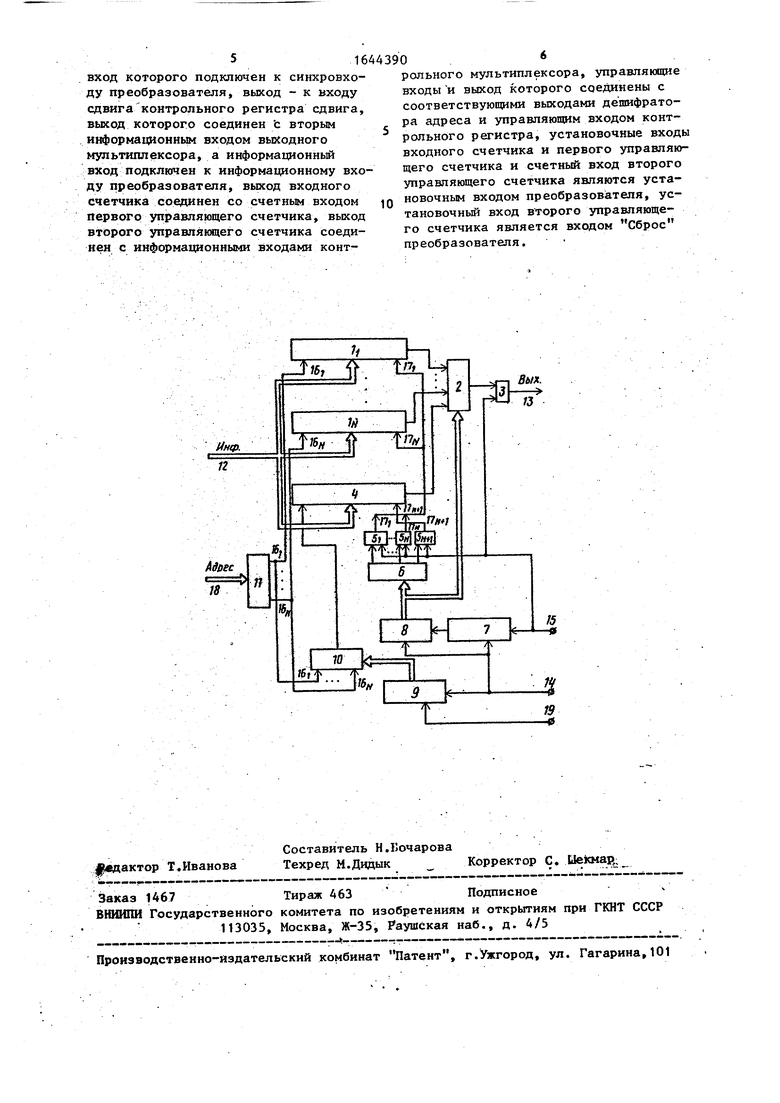

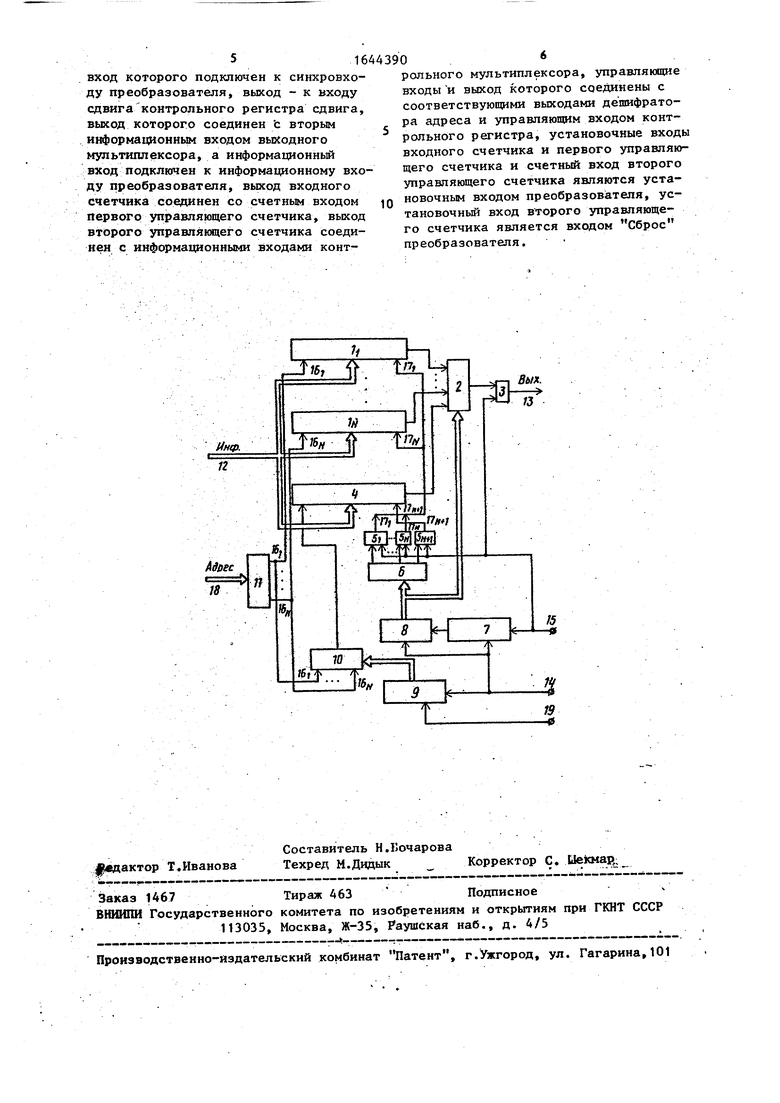

На чертеже представлена функциональная схема преобразователя.

Преобразователь содержит N реги- стров 1|-1н сдвига, выходной мультиплексор 2, элемент И 3, контрольный регистр 4 сдвига, группу из N+1 элементов И 5,-5н+1, управляющий дешифратор 6, входной счетчик 7, первый 8 и второй 9 управляющие счетчики,

контрольный мультиплексор 10, адресный дешифратор 11(реализованные, например, -элементами серии 533, 134). На чертеже также показаны информационный вход 12, выход 13, установочный вход 14, синхровходы 14 и 15, управляющие входы 16 и входы сдвига 17, адресный вход 18 и вход Сброс 19.

Преобразователь работает следующим

образом.

Первоначально по входу 19 подается сигнал, который устанавливает второй управляющий счетчик 9 в исходное состояние, при котором выходы счетчика переключают контрольный мультиплексор 10 на прохождение адреса первого регистра 1. Затем по входу 12 поступает массив информации, сопровождаемый адресами, по которым с помощью дешифратора 11 осуществляется запись информации в соответствующие

ОЭ

регистры у. При этом информация, предназначенная для первого регистра If записывается в контрольный регистр 4, так как контрольный мультиплексор 10 открыт для адресного сигнала первого регистра 1j(. После записи информации в регистры ц происходит процесс ее чтения из них в последовательном коде. По входу 14 поступает сигнал, модифицирующий состояние второго управляющего счетчика 9, после чего выходы открывают контрольный мультиплексор 10 для прохождения адресного сигнала второго регистра 1. Одновременно сигнал по входу 14 устанавливает в исходное состояние входной 7 и первый 8 управляющий счетчики. В исходном состоянии первый управляющий счетчик 8 открывает выходной мультиплексор 2 для прохождения сигнала с выхода первого регистра 1, а также с помощью управляющего дешифратора 6 открывает первый элемент И 5 4 из группы элементов И для прохождения импульсо с синхровхода 15 на сдвиговый вход сдвига первого регистра 1 . На синх- ровход 15 поступает N+1 пачек импульсов с количеством в каждой пачке, равным числу разрядов в каждом регистре . Первая пачка импульсов осуществляет сдвиг первого регистра 1j, одновременно стробируя выходной сигнал выходного мультиплексора 2 на элементе И 3 и просчитываясь на входном счетчике 7. Последний импульс пачки появляется на выходе Перенос входного счетчика 7 и по заднему фронту модифицирует состояние первого управляющего счетчика 8, что приводит к открыванию второго элемента И 5я из группы (N+1) элементов И.

Вторая пачка импульсов будет поступать на сдвиговый вход второго сдвигового регистра 1- и осуществлять его сдвиг, одновременно строби руя выдвигаемую информацию на элементе И 3. Последний импульс пачки модифицирует первый управляющий счетчик 8, открывая вход следующего элемента И из группы N+1 эпементов И При поступлении следующей пачки им- пульсов процесс повторяется. Таким

образом, при поступлении N+1 пачек импульсов информация.с (N+1)-ro регистра будет выдана последовательным кодом на выход 13. При этом информации с первого регистра 1i

0

5

0

5

0

5

0

5

(первое слово) и с контрольного сдвигового регистра 4 (последнее слово) должны совпадать. Их совпадение является признаком исправности первого тракта преобразования. При записи нового массива информации в контрольный регистр 4 записывается информация второго регистра 1. Процедура выдачи информации второго массива аналогична описанной выше. В выдан - ном массиве информации второго и последнего слов должны совпадать. Таким образом, контрольный регистр 4 последовательно циклически обеспечивает дублирование информации каждого тракта преобразования, что позволяет осуществлять их контроль методом сравнения. При выявлении неисправности тракта преобразования коит- рольный сдвиговый регистр можно использовать взамен неисправности в каждом N-м тракте обмена.

Формула изобретения Преобразователь параллельного кода в последовательный, содержащий N регистров сдвига, информационные входы которых являются информационным входом преобразователя, выходы соединены с соответствующими первыми информационными входами выходного мультиплексора, выход которого соединен с первым входом первого элемента И, выход которого является выходом преобразователя, дешифратор адреса, входы которого являются адресными входами преобразователя, выходы соединены с управляющими входами соответствующих регистров сдвига, группу из N-элементов И, выводы которых соединены с входами сдвига соответствующих регистров сдвига, первые входы элементов И группы, второй вход первого элемента И и счетный вход входного счетчика объединены и являются синхровходом преобразователя, первый управляющий счетчик, выход которого соединен с управляющими входами выходного мультиплексора, отличающийся тем, что, с целью расширения функциональных возможностей преобразователя за счет обеспечения контроля преобразования и повышения его надежности, в него введены контрольный регистр сдвига, контрольный мультиплексор, второй управляющий счетчик, управляющий дешифратор и в группу элементов И - (N+O -й элемент И, первый

вход которого подключен к синхровхо- ду преобразователя, выход - к входу сдвига контрольного регистра сдвига, выход которого соединен с вторым информационным входом выходного мультиплексора, а информационный вход подключен к информационному входу преобразователя, выход входного счетчика соединен со счетным входом первого управляющего счетчика, выход второго управляющего счетчика соединен с информационными входами конт

рольного мультиплексора, управляющие входы и выход которого соединены с соответствующими выходами дешифратора адреса и управляющим входом контрольного регистра, установочные входы входного счетчика и первого управляющего счетчика и счетный вход второго управляющего счетчика являются установочным входом преобразователя, установочный вход второго управляющего счетчика является входом Сброс преобразователя.

Авторы

Даты

1991-04-23—Публикация

1989-04-18—Подача