I

(21)4657336/24

(22)01.03.89

(46) 30.04.91. Бюп. № 16

(71)Териопопьский финансово-экономический институт

(72)З.И.Домбровский, М.А.Дуда, В.Н.Немиш и Л.А.Узлова

(53)681.3(088.8)

(56)Авторское свидетельство СССР 1076906, кл. G 06 F 11/00, 1983.

Авторское свидетельство СССР 1425674, кл. G 06 F 11/00, 1987.

(54)КОНТРОЛИРУЕМОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

(57)Изобретение относится к области автоматики и вычислительной техники

, и может быть использовано в узлах обработки цифровой информации повышенной надежности. Цель изобретения - сокращение аппаратурных затрат устройства. Устройство содержит регистры 1 и 2 сдвига, сумматор 3, регистр 4 результата, блок 5 сравнения. Устройство работает в два такта: рабочий и контрольный, определяемых сигналом на входе 6 задания режима работы устройства. В рабочем режиме операнды, поступившие на регистры 1 и 2, складываются сумматором 3 и запоминаются на регистре 4 результата. В контрольном такте операнды циклически сдвигаются на регистрах 1 и 2 сдвига, суммируются сумматором 3 и эта сумма сравнивается с содержимым регистра 4 результата блоком 5 сравнения. I ил., 2 табл.

S 1(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Контролируемое арифметическое устройство | 1987 |

|

SU1425674A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Контролируемое арифметическое устройство | 1982 |

|

SU1076906A1 |

| Арифметическое устройство | 1978 |

|

SU711570A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| ПРОЦЕССОР | 1990 |

|

SU1826787A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297055A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

о

.Ј

ел

со

СЛ

1

Изобретение относится к автоматике и вычислительной технике н может быть использовано в узлах обработки цифровой информации повышенной на-

дежности.

Цель изобретения - сокращение аппаратурных затрат устройства.

На чертеже приведена функциональная схема контролируемого арифмети- ческого устройства.

Предлагаемое устройство содержит регистры 1 и 2 сдвига, сумматор 3, регистр 4 результата и блок 5 сравнения и имеет вход 6 задания режима работы контролируемого арифметического устройства.

Регистры 1 и 2 являются циклическими регистрами сдвига.

Контролируемое арифметическое уст- ройство работает следующим образом.

Работа устройства состоит из двух тактов - рабочего и контрольного. В рабочем такте на вход 6 задания режима работы контролируемого арифмети- ческого устройства подается нулевой сигнал.

На циклические регистры I и 2 сдвига поступают n-разрядные операнды, которые с выходов регистров 1 и 2 подаются на входа первого и второго операндов сумматора 3. Код с выхода суммы п разрядов сумматора 3 записывается в регистр 4 результата. После этого начинается контрольный такт работы устройства и на входе 6 задания режима работы контролируемого арифметического устройства устанавливается единичный сигнал. По этому сигналу происходит сдвиг содержи- мого циклических регистров 1 и 2 сдвига на один разряд в сторону старших разрядов, при этом значение п-х разрядов циклических регистров 1 и 2 сдвига переносится в первые разряды этих регистров. Запись в регистр 4 результата запрещается. В сумматоре 3 производится суммирование поступивших кодов. Результат суммирования снимается с выходов суммы разря- дов с второго по n-й и сравнивается поразрядно на блоке 5 сравнения с содержимым регистра 4 результата.При неравенстве этих кодов на выходе блока 5 сравнения формируется единич- ный гигнал, появление которого в такте контроля означает неисправность контролируемого арифметического устройства.

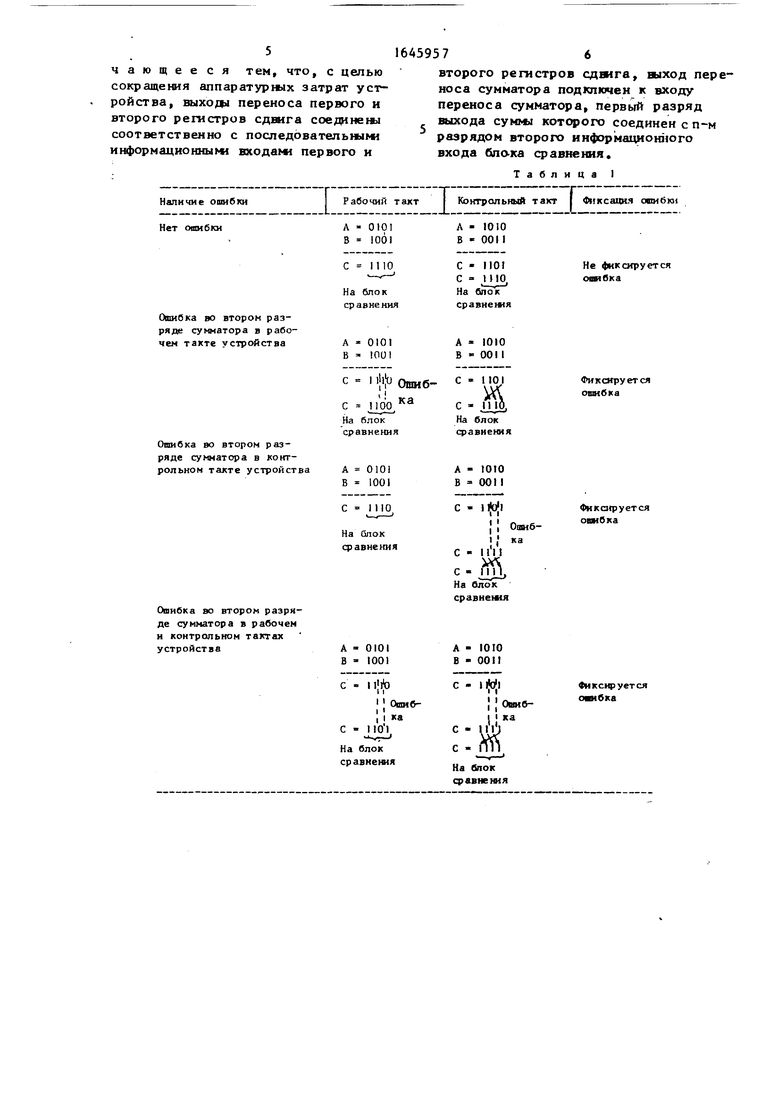

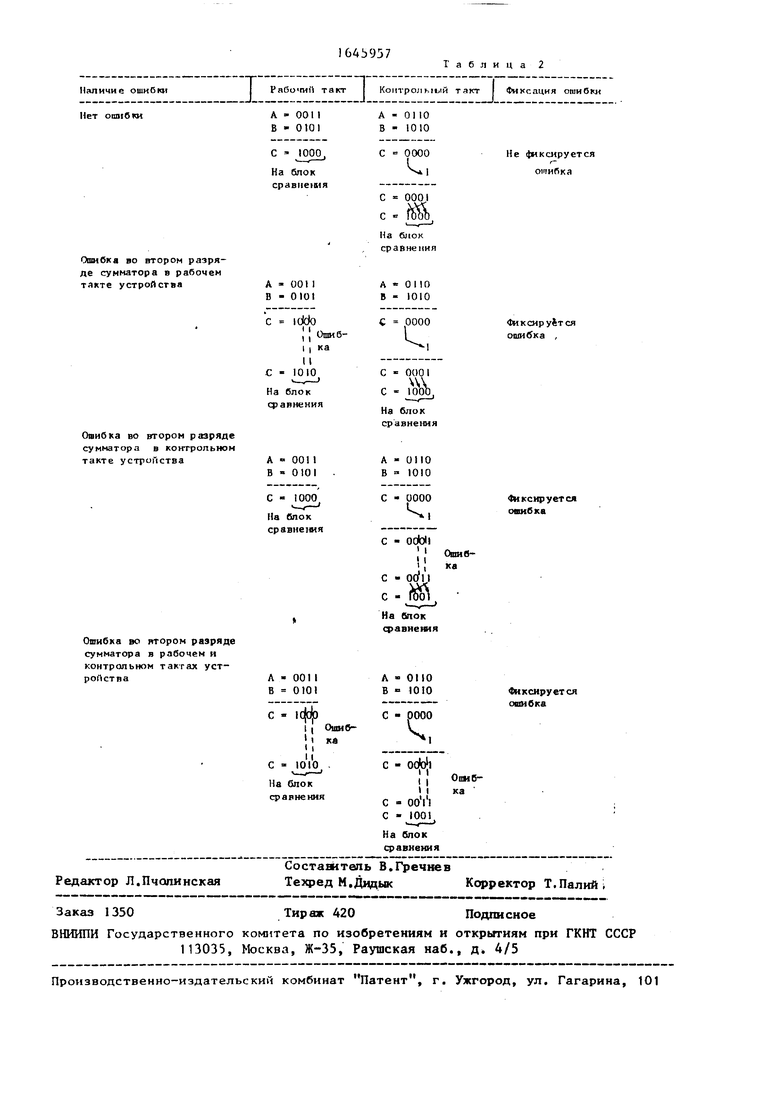

Например, необходимо произвести контроль правильности выполнения операции сложения двух кодов: А и В. При этом, предположим, что при суммировании во втором разряде сумматора возникает ошибка: а) в рабочем такте; б) в контрольном такте; в) в рабочем и контрольном тактах одновременно. Пример 1: А 0101, (табл.1). Пример 2: А 0011,В 0101 (табл.2). Как видно из табл.1 и 2, контролируемое арифметическое устройство фиксирует все вида этих сбое

В регистрах 1 и 2 и сумматоре 3 содержится только по п разрядов, что сокращает аппаратурняе затраты устройства.

Кроме того, устройство обладает хорошими диагностическими способностями, так как позволяет фиксировать сбои, воэникакчдае в рабочем такте, контрольном такте или в рабочем и контрольном тактах одновременно.

Формула изобретения

Контролируемое арифметическое устройство, содержащее два регистра сдвига, сумматор, регистр результата и блок сравнения, причем параллельные информационные входы первого и второго регистров сдвига являются соответственно входами первого и второго операндов контролируемого арифметического устройства, информационные выходы первого и второго регистров сдвига соединены соответственно с входами первого и второго операндов сумматора, выход суммы которого соединен с информационным входом регистра результата, выход которого соединен с первым информационным входом блока сравнения и является информационным выходом контролируемого арифметического устройства, выход несравнения блока сравнения является выходом ошибки контролируемого арифметического устройства, входа сдвига первого и второго регистров сдвига и вход разрешения записи регистра результата подключены к входу задания режима работы контролируемого арифметического устройства, 1-й разряд выхода суммы сумматора соединен с (1-1)-м разря- дом второго информационного входа бло ка ср авнения (2 i п, где п - разрядность операндов), о т л и чающееся тем, что, с целью сокращения аппаратурных затрат устройства, выхода переноса первого и второго регистров сдвига соединены соответственно с последовательным информационным входами первого и

второго регистров сдвиге, выход переноса сумматора подключен к входу переноса сумматора, первый разряд выхода суммы которого соединен с п-м разрядом второго информационного входа бло-ка сравнения.

Таблица I

Авторы

Даты

1991-04-30—Публикация

1989-03-01—Подача