(Л

00

4

4

лов осуществляется деление делимого А, поступающего на входы 12, 13 делимого устройства, на делитель В, поступающий на входы , 15 делителя устройства. И делимое и делитель поступают на входы устройства последовательно, разряд за разрядом, причем каждый разряд имеет три состояния (-1,0 и 1) и кодируется с помощью двух сигналов. Результат деления выдается на информационные выходы 16, 17 устройства. Тактируется работа устройства тремя сериями тактовых им- пульсов, поступающих на тактовые входы 18-20 устройства. Второй, третий арифметические б/юки 5, 6 сумматор 7 и первый элемент ИЛИ 11 контролируют процесс вычисления. Результат контро- ля выдается на выход 21 неисправности устройства, 1 ил., 2 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Устройство для деления чисел | 1987 |

|

SU1441388A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1451682A1 |

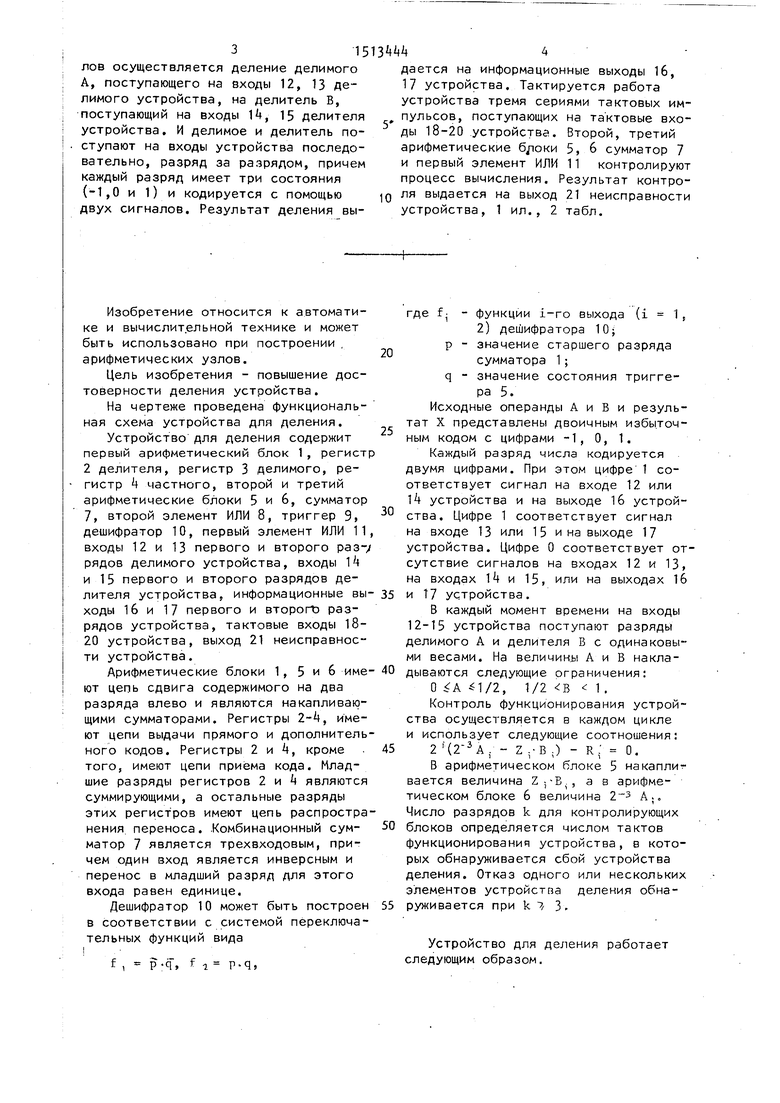

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении арифметических устройств. Цель изобретения - повышение достоверности результата деления устройства. Устройство содержит первый арифметический блок 1, регистр 2 делителя, регистр 3 делимого, регистр 4 частного, второй элемент ИЛИ 8 триггер 9 и дешифратор 10. С помощью этих узлов осуществляется деление делимого А, поступающего на входы 12 13 делимого устройства на делитель В, поступающий на входы 14, 15 делителя устройства. И делимое и делитель поступают на входы устройства последовательно, разряд за разрядом, причем каждый разряд имеет три состояния /-1,0 и 1/ и кодируется с помощью двух сигналов. Результат деления выдается на информационные выходы 16, 17 устройства. Тактируется работа устройства тремя сериями тактовых импульсов, поступающих на тактовые входы 18-20 устройства. Второй, третий, арифметические блоки 5, 6, сумматор 7 и первый элемент ИЛИ 11 контролируют процесс вычисления. Результат контроля выдается на выход 21 неисправности устройства, 1 ил.

20

25

Изобретение относится к автоматике и вычислит.ельной технике и может быть использовано при построении , арифметических узлов.

Цель изобретения - повышение достоверности деления устройства.

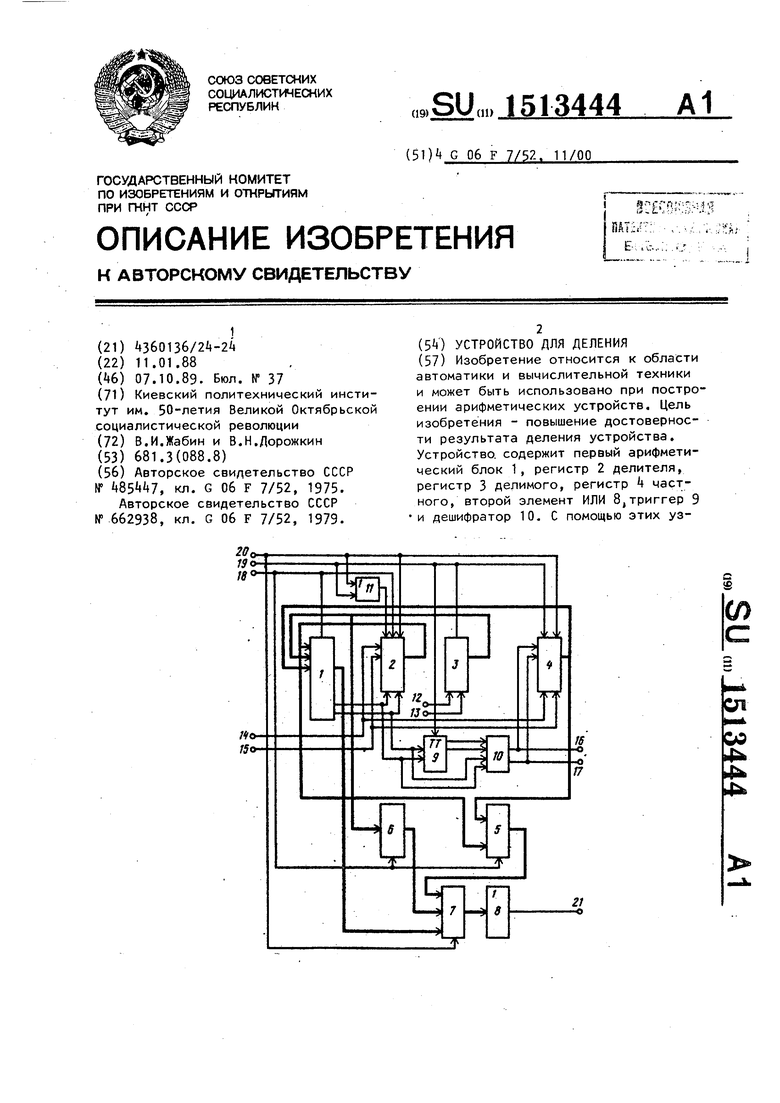

На чертеже проведена функциональная схема устройства для деления.

Устройство для деления содержит первый арифметический блок 1, регистр 2 делителя, регистр 3 делимого, ре- гистр k частного, второй и третий арифметические блоки 5 и 6, сумматор 7, второй элемент ИЛИ 8, триггер 9, дешифратор 10, первый элемент ИЛИ 11, входы 12 и 13 первого и второго раз-; рядов делимого устройства, входы 14 и 15 первого и второго разрядов делителя устройства, информационные вы- 35 ходы 1б и 17 первого и второго разрядов устройства, тактовые входы 18- 20 устройства, выход 21 неисправности устройства.

Арифметические блоки 1, 5 и 6 име- 40 ют цепь сдвига содержимого на два разряда влево и являются накапливающими сумматорами. Регистры 2-4, имеют цепи выдачи прямого и дополнительного кодов. Регистры 2 и 4, кроме . 45 того, имеют цепи приёма кода. Младшие разряды регистров 2 и А являются суммирующими, а остальные разряды этих регистров имеют цепь распространения переноса. Комбинационный сум- 50 матор 7 является трехвходовым, причем один вход является инверсным и перенос в младший разряд для этого входа равен единице.

Дешифратор 10 может быть построен 55 в соответствии с системой переключательных функций вида

p-q,

f 1

Р-Ч

где fj - функции i-ro выхода (i 1,

2) дешифратора 10j р - значение старшего разряда

сумматора 1;

q - значение состояния триггера 5.

Исходные операнды А и В и результат X представлены двоичным избыточным кодом с цифрами -1, О, 1.

Каждый разряд числа кодируется двумя цифрами. При этом цифре 1 соответствует сигнал на входе 12 или k устройства и на выходе 1б устройства. Цифре 1 соответствует сигнал на входе 13 или 15 и на выходе 17 устройства. Цифре О соответствует отсутствие сигналов на входах 12 и 13, на входах 1 и 15, или на выходах 16 и Т7 устройства.

В каждый момент времени на входы 12-15 устройства поступают разряды делимого А и делителя В с одинаковыми весами. На величины А и В накладываются следующие ограничения:

О А 1/2, 1/2 :в ; 1 ,

Контроль функционирования устройства осуществляется в каждом цикле и использует следующие соотношения;

2 (2- А/ Z .-В ;) - R: 0.

В арифметическом блоке 5 накапливается величина Z;-B,, а в арифметическом блоке 6 величина д,. Число разрядов k для контролирующих блоков определяется числом тактов функционирования устройства, в которых обнаруживается сбой устройства деления. Отказ одного или нескольких элементов устройстгза деления обнаруживается при k 7/ 3.

Устройство для деления работает следующим образом.

515

в исходном состоянии в младшем разряде регистра 3 записана единица, а все остальные регистры и арифметические блоки,триггер 9 установлены в нулевое состояние. В каждом цикле вычислений на тактовые входы 18-20 устройства поочередно поступают соответственно тактирующие сигналы Т,, Т, Tj. К началу каждого i-ro цикла вычислений (i 1, 2, ..., П-3) на входы 12 и 13 делимого и 1 и 15 делителя устройства поступают цифры очередных разрядов соответственно а, bj. В первом такте i-ro цикла сигнал Т, с входа 18 устройства поступает на входы сдвига блоков 1, 5 и 6 и на вход записи регистра 2. В результате этого содержимое блоков 1, 5 и 6 сдвигается на два разряда влево, а к младшему разряду-регистра 2 прибавляется значение очередного разряда bj. Если Ь; -1, то вычитается единица из младшего разряда регистра 2. Если 1, то прибавляется единица к младшему разряду регистра 2, а если Ъ. 0, то регистр ,2 не изменяет своего состояния. Таким образом в регистре 2 происходит накопление делителя В.

Во втором такте i-ro цикла сигнал Т с входа 19 устройства поступает на тактовый вход триггера 9, через элемент ИЛИ 11 поступает на вход считывания регистра 2 и на входы считывания и сдвига регистров 3 и . В результате этого в блоке 1 происходит суммирование содержимого этого блока с кодами, поступающими с выходов регистров в блоке 5 происходит суммирование содержимого этого блока с кодами, поступающими с выходов регистров 2 и 4, в блоке 6 происходит суммирование содержимого этого блока с кодами, поступающими с выходов регистра 3. В триггер 9 записывается предыдущее состояние старшего разряда блока 1 (так как каждый разряд блоков 1, 5 и 6 построен на триг- Герах с внутренней задержкой). Если в старшем (знаковом) разряде блока 1 записан нуль, то из регистра 2 в бло- кх 1 и 5 выдается дополнительный код, а если в этом разряде записана единица-, то из регистра 2 в блоки 1 и 5 передается прямой код. Код на выходе регистра 3 зависит от сигналов-на входах 12 и 13 устройства. Если есть сигнал на входе 12 устройства (з;

-1), и то из регистра 3 выдается дополнительный код, а если присут- ствует сигнал на входе 13 устройства (а- 1), то выдается прямой код. При отсутствии сигналов на входах 12 и 13 устройства код из регистра 3 не выдается. Код на выходе регистра зависит от значений сигналов на входах

0 l и 15 устройства. Если есть сигнал на. входе 1 устройства (Ь . -1), то из регистра k выдается прямой код, а.если присутствует сигнал на входе 15 устройства (Ь; 1), выдается до5 полмительный код. При отсутствии сигналов на входах I и 15 устройства код из регистра не выдается.

Одновременно с этим содержимое регистров 3 и 4 сдвигается на один

0 разряд влево (так как каждый разряд этих регистров построен на триггерах с внутренней задержкой). При выдаче дополнительного кода из регистров 2- на входы свободных (не связанных

5 с выходами регистров 2, 3 и +) разрядов блоков 1, 5 и 6 подаются единичные сигналы и, кроме того, на вход младшего разряда подается еще один единичный сигнал.

0 Перед началом третьего такта i-ro цикла вычислений дешифратор 10 ана- лизирует состояние триггера 9 и старшего разряда блока 1 и на выходах дешифратора 10 появляется код-очередного разряда частного X., который

поступает на выходы 1б и 17 устройства. В третьем такте цикла деления сигнал Тз с входа 20 устройства поступает на вход записи регистра А, на вход сдвига регистра 2, и через элемент ИЛИ 11 - на вход считывания регистра 2. В результате этого из регистра 2 в соответствии со значением старшего (знакового) разряда сумма- тора 1 в блоки 1 и 5 выдается прямой или дополнительный код, а к младшему разряду регистра А прибавляется значение очередного разряда X;.

При этом, если присутствует сиг-. нал на выходе 1б устройства (Х - -1), то вычитается единица из младшего разряда регистра 4. Если присутствует сигнал на выходе 17 устройства, то прибавляется единица в младший разряд регистра k, а если

сигналы на выходах.отсутствуют, то регистр k не изменяет своего состояния. Таким образом в регистре происходит накопление частного X. Одло0

115

временно с этим содержимое регистра 2 сдвигается на один разряд влево. В третьем такте К-разрядные коды, поступающие с блоков 1, 5 и 6, суммируются в комбинационном К-разрядном сумматоре 7. Выход этого сумматора поступает на вход элемента ИЛИ 8. В случае сбоя или отказа любого элемента схемы на выходе элемента ИЛИ 8 в третьем такте появится сигнал 1. Таким образом осуществляется полный контроль устройства деления.

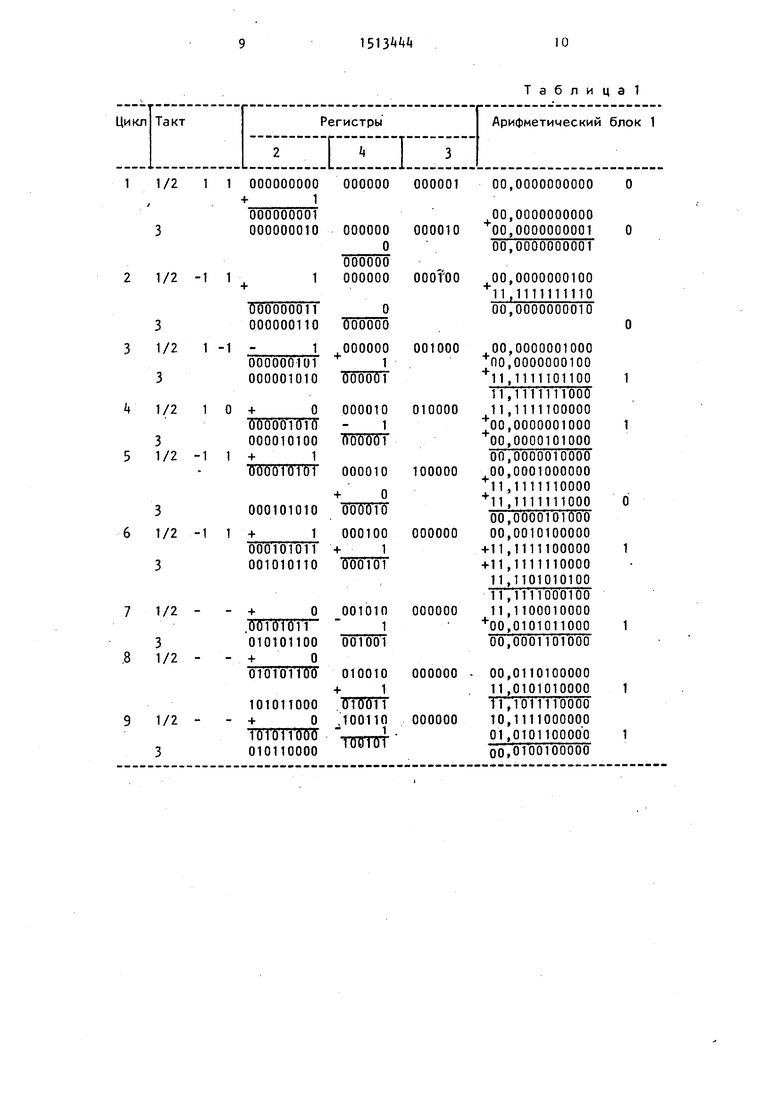

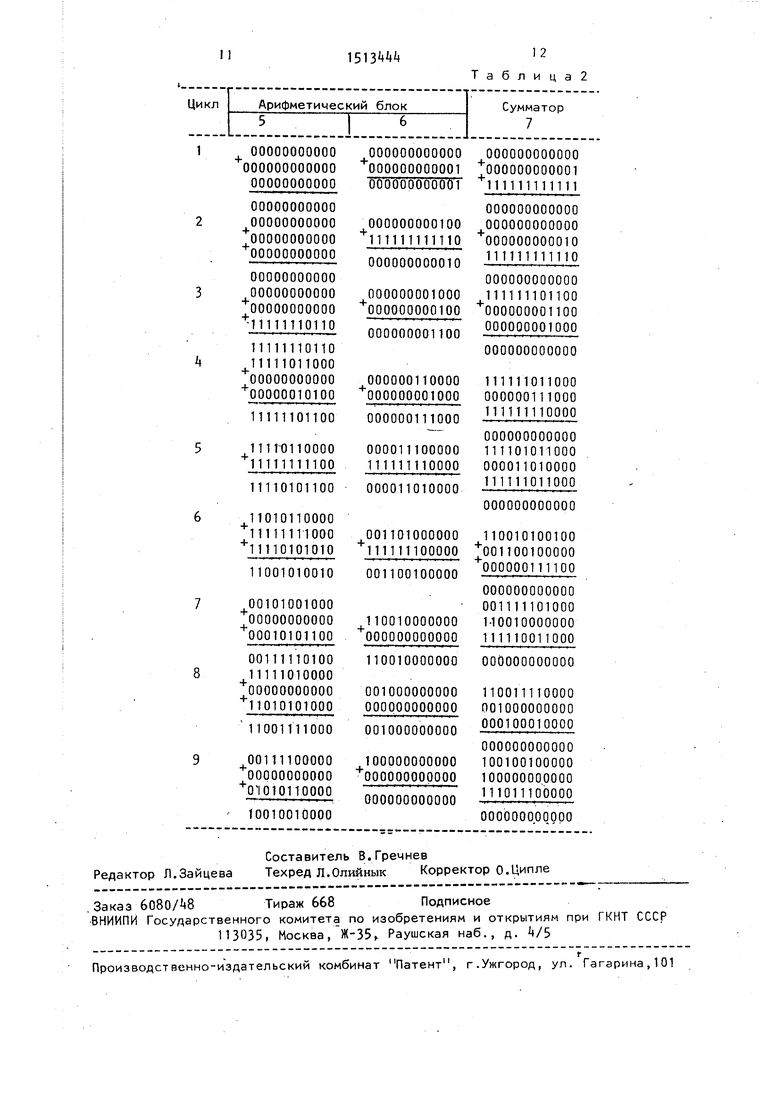

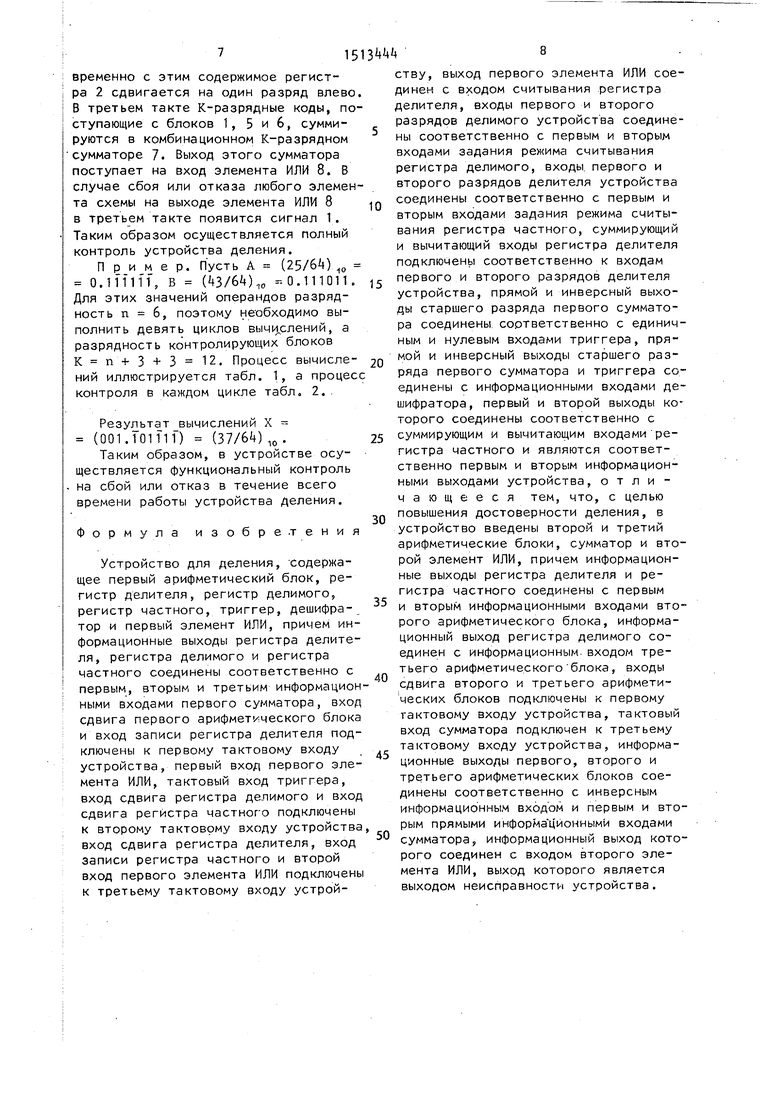

Пример. Пусть А (25/6)о 0. iff iff, В ( +3/6),о -0,111011. Для этих значений операндов разрядность п 6, поэтому необходимо выполнить девять циклов вычи,слеиий, а разрядность контролирующих блоков К п+3+3 12. Процесс вычислений иллюстрируется табл. 1, а процесс контроля в каждом цикле табл. 2..

Результат вычислений X (001.1 01 f If) (37/64),.

Таким образом, в устройстве осуществляется функциональный контроль на сбой или отказ в течение всего времени работы устройства деления.

Формула изобретения

Устройство для деления, Содержащее первый арифметический блок, регистр делителя, регистр делимого, регистр частного, триггер, дешифра-, тор и первый элемент ИЛИ, причем информационные выходы регистра делителя, регистра делимого и регистра частного соединены соответственно с первым, вторым и третьим информационными входами первого сумматора, вход сдвига первого арифмет /ческого блока и вход записи регистра делителя подключены к первому тактовому входу устройства, первый вход первого элемента ИЛИ, тактовый вход триггера, вход сдвига регистра делимого и вход сдвига регистра частного подключены к второму тактовому входу устройства вход сдвига регистра делителя, вход записи регистра частного и второй вход первого элемента ИЛИ подключены к третьему тактовому входу устрой31+/4 48

ству, выход первого элемента ИЛИ соединен с входом считывания регистра делителя, входы первого и второго разрядов делимого устройства соедине- ны соответственно с первым и вторым входами задания режима считывания регистра делимого, входы, первого и второго разрядов делителя устройства соединены соответственно с первым и вторым входами задания режима считывания регистра частного, суммирующий и вычитающий входы регистра делителя подключень соответственно к входам

10

первого и второго разрядов делителя

устройства, прямой и инверсный выходы старшего разряда первого сумматора соединены соответственно с единичным и нулевым входами триггера, прямой и инверсный выходы старшего разряда первого сумматора и триггера соединены с информационными входами дешифратора, первый и второй выходы которого соединены соответственно с

суммирующим и вычитающим входами регистра частного и являются соответственно первым и вторым информационными выходами устройства, отличающееся тем, что, с целью

повышения достоверности деления, в устройство введены второй и третий арифметические блоки, сумматор и второй элемент ИЛИ, причем информационные выходы регистра делителя и регистра частного соединены с первым

и вторым информационными входами вто0

5

рого арифметического блока, информационный выход регистра делимого соединен с информационным.входом третьего арифметического блока, входы сдвига второго и третьего арифметических блоков подключены к первому тактовому входу устройства, тактовый вход сумматора подключен к третьему тактовому входу устройства, информационные выходы первого, второго и третьего арифметических блоков соединены соответственно с инверсным информационным входом и первым и вторым прямыми информа цйоннымй входами сумматора, информационный выход которого соединен с входом второго элемента ИЛИ, выход которого является выходом неисправности устройства.

II

isn t

12 Таблица2

| Авторское свидетельство СССР ff , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1976 |

|

SU662938A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1988-01-11—Подача