о

Ј

сл

Ј О 00

Изобретение относится к автоматике и вычислительной технике и может быть использовано для спектрального . анализа случайных процессов, циЛро- « вой фильтрации, сжатия сигнала

1645968а

Цель изобретения - упрощение устройства.

Алгоритм вычисления коэффициентов в базисе Фурье для может быть представлен в следующем виде: 1-й шаг

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов Фурье | 1983 |

|

SU1096655A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1647592A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для преобразования по функциям Хаара | 1986 |

|

SU1327119A1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1545230A1 |

| Устройство для выполнения быстрого преобразования Уолша | 1987 |

|

SU1425707A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| Устройство для быстрого преобразования Уолша в реальном масштабе времени | 1988 |

|

SU1709341A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для спектрального анализа случайных сигналов, цифровой Фильтрации, сжатия сигналов. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что в состав устройства входят умножители 1, регистры 2, сумматоры-вычитатели 3, регистры 4, блоки 5 постоянной памяти коэффициентов и блок 6 синхронизации. 3 ил., 1 табл.

x,xlx3x4 -(x,wl +xawZ4)( (..Уэ.-Д.)

Ј- - п

х:

х;

2-й шаг

хХ +xiw,2), (, (), (,) .

Ј c ; c3c+

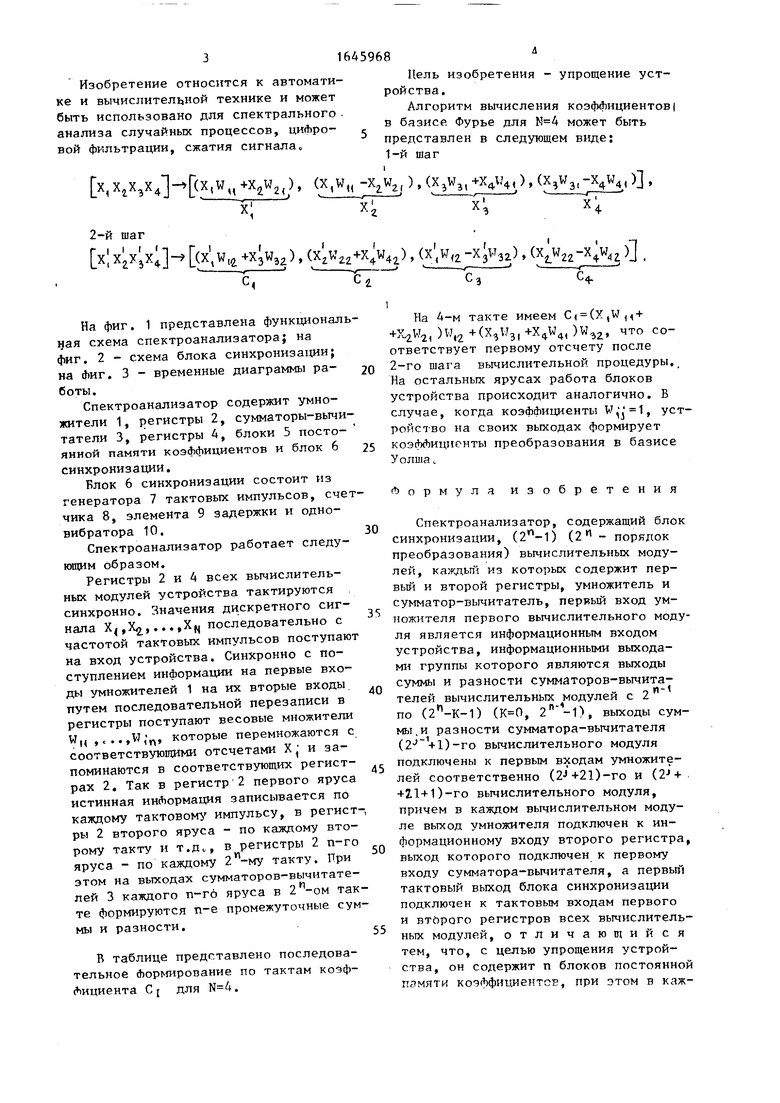

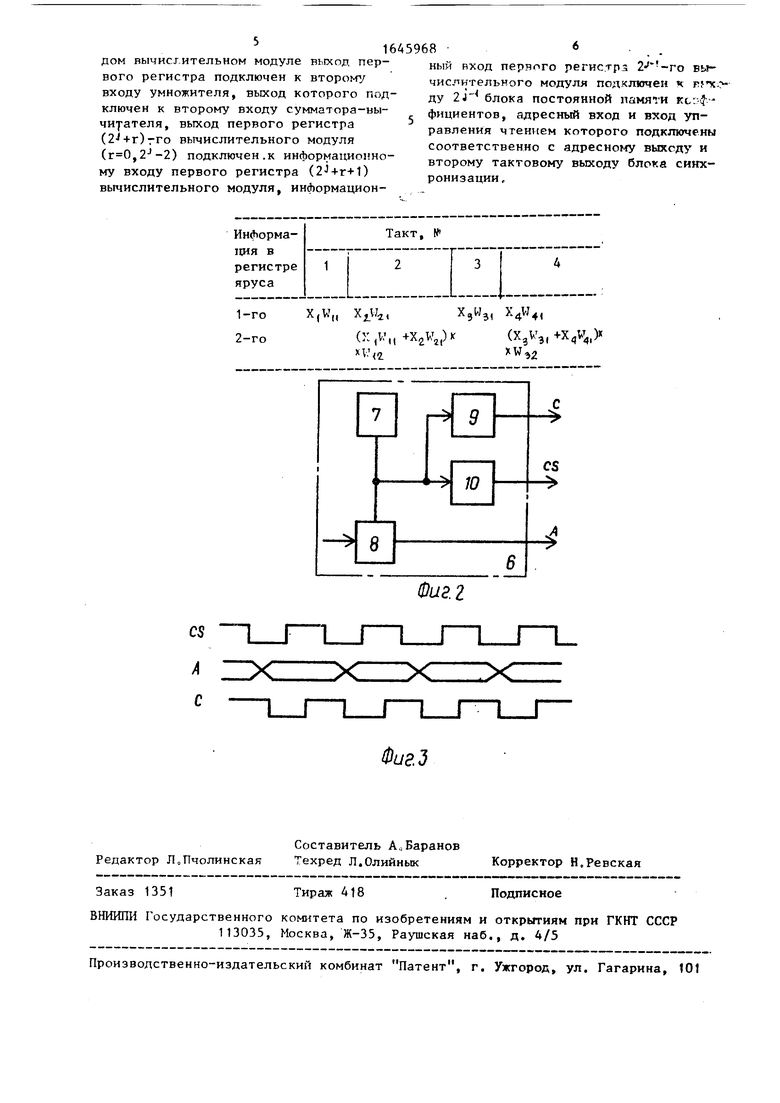

На фиг. 1 представлена функциональная схема спектроаналиэатора; на фиг. 2 - схема блока синхронизации; на Фиг. 3 - временные диаграммы работы.

Спектроанализатор содержит умножители 1, регистры 2, сумматоры-вычи- татели 3, регистры 4, блоки 5 постоянной памяти коэффициентов и блок 6

синхронизации.

Блок 6 синхронизации состоит из генератора 7 тактовых импульсов, счетчика 8, элемента 9 задержки и одно- вибратора 10.

Спектроанализатор работает следующим образом.

Регистры 2 и 4 всех вычислительных модулей устройства тактируются синхронно. Значения дискретного сигнала Х| ,Х,... ,Xjj последовательно с частотой тактовых импульсов поступают на вход устройства. Синхронно с поступлением информации на первые входы умножителей 1 на их вторые входы путем последовательной перезаписи в регистры поступают весовые множители W,, ,«..,W;n, которые перемножаются с соответствующими отсчетами Xt и запоминаются в соответствующих регистрах 2. Так в регистр 2 первого яруса истинная информация записывается по каждому тактовому импульсу, в регист ры 2 второго яруса - по каждому второму такту и т.дь, в регистры 2 п-го яруса - по каждому 2п-му такту. При этом на выходах сумматоров-вычитате- лей 3 каждого п-го яруса в 2п-ом такте формируются n-е промежуточные суммы и разности.

В таблице представлено последовательное Формирование по тактам коэффициента Ct для .

п

х:

х;

0

5

30

3S

, 40

45

50

i

На 4-м такте имеем C (X,W, +

, )WI2 +(X,W3, +X4W4, )WM, что соответствует первому отсчету после 2-го шага вычислительной процедуры. На остальных ярусах работа блоков устройства происходит аналогично. В случае, когда коэффициенты W,., устройство на своих выходах формирует коэффициенты преобразования в базисе Уолшаt

Формула изобретения

Спектроанализатор, содержащий блок синхронизации, (2п-1) (2м - порядок преобразования) вычислительных модулей, каждый из которых содержит первый и второй регистры, умножитель и сумматор-вычитателъ, первый вход умножителя первого вычислительного модуля является информационным входом устройства, информационными выходами группы которого являются выходы суммы и разности сумматоров-вычита- телей вычислительных модулей с 2 по (2п-К-1) (, 2п 1-1), выходы суммы.и разности сумматора-вычитателя ()-ro вычислительного модуля подключены к первым входам умножителей соответственно ()-го и (2J + +2.1+1)-го вычислительного модуля, причем в каждом вычислительном модуле выход умножителя подключен к информационному входу второго регистра, выход которого подключен к первому входу сумматора-вычитателя, а первый тактовый выход блока синхронизации подключен к тактовым входам первого и второго регистров всех вычислительных модулей, отличающийся тем, что, с целью упрощения устройства, он содержит п блоков постоянной памяти коэффициентов, при этом в каждом вычислительном модуле выход первого регистра подключен к второму входу умножителя, выход которого подключен к второму входу сумматора-вы- читателя, выход первого регистра ()-го вычислительного модуля (,2J-2) подключен.к информационному входу первого регистра (2J+r+1) вычислительного модуля, информацион1-го2-го

X,WM

ный вход первого регистрз вычислительного модуля подключен ч ду 2J блока постоянной памяти кс: t фнциентов, адресный вход и вход управления чтением которого подключены соответственно с адресному выходу и второму тактовому выходу блока синхронизации.

X9W3,

+X2W2()K

X4W4,

(X3V3I XW,2

Фиг. 2

Фиг.3

| Устройство ортогонального преобразования по уолшу | 1976 |

|

SU620974A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США V 3981443, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-30—Публикация

1989-04-12—Подача