Изобретение относится к вычисли- , тельной технике и может быть использовано в высокопроизводительных устройствах обработки цифровой информации.

Целью изобретения является расширение области применения за счет осуществления суммирования чисел с разными знаками.

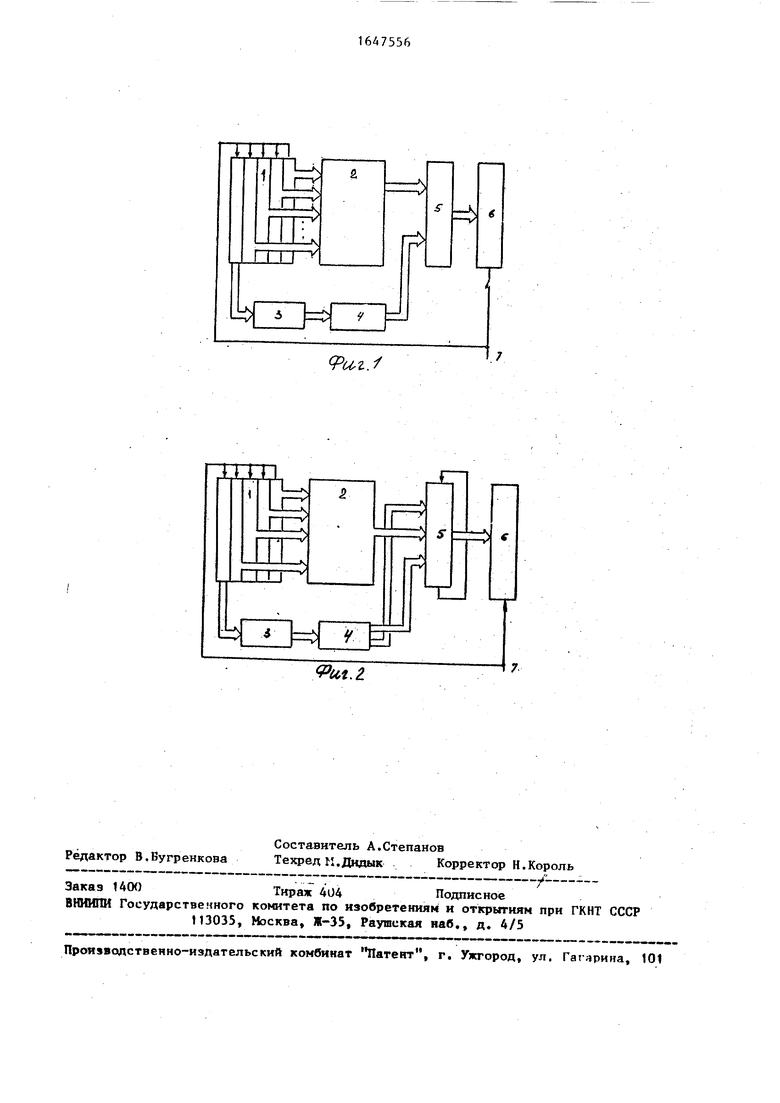

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - вариант построения структурной схемы устройства для суммирования массива чисел в обратном коде.

Устройство для суммирования массива чисел содержит запоминающий блок 1, сумматор 2 для группового сложения чисел, одноразрядный многовходовый сумматор 3, постоянный запоминающий блок 4, параллельный сумматор 5, выходной регистр 6 и вход 7 синхронизации. Запоминающий блок 1 представляет собой группу из N n-разрядных регистров или ячеек памяти с возможностью одновременного обращения ко всем регистрам (ячейкам) одновременно и может быть выполнен и в виде ассоциативного запоминающего устройства. Сумматор 3 предназначен для определения количества единиц в знаковом срезе слагаемых.

Устройство осуществляет суммирование N n-разрядных двоичных чисел, представленных в виде (п-1)-разряд-.

4 СЛ СП

Ф

ной мантиссы и одного знакового раз- ряда.

В основе работы устройства лежит следующий метод.5

Пусть слагаемые массива представлены в виде:

п- п-4 о Ч„-К +q ,;, К +...+q,n.K ;

q(-KMH +qz....+q n K°; 10 qN/Kh +qNi- Kh 1 + -.+qNn-K0 ,

где К - основание системы счисления; q -t - коэффициент, принимающий со- ответствующее значение при 15 представлении чисел в системе счисления с основанием К. Для двоичной системы , Представим тот же массив слагаемых в двоичной системе разрядности резуль-20 тата, т.е. разрядности n+Jlog Nf, причем знаковый разряд переносим в самую левую позицию, тогда:

q Mleog C-i гн1 гМГ-г 25

1 i

2 5 п г q2, 2nVo9 NC- +qn. +

: $ щг№ + .iuJtffcit-V

qN, +qNZ

+ -- +ЗДбо мС 2°

Поскольку разрядность исходных слагаемых п, то все отрицательные чис ла при представлении их в обратном или дополнительном кодах разрядности n+ logtNLB позициях, начиная с 2П по 2n4e° N z ) будут иметь единицы, которые назовем фиктивными, так как они отсутствуют в исходных кодах слагаемых. Пусть отрицательных чисел и массиве будет К. Тогда для получения правильного результата сложения разиознаковых чисел необходимо к сум- ме мантисс

, ql2 2n 2+q V2n 3+...+qftl-2° ;

, 2n-4 l2J.2t1- + ... Ul

«

Ям2-2 г-Н1й} 2И Э + ...-К1Мп-2висходного массива прибавить число

(2ги|ео си fa.«c-

к J

знаковый разряд ).

При получении суммы массива разно- знаковых слагаемых очевидно следует учитывать форму представления слагаемых .

Так, если слагаемые представлены в дополнительном коде, все единицы переноса, превышающие разрядность n+Jlog NL, игнорируются.

Если числа представлены в обратном коде, все единицы переноса, превышающие разрядность n+Jlog NЈ, циклически в соответствии со своими позициями складываются с младшими разрядами полученной суммы.

Преобразуя значение Рк, можно получить в следующем виде

P,.K.(23e CrtJfc :...rt0)

при этом К пробегает в общем случае значения от 1 до N. Поскольку любое число Р кратно 2 , для получения окончательной суммы необходимо знать

числа

fcjfcNC-i о (2 +2 3 +...+2 ),

которые можно хранить в памяти. При этом для считывания из памяти нужного числа необходимо знать число единиц в знаковом срезе (т.е. число отрицательных слагаемых), которое является адресом числа Р„.

Для получения окончательной суммы необходимо суммировать сумму мантисс исходных слагаемых с числом Рк, сдвинутым относительно этой суммы на п-1 разряд влево.

Устройство работает следующим обг разом.

Разрядные срезы слагаемых юступают на соответствующие входы сумматора 2, а разрядный срез знакового разряда - на вход сумматора 3, формирующего код количества единиц в этом срезе, т.е. количество отрицательных чисел в массиве. Данный код является (2-3log2Nf) разрядным, при этом если слагаемые представлены в дополнительном Коде, то в разрядах постоянного запоминающего блока 4 Glog2NL+1)-ro по (2«3log.,N)-u содержатся нули, т.е. эти разряды не используются. При суммировании чисел в обратном коде параллельный сумматор 5 должен содержать цепь циклического переноса (фиг.2), Результат суммирования заносится в регистр 6 по заднему фронту импульса синхронизации по входу 7.

Рассмотрим для примера суммирование чисел в дополнительном коде. Сумма мантисс определяется следукмцим образом +5

+6

+ 7 -S

-з

-1

Так как разрядность результата равна семи, то на выходе сумматора 2 получают число 0.100001 . Так как в массиве содержится три отрицательных числа, то на выходе сумматора 3 будет сформирован код 011, т.е. 3 в двоичном коде. Этот код является адресом для считывания Р3, которое является суммой фиктивных единиц и знаков из блока 1, т.е. будет считано число . Оконча- (Тельно сумма массива определится как; 0.100001

1.101

.0.001001

+9

единица переполнения игнорируемся. Формула изобретения

Устройство для суммирования массива «исел, содержащее запоминающий блок, сумматор для группового сложен ния чисел и выходной регистр, причем выходы групп одноименных разрядов слагаемых запоминающего блока соеди

;

6

пены с соответстн тогф ми входами сумматора для группового сложения чисел, отличающееся тем, что, с целью расширения области применения за счет осуществления суммирования чисел с разными знаками, устройство дополнительно содержит одноразрядный многовходовый сумматор, постоJQ янный запоминакиций блок и параллельный сумматор, причем выходы знаковых разрядов слагаемых запоминающего блока соединены с входами одноразрядного многовходового сумматора, выход кото-15 росо соединен с адресным входом постоянного запоминающего блока, разряды выхода сумматора для группового сложения чисел соединены с соответствующими разрядами первого входа парал20 лельного сумматора,разряды второго входа которого с первого по Jlog2N -ft соединены с разрядами выхода постоянного запоминающего блока с фо§гн -Н)-го по (2-11ор,гн)-й, а

25 разряды с n-го по (n+ logll$ - )-Pi соединены с разрядами выхода постоянного запоминающего блока соответственно с первого по JlogjN -ft, пде N - число слагаемых, an- разряд30 ность слагаемых, выход параллельного сумматора соединен с информационным входом выходного регистра, выход которого является выходом результата устройства, вход синхронизации запо,. минающего блока соединен с входом синхронизации выходного регистра и подключен к входу синхронизации устройства, свободные разряды входов параллельного сумматора соединены с шиной нулевого потенциала устройства.

ГХ

S

Ј

-ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| Многовходовой сумматор | 1989 |

|

SU1679483A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Устройство для сложения последовательности чисел с плавающей запятой | 1984 |

|

SU1182512A1 |

| Преобразователь двоичного кода вдОпОлНиТЕльНый | 1979 |

|

SU851395A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных устройствах обработки цифровой информации. Целью изобретения является расширение области применения за счет осуществления суммирования чисел с разными знаками . Цель достигается тем, что в устройство, содержащее запоминающий блок, сумматор для группового сложения чисел и выходной регистр, введены одноразрядный многовходовый сумматор, постоянный запоминающий блок и параллельный сумматор, а также новые связи. Устройство может суммировать числа в дополнительном и обратном коде. Суммирование чисел с различными знаками осуществляется путем добавления корректирующего кода, считанного из постоянного запоминающего блока по адресу, являющемуся кодом числа отрицательных чисел, к сумме мантисс чисел. 2 ил. (Л

./

&.Ј

| Конвейерное вычислительное устройство | 1985 |

|

SU1322261A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Введение в кибернетическую технику | |||

| /Под ред | |||

| Б.Н.Малиновского | |||

| - Киев, Наукова Думка, 1979, с | |||

| Способ получения морфия из опия | 1922 |

|

SU127A1 |

| Пишущая машина | 1922 |

|

SU37A1 |

Авторы

Даты

1991-05-07—Публикация

1989-01-13—Подача