рядов второго регистра порядка и инверсные выходы первого регистра поря ка, выход первого сумматора соединен с первым информационным входом перво го коммутатора и с первым входом второго сумматора, второй вход которого соединен с входом кода (б) где Р у (Е) - минимальный порядок числа, второй информадионньш и управляюпщй входы первого коммутатора соединены сооч ветственно с вькодом третьего регистра порядка и прямым выходом триггера управления, выход первого коммутатора соединен с адрес ным входом второго узла памяти, первый выход которого соединен с первым входом первого элемента И, второй вход которого соединен с инверсным выходом триггера управления, выход, первого элемента Н подключен к перво му управляющему входу второго коммутатора, второй управляющий вход кото рого соединен с выходом второго разряда регистра управления, выход второго коммутатора подключен к тактово му ,чу первого регистра порядка, выход регистра мантиссы соединен с информационным входом- сдвигателя, выход которого соединен с первьп-ш входами элемектов И группы, управляю щий вх. сдвигателя соединен с выходa яI log, L F rood (n - 1)) младших разрядов второго регистра порядков; первьш, второй и третий выходы перво го узла памяти соединены соответственно с упрггвлягощим входом третьего ком№/татора, первым и вторым управляю1 1, входами четвертого коммутатора четвертый выход первого узла naixiHTH соединен с информационным входом триггера управления первым входом второго элемента И и с вторыми входами элементов И группы,, первый и второй инфррмационные входы 4ретьего комГ утатора соединены соответственно с выходом второго суьматора и входом Р j,, (Б) устройства, выход первого элемента Н соединен с тактовыми входами второго регистра порядка и регистра мантиссы, выход второго узла пашти соединек с информадаонпым входом третьего ре-гистра порядка, первый и второй ин формациониые:входы четвертого коммутатора соединены соответственно с входами кодов 100 и 000 устройствЛ(, разряд третьего инфор мациойного входа четвертого KOMJxryтатора соединен с. входом логического 1 2 нуля устройства, второй и третий разряды третьего информационного входа соединены соответственно с двумя младшими выходами второго узла памяти, тактовые входы триггера управления, регистра управления и третьего регистра порядка соединены с инфор,мационным входом второго коммутатора и вторым входом второго элемента И, информационные входы регистра управления, второго регистра порядка, регистра мантиссы, триггера управления и второго коммутатора блока управления соединены соответственно с входами управления, порядка, мантиссы, готовности и тактовым входом устройства, причем ка;ж,дый .блок сум1 1ирования содержит регистр кода операции, четвертую и пятую группы элементов И, группу элементов ИЛИ, элемент НЕ, элемент И, причем выход первого разряда регистра кода операции соединен с первым входом элемента И, второй вход которого соединен с выходом элемента ИЛИ, выход элемента И соединен с вторым входом сумматора порядка, с первыми входа1-1и алементоз И четвертой группы и через элемент НЕ с вторыми.входами элементов И второй и третьей групп, выходы регистра мантиссы соединены с вторыми входа- . ми .соответствующих элементов И четвертой группы выходы элементов И первой группысоединены с соответствую1дими входами второй группы сумматора мантисс, вход переноса которого соединен с выходом триггера переноса, выходы второго и третьего разрядов регистра кода операции соединены соответственно с первыми входами Т), старших и i-n младших элементов И пятой группы, вторые входы которых соединены с соответствующими выходами регистра младшего разр 1,/р, выходы элементов И четвертой и пятой групп соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ группы, третьи входы Р старших.из которых соединены с выходами старшего элемента И третьей группы, выходы младших элементов И которой соединены с третьими; входами соответствующих младших элементов ИЛИ группы, тактовый вход регистра кода операции соединен с тактовым входом регистра порядка,, выход регистра кода операцйи и выходы элементов ИЛИ группы, выход переноса сумматора мантисс yfc-ro блока суммирования соединены соответственно с информационными входа регистра кода операции и ре гистра мантисс, информационным входом триггера переноса (k+ 1)-го 2 блока суммирования, выходы третьего и четвертого коммутаторов и выход группы элементов И блока управления соединены соответственно с информационными входами регистра порядка, регистра кода операции и регистра мантиссы первого блока суммирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Устройство для сложения 2 @ чисел | 1985 |

|

SU1307456A1 |

УСТРОЙСТВО ДЛЯ СЛОЖНИЯ ПОСЛЕДОВАТЕЛЬНОСТИ ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ, содержащее m блоков суммирования, каждьй из которых содержит регистры порядка и мантиссы, триггер переноса, сумматоры порядка и мантиссы, элемент ИЛИ, регистр младшего разряда и три группы элементов И, причем в каждом блоке сум.мирования вьрсоды регистра порядка соединены с входами первой группы сумматора порядка и с сответствующими входами элемента ИЛИ, выходы регистра младшего разряда соединены с первыми входами элементов И первой группы, выходы младших и старших разрядов регистра мантисс соединены соответственно с первыми входами элементов И второй и третьей групп, выходы элементов И второй группы соединены с соответствующими входами первой группы сумматора мантисс, выход суммы сумматора мантисс соединен с информационным входом регистра младшего разряда, тактовьш вход которого соединен с тактовыми входами регистров мантиссы и порядка, тактовым входом триггера переноса и тактовым входом устройства, выход регистра порядка k -го блока суммирования соединен с информационным входом регистра порядка (k + 1)-го блока суммирования, выход fn-го блока суммирования является выходом устройства ( k 1 - (iTi- 1)), отличающееся тем, что, с целью сокращения аппараттурных затрат, оно содержит блок управления, содержащий регистр управления, первый, второй, третий регистры порядка, первый, второй элементы И, триггер управления, регистр мантиссы, схему сравнения, первый , второй сумматоры, первый, УЗ второй узлы памяти, сдвигатель, группу элементов И, первый, второй, третий и четвертый коммутаторы, .причем выходы первого регистра порядка, за исключением выхода знакового разряда, а также выходы разрядов второго регистра порядка, с втоРОГО по (lOQ,(y - 1)J + 1)-й, где Р;ис1кс максимальный порядок числа, п-разрядность мантиссы,соединены соответственно с первой и второй группами входов схемы сравнения, выходы регистра управления, выходы знаковых разрядов первого и второго регистров порядка, выходы схемы сравнения, соединены соответственно с адресньми входами первого узла памяти, выходы (log2LP(,,,c/(n - 1)J + 1) стар-ших разрядов второго регистра порядка соединены соответственно с информационными входами первого регистра порядка, к первой и второй группам входов:первогосумматора подключены соответственно прямые выходы (logj L 1-i О старших раз

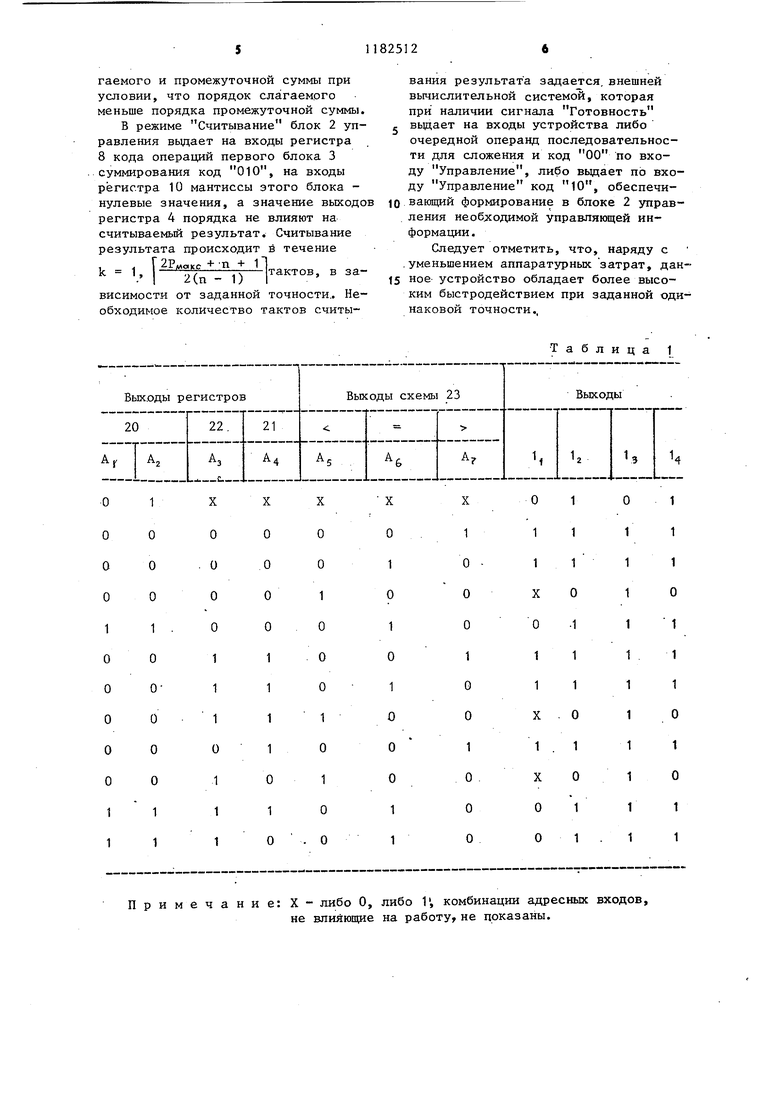

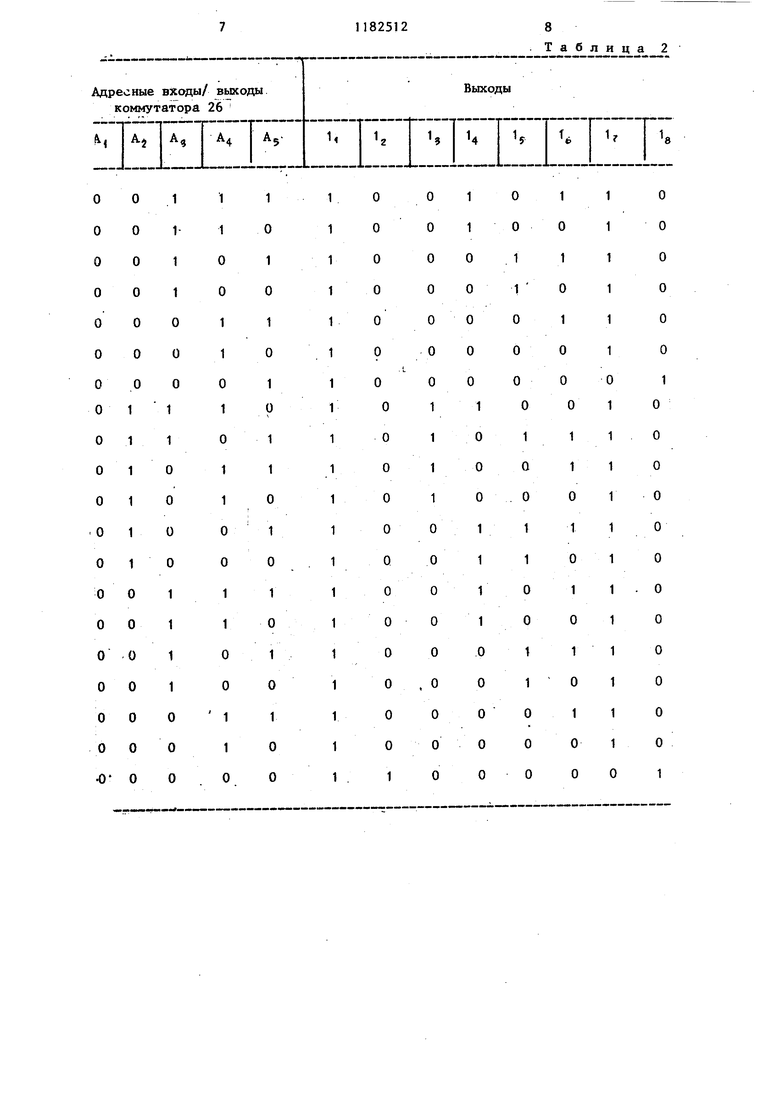

Изобретение относится к вычислительной технике и может быть исполь зовано при построении специализированных вьтислительных систем в качестве высокопроизводительного блока, обеспечивающего заданную точность сложения последовательности чисел с плавающей запятой. Целью изобретения является сокра щение аппаратурных затрат. На чертеже представлена схема устройства для сложения последовательности чисел с плавающей запятой Устройство содержит тактовьш вхо 1,, блок 2 управления, блоки 3 сумми рования. Блок 3 суммирования содержит регистр 4 порядка, элемент ИЛИ 5, сум матор 6 порядка, элемент И 7, регис 8 кода операции, группу 9 элементов И, регистр 10 мантиссы, группы 11 и 12 элементов И, элемент НЕ 13, груп пу 14 элементов И, регистр 15 младшего разряда, группу 16 элементов И, сумматор 17 мантисс, триггер 18 переноса, группу 19 элементов ИЛИ. Блок 2 управления содержит регистр 20 управления, регистры 21 и 22 порядка, схему 23 сравнения, узе 24 памяти, сумматор 25, коммутатор 26, сумматор 27, регистр 28 порядка триггер 29 управления, узел 30 памя ти, элемент И 31, коммутатор 32, ре гистр 33 мантиссы, сдвигатель 34, группу 35 элементов И, элемент И 36 коммутаторы 37 и 38. Устройство для сложения последовательности чисел с плавающей запятой работает в режимах Начальная установка, Сложение, Сдвиг и Считывание. Узел 24 памяти блока 2 управлени имеет кодировку, представленную в табл. 1. Узел 30 памяти блока 2 управления имеет установку, представленную в табл. 2. Работа блока 2 управления по вьщаче необходимой информации на входы первого блока 3 суммирования осуществляется в соответствии со следующим алгоритмом. Шаг 1 (начальная установка). Выполнить Р(е) 1 РХ/.(П - 1)J, М () М,(Ч Р(е) P,.mod(n - 1), установить начальное значение первого регистра порядка Рд,ц() Ру(). Одновременно вьдать: на ВХОДЫ регистра мантиссы число М, (б)) pit Х2 , на входы регистра кода операции блока 3 код 000, выставить сигнал Готовность. Шаг 2 (прием очередного операнда, или такты считывания результата): Py(f) Pxmod(n - 1), Мх(е) (f; - . РХ() LPji(n - 1)J. Шаг 3. Если Р(е) Рмин(б о одновременно вьщать на входы . регистра порядка число Р(S)-. - ) 1мич ЕЬ «а sx°ды регистра кода операций код 100, на входы регистра . мантиссы - мантиссу, установить сигнал Готовность и перейти к шагу 2, иначе к шагу 4. Шаг 4, Вьшолнить: ЛР /Рмин - Р, ()1 и Pjij (е) Р(е). Шаг 5. Если Рд 1, то вцдать на , входы регистра кода операций код 001, на входы регистра мантиссы мантиссу 00.0, Если Л 2, то ввдать на входы регистра кода операций код 010, на входы регистра мантиссы-мантиссу 00...О и перейти к шагу 7, иначе перейти к шагу 6.

Шаг 6. Одновременно вьщать: на входы регистра кода операций код, 010, на входы регистра мантиссы - мантиссу 00...О, выполнить ДР &Р - 2 и перейти к шагу 5.

Шаг 7, Одновременно вьщат-ь; на входы регистра кода операций код 100, на входы регистра порядка - порядок ., (б) г. на входы регистра мантиссы мантиссу М(е) 2( , уста новить сигнал Готовность и перейти к шагу 2.

Примечание: - основание

системы Счисления, в котором выполняются операции сложения в арифметическом устройстве ( 6 о П-1

2 , где ц разрядность мантиссы) j

Pj( и М - COOTветственно порядок и мантисса числа, Xj - наибольшее целое число, меньшее или равное К ( ) ГХ - наименьшее целое число, большее или равное X (потолок

X);

X mod Y - остаток от деления X на V .

В режиме Начальная установка рлок управления 2 вьщает на входы регистра 10 мантиссы первого блока 3 суммирования сдвинутую на 2 мантиссу первого слагаемого последовательности, чем обеспечивается ее перевод из двоичной системы счисления в систему счисления с основанием И - 1, Одновременно с этим на вход регистра 8 кода операций первого блока 3 суммирования из блока 2 управления вьдается код 000, обеспечивающий сложение мантиссы первого слагаемого с нулем, начиная с первого блока 3 суммирования, этим обеспечивается бчистка от результатов сложения предьщущей последовательностио

В режиме Сложение блок 2 управления вьщает на входы регистра 4 порядка первого блока 3 суммирования содержимое выходов сумматора 27, на входы регистра 10 мантиссы первого блока 3 суммирования - значение мантиссы 1-го слагаемого последовательности, представленной в системе счисления с основанием п - 1, на вход регистра 8 кода операций этого блока - код операции Сложение, равный 100. В блоках 3 суммирования в зависимости от сигнала на выходе элемента либо значение сумматора 6 порядка в процессе передачи в следующий блок 3 суммирования уменьшается на единицу, а мантисса слагаемого при этом остается без изменений (содержимое регистра 15 ь4Г1адшего разряда не меняется), либо значение сумматора 6 порядка передается в следующий блок 3 суммирования без изменения, а мантисса слагаемого складывается с содержимым регистра 15 младшего разряда. Старший разряд полученного таким образом промежуточного результата, представ.лённый И -двоичнщми разрядами, передается через группу 12 элементов И в регистр 10 мантиссы следующего блока 3 суммирования, а младший разряд этой промежуточной суммы складывается . содержимым сумматора 17 мантисс и записьюается в регистр 15; младшего разряда. Этому варианту соответствует О на выходе элемента ИЛИ 5, который возможен в том случае, когда осуществилось выравнивание порядков принятого слагаемого и порядка промежуточной

суммы.

В режиме Сдвиг блок 2 управления выдает на входы регистра 10 мантиссы первого блока 3 суммирования, нулевые значения, на входы регистра 8 кода операций зтого блока либо код 001, либо 010. В зависимости от значения второго и третьего разрядов регистра 8 кода операций первого блока 3 суммирования сдвиг промежуточного результата осуществляется через пятую группу элементов И 16 либо на один, либо на два разряда. Значение выходов регистра 4 порядка первого блока 3 суммирования не влияет на работу .устройства в данном режиме.

Б этом режиме осуществляется выравнивание порядков очередного елагаемого и промежуточной суммы при условии, что порядок слагаемого меньше порядка промежуточной суммы. В режиме Считывание блок 2 управления выдает на входы регистра 8 кода операций первого блока 3 суммирования код 010, на входы регистра 10 мантиссы этого блока нулевые значения, а значение выходо регистра 4 порядка не влияют на считываемьй результат. Считывание результата происходит в течение

1 ч +П + П

k 1, I-.,п J) тактов, в зависимости от заданной точности.. Необходимое количество тактов считыПримечание: Х- либо О, не влияющие

вания результата задается, внешней вычислительной системой, которая при наличии сигнала Готовность

вьщает на входы устройства либо очередной операнд последовательности для сложения и код 00 по входу Управление, либо выдает по входу Управление код 10, обеспечивающий формирование в блоке 2 управления необходимой управляющей информации.

Следует отметить, что, наряду с уменьшением аппаратурных затрат, данное устройство обладает более высоким быстродействием при заданной одинаковой точности.

Таблица 1 либо 1, комбинации адресных входов, на работу, не показаны.

Таблица 2

| Устройство для суммирования N @ -разрядных чисел | 1979 |

|

SU920707A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для одновременного выполнения операций сложения над множеством чисел | 1975 |

|

SU558276A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-30—Публикация

1984-04-27—Подача