Изобретение относится к цифровой вычислительной технике и может быть использовано при построении микропрограммных устройств управления распределенных цифровых систем, проектируемых на однотипных БИС и реализующих параллельные алгоритмы обработки информации.

Цель изобретения - расширение области применения за счет реализации любой дисциплины запуска и ожидания завершения параллельных участков микропрограмм.

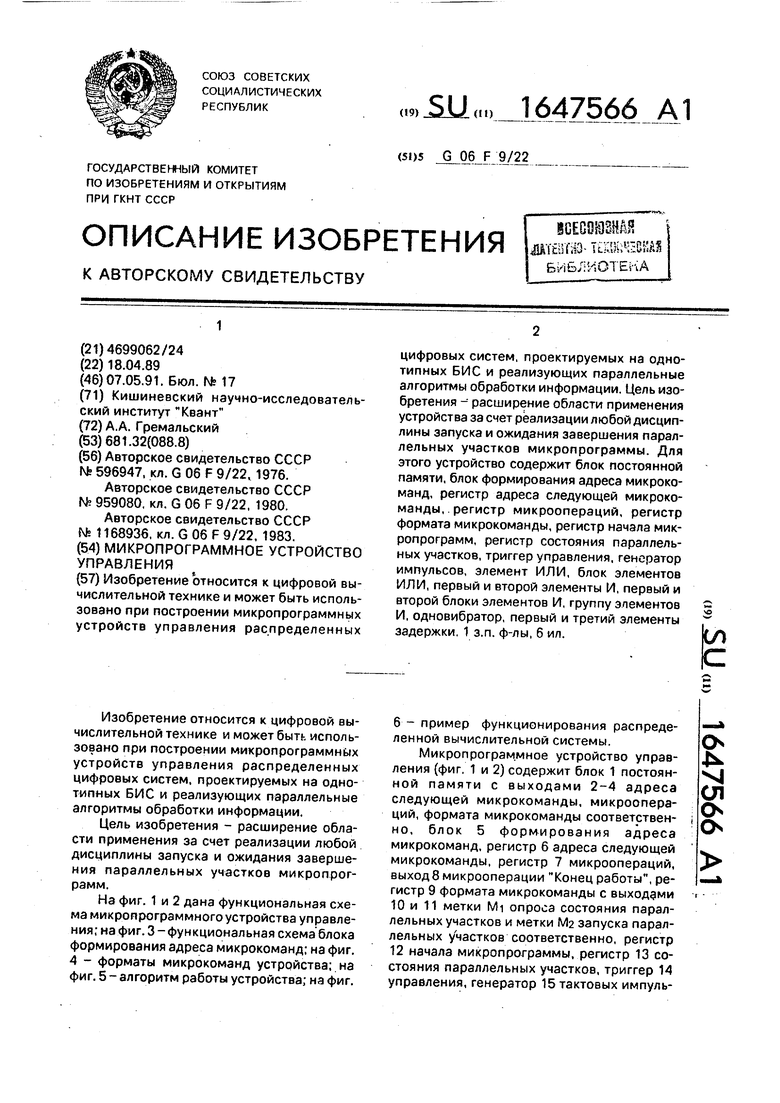

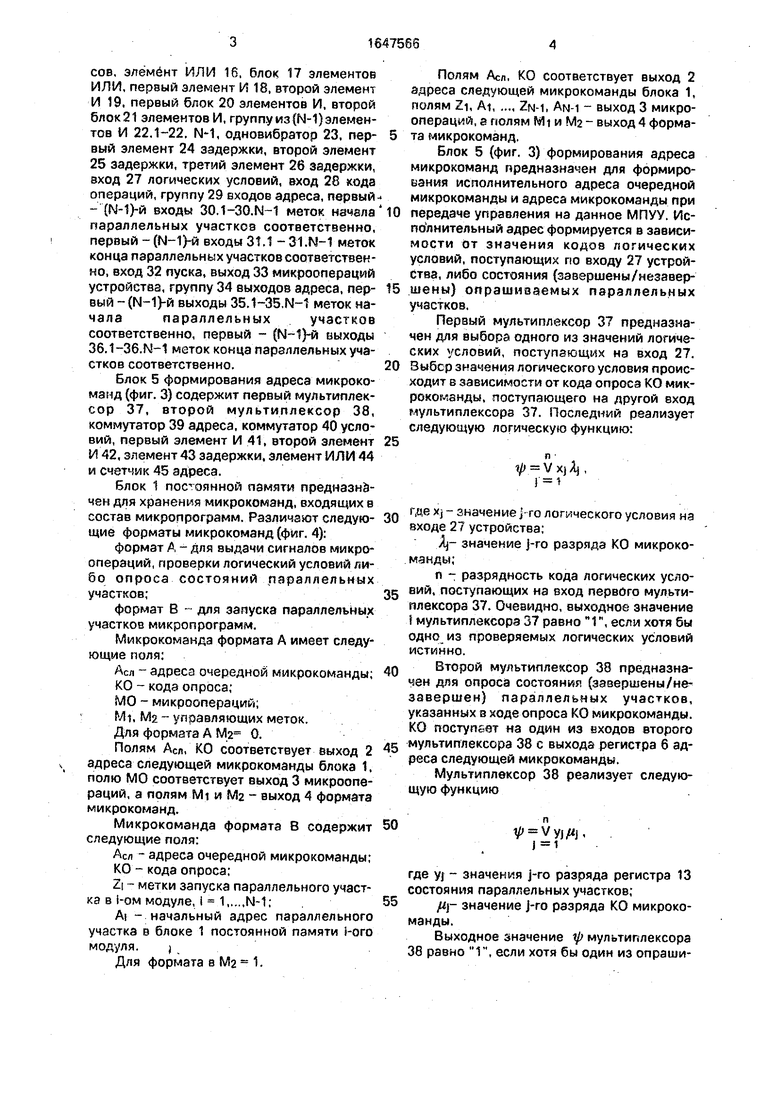

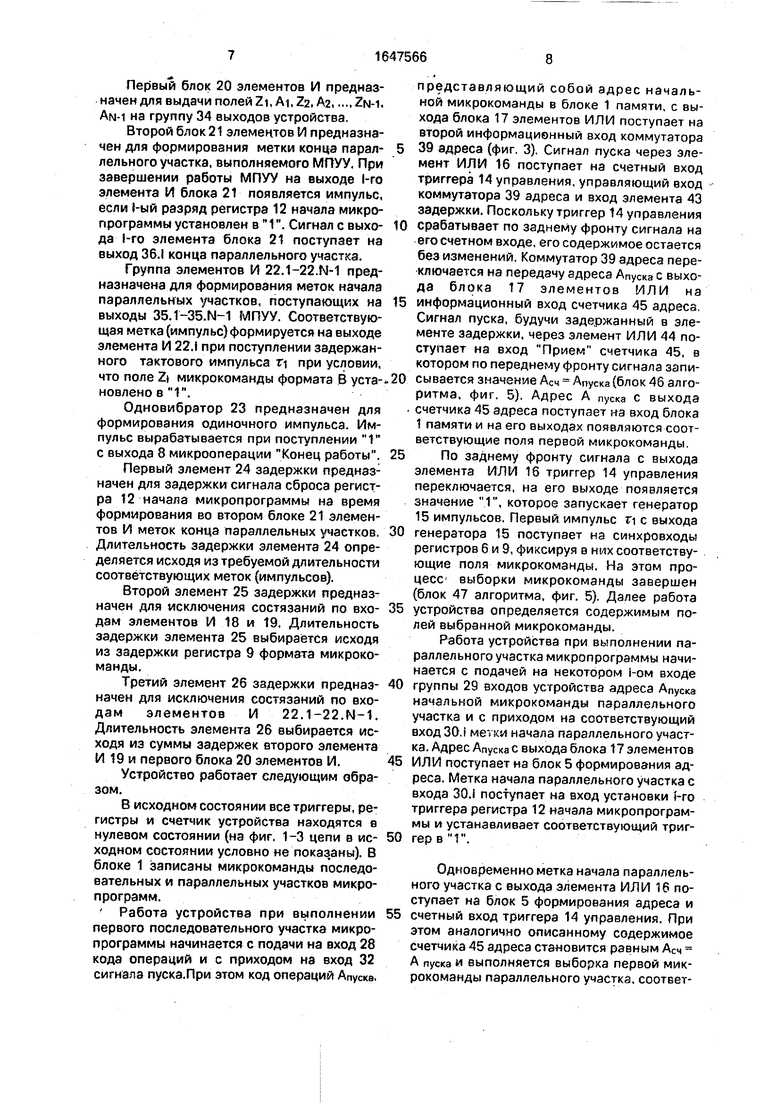

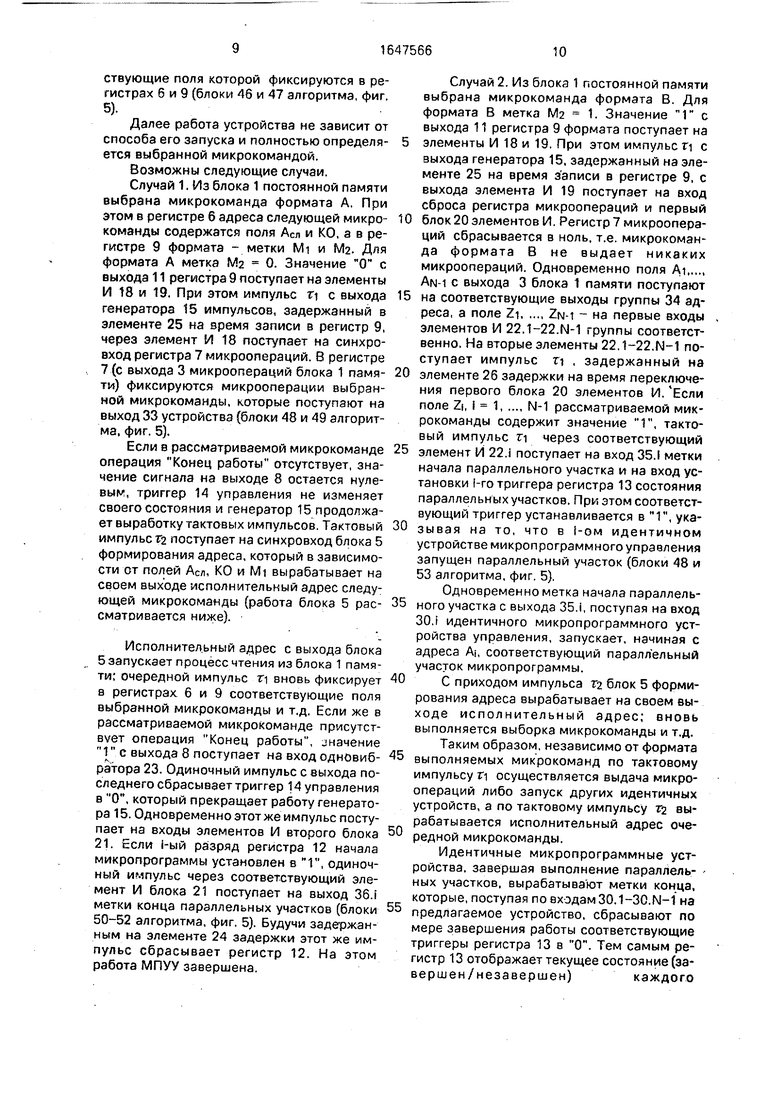

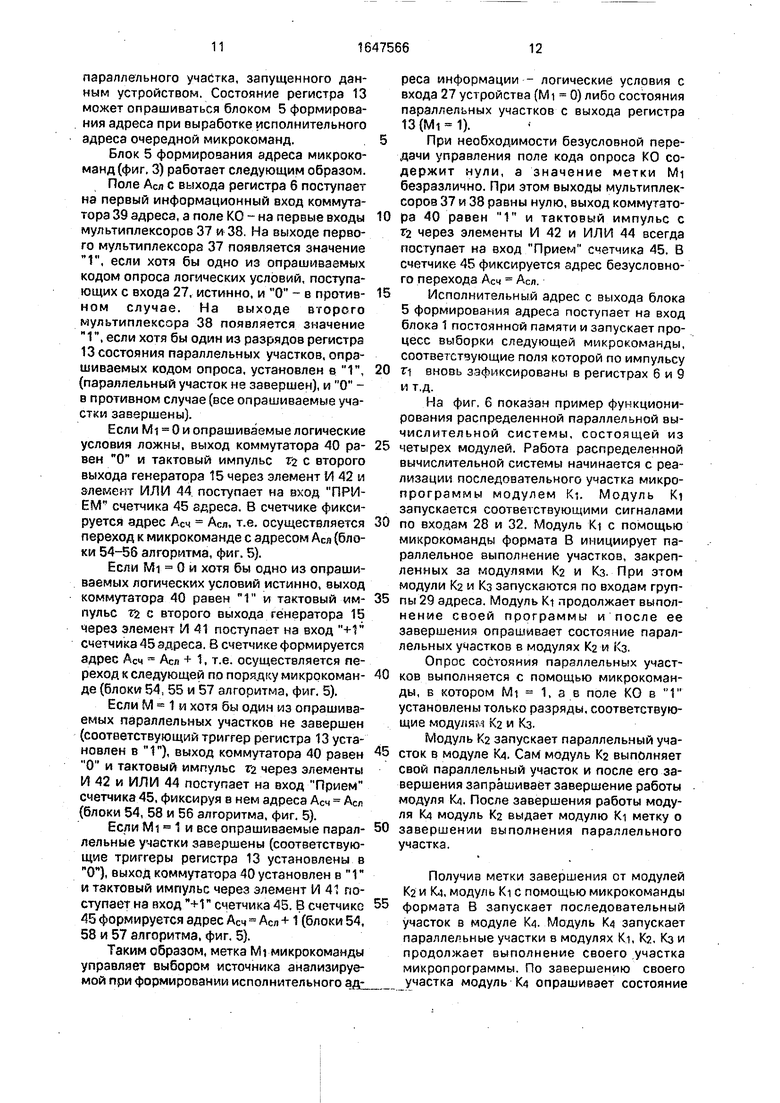

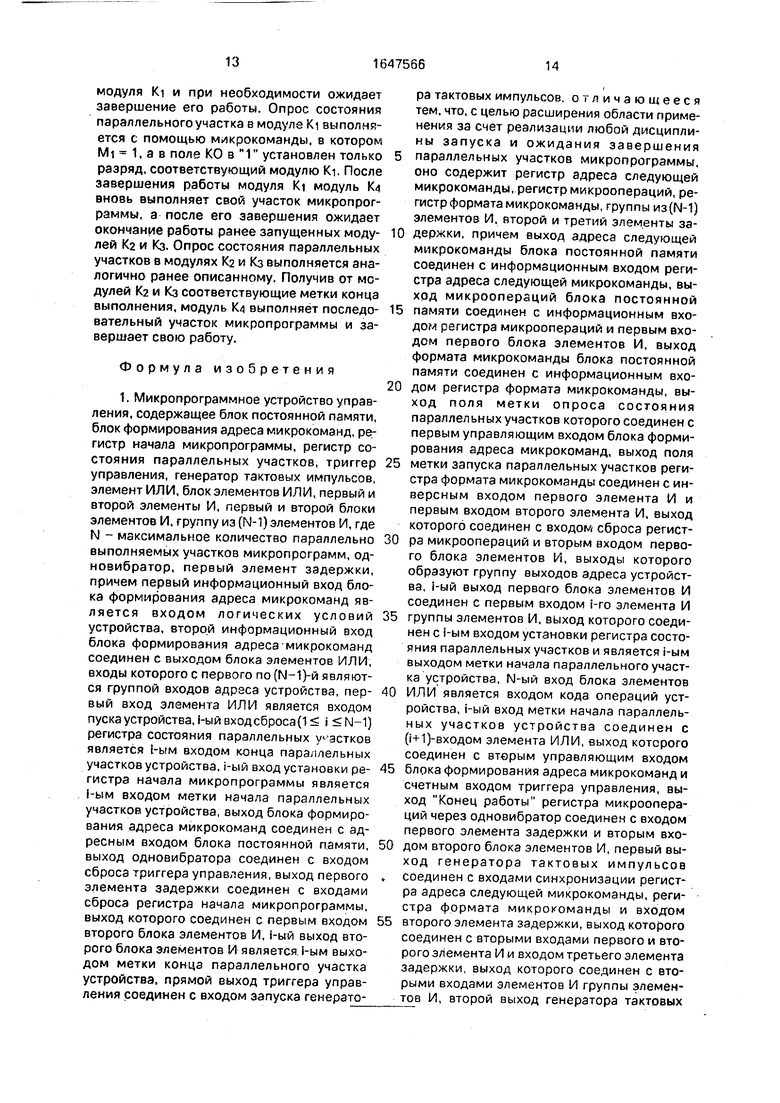

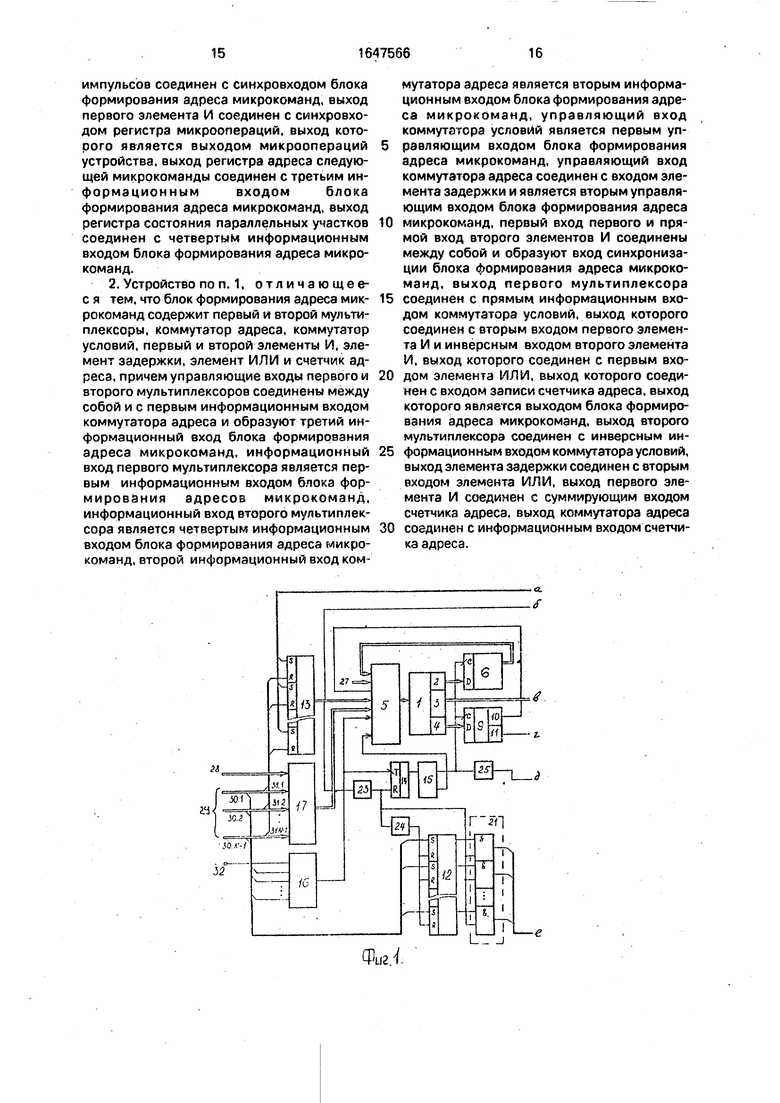

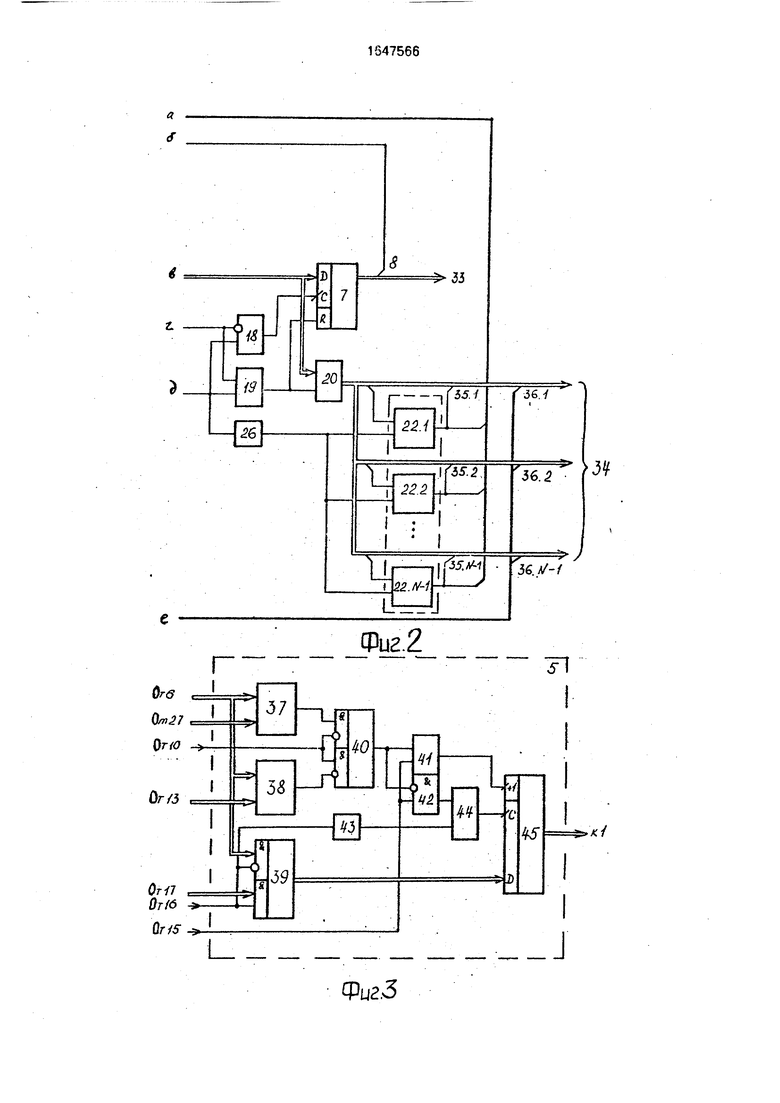

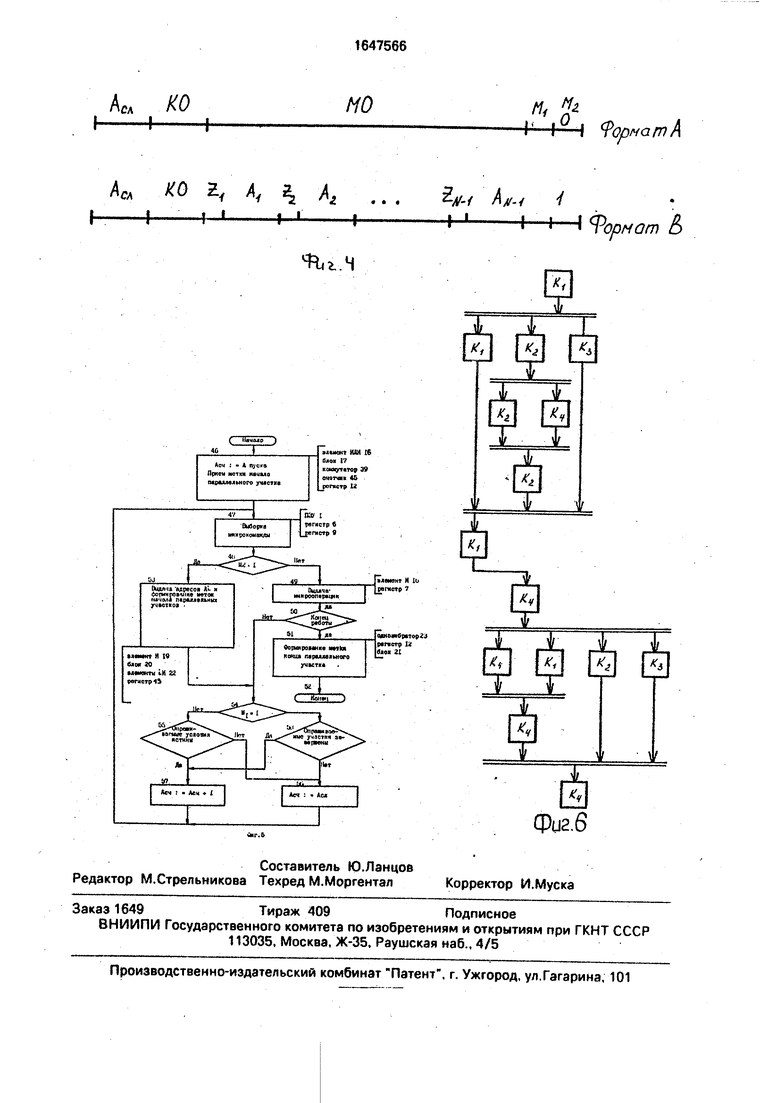

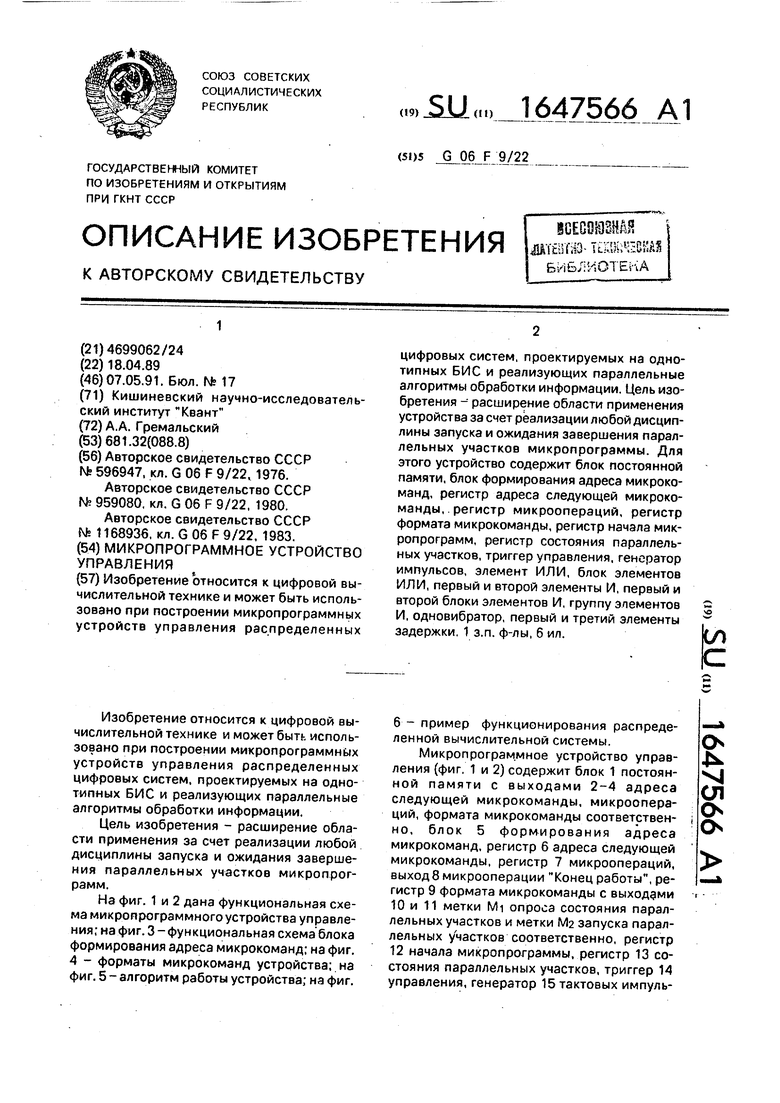

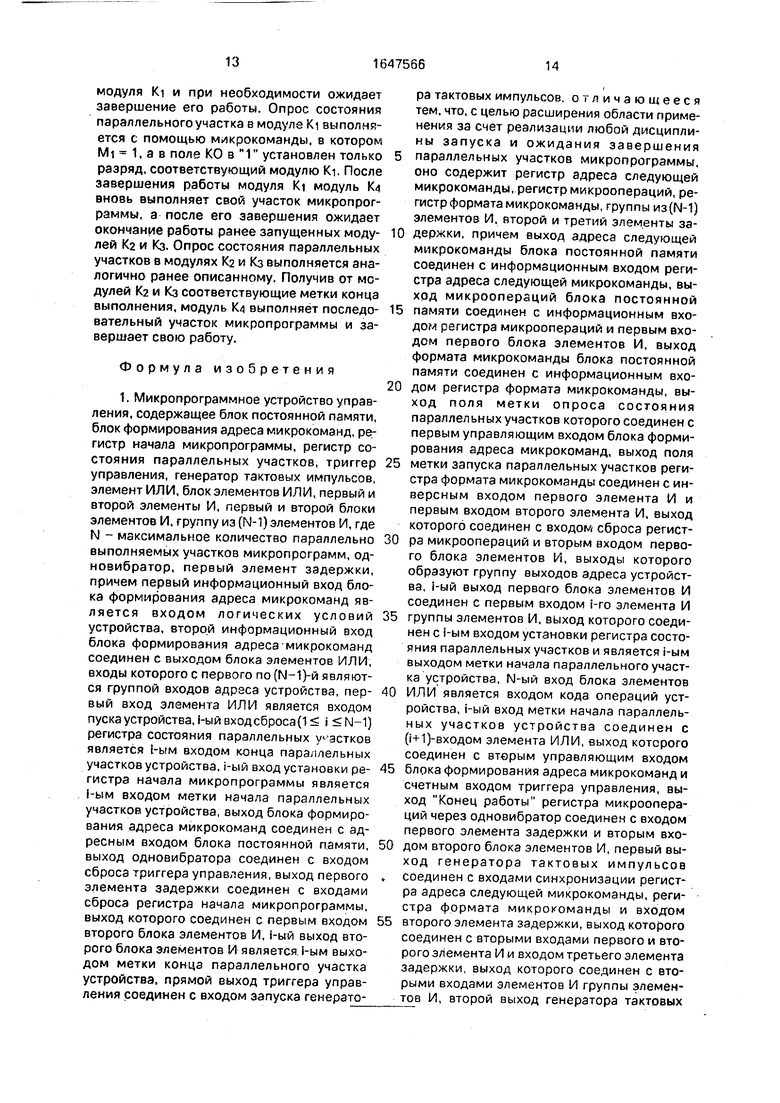

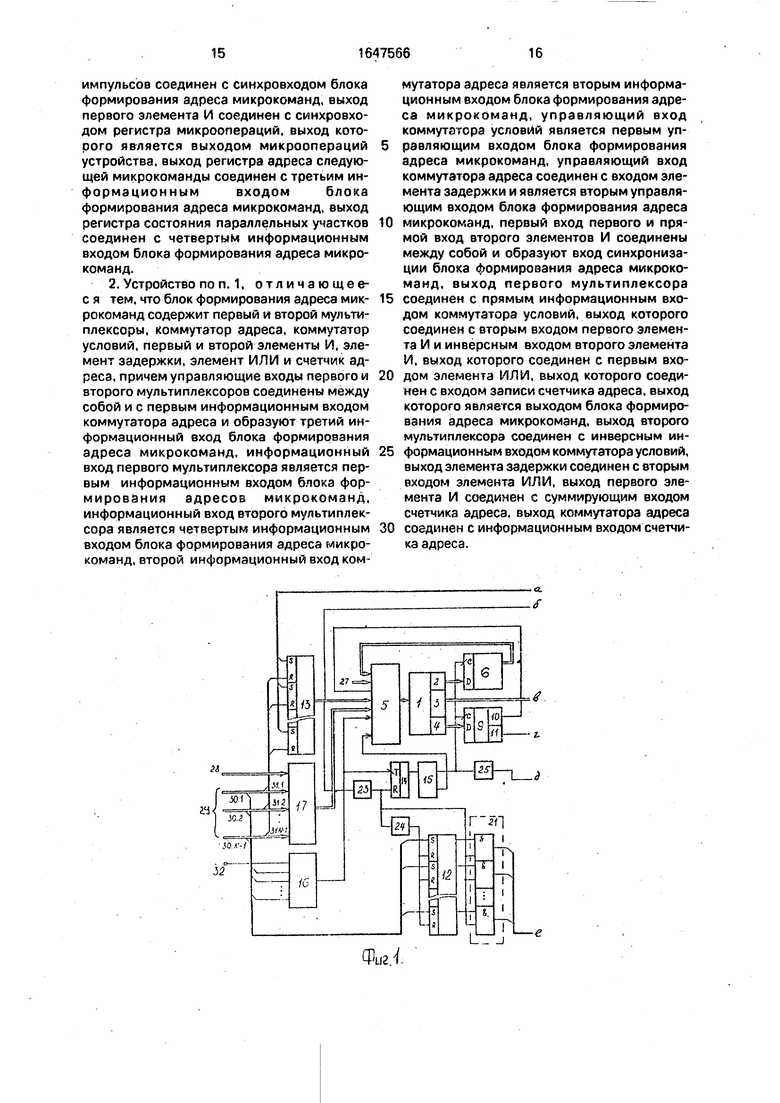

На фиг. 1 и 2 дана функциональная схема микропрограммного устройства управления; на фиг. 3 - функциональная схема блока формирования адреса микрокоманд; на фиг. 4 - форматы микрокоманд устройства; на фиг. 5 - алгоритм работы устройства; на фиг.

6 - пример функционирования распределенной вычислительной системы.

Микропрограммное устройство управления (фиг, 1 и 2) содержит блок 1 постоянной памяти с выходами 2-4 адреса следующей микрокоманды, микроопераций, формата микрокоманды соответственно, блок 5 формирования адреса микрокоманд, регистр 6 адреса следующей микрокоманды, регистр 7 микроопераций, выход 8 микрооперации Конец работы, регистр 9 формата микрокоманды с выходами 10 и 11 метки Mi опроса состояния параллельных участков и метки М2 запуска параллельных участков соответственно, регистр 12 начала микропрограммы, регистр 13 состояния параллельных участков, триггер 14 управления, генератор 15 тактовых импульО

VI ел о- о

сов, элемент ИЛИ 16, блок 17 элементов ИЛИ, первый элемент И 18, второй элемент И 19, первый блок 20 элементов И, второй блок 21 элементов И, группу из (N-1) элементов И 22.1-22. N 1, одновибратор 23, пер- вый элемент 24 задержки, второй элемент 25 задержки, третий элемент 26 задержки, вход 27 логических условий, вход 28 кода операций, группу 29 входов адреса, первый - (М-1)-й входы 30.1-3Q.N-1 меток начала параллельных участков соответственно, первый - (М-1)-й входы 3t,1 -31.W-1 меток конца параллельных участков соответственно, вход 32 пуска, выход 33 микроопераций устройства, группу 34 выходов адреса, пер- вый -(М-1)-й выходы 35.1-35.N-t меток началапараллельных участков соответственно, первый - ()-и выходы 36.1-36.N-1 меток конца параллельных участков соответственно.

Блок 5 формирования адреса микрокоманд (фиг. 3) содержит первый мультиплексор 37, второй мультиплексор 38, коммутатор 39 адреса, коммутатор 40 условий, первый элемент И 41, второй элемент И 42, элемент 43 задержки, элемент ИЛИ 44 и счетчик 45 адреса.

Блок 1 постоянной памяти предназначен для хранения микрокоманд, входящих в состав микропрограмм. Различают следую- щие форматы микрокоманд (фиг. 4):

формат А - для выдачи сигналов микроопераций, проверки логический условий либо опроса состояний параллельных участков;

формат В ™ для запуска параллельных участков микропрограмм.

Микрокоманда формата А имеет следующие поля:

Асл адреса очередной микрокоманды;

КО - кода опроса;

МО - микроопераций;

Mi, M2 - управляющих меток.

Для формата А Ма 0.

Полям Асл, КО соответствует выход 2 адреса следующей микрокоманды блока 1, полю МО соответствует выход 3 микроопераций, а полям Mi и Ма - выход 4 формата микрокоманд.

Микрокоманда формата В содержит следующие поля:

Асл - адреса очередной микрокоманды;

КО - кода опроса;

Zi - метки запуска параллельного участка в i-ом модуле, i 1N-1;

AI - начальный адрес параллельного участка в блоке 1 постоянной памяти Ього модуля. j

Для формата в Мг - 1.

Полям Асл, КО соответствует выход 2 адреса следующей микрокоманды блока 1, полям Zi, AIZN-I, AN-I выход 3 микроопераций, а полям Mi и М2 - выход 4 формата микрокоманд.

Блок 5 (фиг. 3) формирования адреса микрокоманд предназначен для формирования исполнительного адреса очередной микрокоманды и адреса микрокоманды при передаче управления на данное МПУУ. Ис- полнительный адрес формируется в зависимости от значения кодов логических условий, поступающих по входу 27 устройства, либо состояния (зэвершены/незавер- шены) опрашиваемых параллельных участков.

Первый мультиплексор 37 предназначен для выбора одного из значений логических условий, поступающих на вход 27. Выбср значения логического условия происходит в зависимости от кода опроса КО микрокоманды, поступающего на другой вход мультиплексора 37. Последний реализует следующую логическую функцию:

п

ф - v xj Aj,

} }

где Xj - значение j- го логического условия на входе 27 устройства;

Лр значение j-ro разряда КО микрокоманды;

л - разрядность кода логических условий, поступающих на вход первого мультиплексора 37. Очевидно, выходное значение } мультиплексора 37 равно 1, если хотя бы одно из проверяемых логических условий истинно.

Второй мультиплексор 38 предназначен для опроса состояния (завершены/незавершен) параллельных участков, указанных в ходе опроса КО микрокоманды. КО поступает «а один из входов второго мультиплексора 38 с выхода регистра 6 адреса следующей микрокоманды.

Мультиплексор 38 реализует следующую функцию

V ,

где yj - значения j-ro разряда регистра 13 состояния параллельных участков;

//j- значение j-ro разряда КО микрокоманды.

Выходное значение ty мультиплексора 38 равно 1, если хотя бы один из опрашиваемых параллельных участков незавершен, т.е. yj 1.

Коммутатор 39 адреса предназначен для передачи на информационный вход счетчика 45 начального адреса микропрограммы или параллельного участка. Если сигнал пуска, поступающий на вход блока 5 с выхода элемента ИЛИ 16, равен 14, на выход коммутатора 39 адреса передается адрес с выхода блока 17 элементов ИЛИ. В противном случае на выход коммутатора 39 передается адрес Асл микрокоманды, поступающий с выхода регистра 6 адреса следующей микрокоманды.

Коммутатор 40 условий предназначен для передачи на вход элементов И 41 и 42 результата анализа логических условий либо результата опроса состояния параллельных участков. Если значение метки Mi равно 1, на выход коммутатора 40 с выхода мультиплексора 38 передается инверсное значение результата опроса состояния параллельных участков.

Элементы И 41 и 42 предназначены для формирования управляющих сигналов +1 и Прием счетчика 45 адреса. Управляющие сигналы формируются в момент прихода тактового импульса тг в зависимости от значения метки Mi, полей АСл и КО соответствующих микрокоманд. Если выход коммутатора 40 условий установлен в О, формируется управляющий сигнал Прием. В противном случае формируется управляющий сигнал +1.

Элемент43 задержки предназначен для устранения состязаний на входах счетчика 45 адреса. Длительность задержки элемента 43 выбирается исходя из задержки коммутатора 39 адреса,

Элемент ИЛИ 44 предназначен для объединения управляющих сигналов, поступающих с входа пуска блока 5 и выхода элемента И 42.

Счетчик 45 адреса предназначен для формирования и хранения исполнительного адреса микрокоманд. При наличии на входе счетчика 45 управляющего сигнала Прием в счетчик 45 фиксируется код с его информационного входа, т.е. выполняется принудительная адресация следующей микрокоманды. При наличии на входе счетчика 45 управляющего сигнала +1 его содержимое увеличивается на единицу, т.е. выполняется естественная адресация очередной микрокоманды.

Регистр 6 адреса предназначен для хранения полей АСЛ и КО, поступающих с выхода 2 адреса блока 1 постоянной памяти.

Регистр 7 микроопераций необходим для хранения поля МО, поступающего с выхода 3 блока 1 постоянной памяти.

Регистр 9 формата микрокоманды предназначен для хранения меток Mi и М2, поступающих с выхода 4 блока 1 постоянной памяти.

Регистр 12 начала микропрограмм служит для хранения метки начала параллельного участка, поступающей по одному из входов 30.1 -30.N-1.

Регистр 13 состояния параллельных участков служит для отображения состояния всех параллельных участков, запускаемых МПУУ. Если 1-ый разряд регистра установлен в 1, 1-ый параллельный участок незавершен. В противном случае соответствующий участок завершен.

Разряд i устанавливается в 1 сигналом с выхода элемента И 22.i при запуске МПУУ соответствующего параллельного участка и сбрасывается в О при поступлении на вход 31.1 метки конца соответствующего параллельного участка.

Триггер 14 управления служит для запуска и останова МПУУ.

Генератор 15 импульсов формирует на своих выходах две последовательности сдвинутых одна относительно другой синхроимпульсов ri и Г2 . Генератор вырабатывает импульсы только при наличии на его управляющем входе сигнала 1

Элемент ИЛИ 16 предназначен для формирования сигнала запуска устройства Запуск устройства выполняется либо от сигнала Пуск, поступающего с входа 32, либо от одной из меток начала параллельного участка, поступающей по входам 30.1- 30.N-1

Блок 17 элементов ИЛИ предназначен для формирования начального адреса микропрограммы либо параллельного участка. Начальный адрес микропрограммы поступает с входа 28 а начальные адреса параллельных участков - с входов группы 29

Элемент И 18 предназначен для формирования сигнала Прием в регистр 7 микроопераций. Сигнал Прием формируется при условии, что метка Ма 0 при поступлении задержанного тактового импульса т. Элемент И 19 предназначен для формирования сигнала Сброс регистра 7 микрооперации и сигнала разрешения выдачи полей Zi, Ai, Z2, А2ZN-I, AN-Ч на группу 34

выходов устройства. Сигнал на выходе элемента И 19 формируется при условии, что метка М2 1 при поступлении задержанного тактового импульса т .

Первый блок 20 элементов И предназначен для выдачи полей Zi, Ai, Zz, A2,.... ZN-L Ам-1 на группу 34 выходов устройства.

Второй блок 21 элементов И предназначен для формирования метки конца параллельного участка, выполняемого МЛУУ. При завершении работы МПУУ на выходе 1-го элемента И блока 21 появляется импульс, если 1-ый разряд регистра 12 начала микропрограммы установлен в 1. Сигнал с выхода 1-го элемента блока 21 поступает на выход 36.I конца параллельного участка.

Группа элементов И 22.1-22.N-1 предназначена для формирования меток начала параллельных участков, поступающих на выходы 35.1-35.N-1 1ИПУУ. Соответствующая метка (импульс) формируется на выходе элемента И 22.1 при поступлении задержанного тактового импульса ri при условии, что поле Z микрокоманды формата В установлено в 1.

Одновибратор 23 предназначен для формирования одиночного импульса. Импульс вырабатывается при поступлении 1 с выхода 8 микрооперации Конец работы.

Первый элемент 24 задержки предназначен для задержки сигнала сброса регистра 12 начала микропрограммы на время формирования во втором блоке 21 элементов И меток конца параллельных участков. Длительность задержки элемента 24 определяется исходя из требуемой длительности соответствующих меток (импульсов).

Второй элемент 25 задержки предназначен для исключения состязаний по входам элементов И 18 и 19. Длительность задержки элемента 25 выбирается исходя из задержки регистра 9 формата микрокоманды.

Третий элемент 26 задержки предназначен для исключения состязаний по входам элементов И 22.1-22.W-1. Длительность элемента 26 выбирается исходя из суммы задержек второго элемента И 19 и первого блока 20 элементов И.

Устройство работает следующим образом.

В исходном состоянии все триггеры, регистры и счетчик устройства находятся в нулевом состоянии (на фиг. 1-3 цепи в исходном состоянии условно не показаны). В блоке 1 записаны микрокоманды последовательных и параллельных участков микропрограмм.

Работа устройства при выполнении первого последовательного участка микропрограммы начинается с подачи на вход 28 кода операций и с приходом на вход 32 сигнала пуска.При этом код операций .

представляющий собой адрес начальной микрокоманды в блоке 1 памяти, с выхода блока 17 элементов ИЛИ поступает на второй информационный вход коммутатора

5 39 адреса (фиг. 3). Сигнал пуска через элемент ИЛИ 16 поступает на счетный вход триггера 14 управления, управляющий вход коммутатора 39 адреса и вход элемента 43 задержки. Поскольку триггер 14 управления

0 срабатывает по заднему фронту сигнала на его счетном входе, его содержимое остается без изменений. Коммутатор 39 адреса переключается на передачу адреса Апуска с выхода блока 17 элементов ИЛИ на

5 информационный вход счетчика 45 адреса. Сигнал пуска, будучи задержанный в элементе задержки, через элемент ИЛИ 44 поступает на вход Прием счетчика 45, в котором по переднему фронту сигнала запи- 0 сывается значение Асч Апуска (блок 46 алгоритма, фиг. 5). Адрес А пуска с выхода . счетчика 45 адреса поступает на вход блока 1 памяти и на его выходах появляются соответствующие поля первой микрокоманды.

5 По заднему фронту сигнала с выхода элемента ИЛИ 16 триггер 14 управления переключается, на его выходе появляется значение 1, которое запускает генератор 15 импульсов. Первый импульс ri с выхода

0 генератора 15 поступает на синхровходы регистров 6 и 9, фиксируя в них соответствующие поля микрокоманды. На этом процесс1 выборки микрокоманды завершен (блок 47 алгоритма, фиг. 5). Далее работа

5 устройства определяется содержимым полей выбранной микрокоманды.

Работа устройства при выполнении параллельного участка микропрограммы начинается с подачей на некотором i-ом входе

0 группы 29 входов устройства адреса Апуска начальной микрокоманды параллельного участка и с приходом на соответствующий вход 30.i ш начала параллельного участка. Адрес Апуска с выхода блока 17 элементов

5 ИЛИ поступает на блок 5 формирования адреса. Метка начала параллельного участка с входа 30.I поступает на вход установки {-го триггера регистра 12 начала микропрограммы и устанавливает соответствующий триг0 герв Т.

Одновременно метка начала параллельного участка с выхода элемента ИЛИ 16 поступает на блок 5 формирования адреса и 5 счетный вход триггера 14 управления. При этом аналогично описанному содержимое счетчика 45 адреса становится равным АСч А пуска и выполняется выборка первой микрокоманды параллельного участка, соответствующие поля шторой фиксируются в регистрах б и 9 (блоки 46 и 47 алгоритма, фиг. 5).

Далее работа устройства не зависит от способа его запуска и полностью определи- ется выбранной микрокомандой.

Возможны следующие случаи.

Случай 1. Из блока 1 постоянной памяти выбрана микрокоманда формата А. При этом в регистре 6 адреса следующей микро- команды содержатся поля АСл и КО, а в регистре 9 формата - метки MI и М2. Для формата А метка Ма 0. Значение 0м с выхода 11 регистра 9 поступает на элементы И 18 и 19. При этом импульс т с выхода генератора 15 импульсов, задержанный в элементе 25 на время записи в регистр 9, через элемент И 18 поступает на синхро- вход регистра 7 микроопераций. В регистре 7 (с выхода 3 микроопераций блока 1 памя- ти) фиксируются микрооперации выбранной микрокоманды, которые поступают на выход 33 устройства (блоки 48 и 49 алгоритма, фиг. 5).

Если в рассматриваемой микрокоманде операция Конец работы отсутствует, значение сигнала на выходе 8 остается нулевым, триггер 14 управления не изменяет своего состояния и генератор 15 продолжает выработку тактовых импульсов. Тактовый импульс Г2 поступает на синхровход блока 5 формирования адреса, который в зависимости от полей АСЛ, КО и Mi вырабатывает на своем выходе исполнительный адрес следующей микрокоманды (работа блока 5 рас- сматоивается ниже).

Исполнительный адрес с выхода блока 5 запускает процесс чтения из блока 1 памяти; очередной импульс т вновь фиксирует в регистрах 6 и 9 соответствующие поля выбранной микрокоманды и т.д. Если же в рассматриваемой микрокоманде присутствует операция Конец работы, лначение 1 с выхода 8 поступает навхододновиб- ратора 23. Одиночный импульс с выхода последнего сбрасывает триггер 14 управления в О, который прекращает работу генератора 15. Одновременно этот же импульс поступает на входы элементов И второго блока 21. Если i-ый разряд регистра 12 начала микропрограммы установлен в 1, одиночный импульс через соответствующий элемент И блока 21 поступает на выход 36.1 метки конца параллельных участков (блоки 50-52 алгоритма, фиг. 5). Будучи задержанным на элементе 24 задержки этот же импульс сбрасывает регистр 12. На этом работа МПУУ завершена.

Случай 2. Из блока 1 постоянной памяти выбрана микрокоманда формата В. Для формата В метка М2 1. Значение 1 с выхода 11 регистра 9 формата поступает на элементы И 18 и 19. При этом импульс Г| с выхода генератора 15, задержанный на элементе 25 на время записи в регистре 9, с выхода элемента И 19 поступает на вход сброса регистра микроопераций и первый блок 20 элементов И. Регистр 7 микроопераций сбрасывается в ноль, т.е. микрокоманда формата В не выдает никаких микроопераций. Одновременно поля Ai,..., Ам-1 с выхода 3 блока 1 памяти поступают на соответствующие выходы группы 34 адреса, а поле ZiZN-I - на первые входы

элементов И 22.1-22.N-1 группы соответственно. На вторые элементы 22.1-22.N-1 поступает импульс ri , задержанный на элементе 26 задержки на время переключения первого блока 20 элементов И. Если поле Zi, i 1, ..., N-1 рассматриваемой микрокоманды содержит значение 1, тактовый импульс ri через соответствующий элемент И 22.i поступает на вход 35.1 метки начала параллельного участка и на вход установки 1-го триггера регистра 13 состояния параллельных участков. При этом соответствующий триггер устанавливается в 1, указывая на то, что в t-ом идентичном устройстве микропрограммного управления запущен параллельный участок (блоки 48 и 53 алгоритма, фиг. 5).

Одновременно метка начала параллельного участка с выхода 35., поступая на вход 30.1 идентичного микропрограммного устройства управления, запускает, начиная с адреса Ai, соответствующий параллельный участок микропрограммы.

С приходом импульса ti блок 5 формирования адреса вырабатывает на своем выходе исполнительный адрес, вновь выполняется выборка микрокоманды и т.д.

Таким образом, независимо от формата выполняемых микрокоманд по тактовому импульсу ri осуществляется выдача микроопераций либо запуск других идентичных устройств, а по тактовому импульсу Т5 вырабатывается исполнительный адрес очередной микрокоманды.

Идентичные микропрограммные устройства, завершая выполнение параллельных участков, вырабатывают метки конца, которые, поступая по входам 30.1-30.N-1 на предлагаемое устройство, сбрасывают по мере завершения работы соответствующие триггеры регистра 13 в О. Тем самым регистр 13 отображает текущее состояние (завершен/незавершен)каждого

параллельного участка, запущенного данным устройством. Состояние регистра 13 может опрашиваться блоком 5 формирования адреса при выработке исполнительного адреса очередной микрокоманд.

Блок 5 формирования адреса микрокоманд (фиг. 3) работает следующим образом.

Поле Асл с выхода регистра б поступает на первый информационный вход коммутатора 39 адреса, а поле КО - на первые входы мультиплексоров 37 и 38. На выходе первого мультиплексора 37 появляется значение 1, если хотя бы одно из опрашиваемых кодом опроса логических условий, поступающих с входа 27, истинно, и О - в против- ном случае. На выходе второго мультиплексора 38 появляется значение 1, если хотя бы один из разрядов регистра 13 состояния параллельных участков, опрашиваемых кодом опроса, установлен в 1, (параллельный участок не завершен), и О - в противном случае (все опрашиваемые участки завершены).

Если Mt 0 и опрашиваемые логические условия ложны, выход коммутатора 40 ра- вен О и тактовый импульс Тг с второго выхода генератора 15 через элемент И 42 и элемент ИЛИ 44 поступает на вход ПРИЕМ счетчика 45 адреса. В счетчике фиксируется адрес Асч Асл, т.е. осуществляется переход к микрокоманде с адресом АСл (блоки 54-56 алгоритма, фиг. 5).

Если Mi 0 и хотя бы одно из опрашиваемых логических условий истинно, выход коммутатора 40 равен 1 и тактовый им- пульс с второго выхода генератора 15 через элемент И 41 поступает на вход +Т счетчика 45 адреса. 8 счетчике формируется адрес АСЧ АСЛ + 1, т.е. осуществляется переход к следующей по порядку микрокоман- де (блоки 54, 55 и 57 алгоритма, фиг. 5).

Если М 1 и хотя бы один из опрашиваемых параллельных участков не завершен (соответствующий триггер регистра 13 установлен в Г), выход коммутатора 40 равен О и тактовый импульс Г2 через элементы И 42 и ИЛИ 44 поступает на вход Прием счетчика 45, фиксируя в нем адреса АСч АСл (блоки 54, 58 и 56 алгоритма, фиг. 5).

Если Mi 1 и все опрашиваемые парал- лельные участки завершены (соответствующие триггеры регистра 13 установлены в О), выход коммутатора 40 установлен в Г и тактовый импульс через элемент И 41 поступает на вход -И счетчика 45. В счетчике 45 формируется адрес АСч АСл +1 (блоки 54, 58 и 57 алгоритма, фиг. 5).

Таким образом, метка Mi микрокоманды управляет выбором источника анализируемой при формировании исполнительного ajt

реса информации - логические условия с входа 27 устройства (Mi 0) либо состояния параллельных участков с выхода регистра t3(Mi 1).

При необходимости безусловной передачи управления поле кода опроса КО содержит нули, а значение метки Mi безразлично. При этом выходы мультиплексоров 37 и 38 равны нулю, выход коммутатора 40 равен 1 и тактовый импульс с Г2 через элементы И 42 и ИЛИ 44 всегда поступает на вход Прием с«етчика 45. В счетчике 45 фиксируется адрес безусловного перехода Асч Асл.

Исполнительный адрес с выхода блока 5 формирования адреса поступает на вход блока 1 постоянной памяти и запускает процесс выборки следующей микрокоманды, соответствующие поля которой по импульсу Г| вновь зафиксированы в регистрах 6 и 9 и т.д.

На фиг, 6 показан пример функционирования распределенной параллельной вычислительной системы, состоящей из четырех модулей. Работа распределенной вычислительной системы начинается с реализации последовательного участка микро- программы модулем Ki. Модуль KI запускается соответствующими сигналами по входам 28 и 32. Модуль Ki с помощью микрокоманды формата В инициирует параллельное выполнение участков, закрепленных за модулями К.2 и Кз. При этом модули Кг и Кз запускаются по входам группы 29 адреса. Модуль Ki продолжает выполнение своей программы и после ее завершения опрашивает состояние параллельных участков в модулях К2 и Кз.

Опрос состояния параллельных участков выполняется с помощью микрокоманды, в котором Mi 1, а в поле КО в 1 установлены только разряды, соответствующие модулям Кз и Кз.

Модуль К2 запускает параллельный участок в модуле Ю. Сам модуль К2 выполняет свой параллельный участок и после его завершения запрашивает завершение работы модуля Id. После завершения работы модуля Кд модуль Кг выдает модулю Ki метку о завершении выполнения параллельного участка.

Получив метки завершения от модулей К2 и K«i, модуль Ki с помощью микрокоманды формата В запускает последовательный участок в модуле К.А. Модуль Кз запускает параллельные участки в модулях Ki, K2, Кз и продолжает выполнение своего участка микропрограммы. По завершению своего участка модуль Кз опрашивает состояни

модуля Ki и при необходимости ожидает завершение его работы. Опрос состояния параллельного участка в модуле Ki выполняется с помощью микрокоманды, в котором Mi 1. а в поле КО в 1 установлен только разряд, соответствующий модулю KL После завершения работы модуля Ki модуль К4 вновь выполняет свой участок микропрограммы, а после его завершения ожидает окончание работы ранее запущенных моду- лей Кз и Кз. Опрос состояния параллельных участков в модулях Kz и Кз выполняется аналогично ранее описанному. Получив от модулей Ка и Кз соответствующие метки конца выполнения, модуль Кз выполняет последо- вательный участок микропрограммы и завершает свою работу.

Формула изобретения

1, Микропрограммное устройство управления, содержащее блок постоянной памяти, блок формирования адреса микрокоманд, регистр начала микропрограммы, регистр состояния параллельных участков, триггер управления, генератор тактовых импульсов, элемент ИЛИ, блок элементов ИЛИ, первый и второй элементы И, первый и второй блоки элементов И, группу из (N-1) элементов И, где N - максимальное количество параллельно выполняемых участков микропрограмм, од- новибратор, первый элемент задержки, причем первый информационный вход блока формирования адреса микрокоманд является входом логических условий устройства, второй информационный вход блока формирования адреса микрокоманд соединен с выходом блока элементов ИЛИ, входы которого с первого по (N-1)-u являются группой входов адреса устройства, пер- вый вход элемента ИЛИ является входом пуска устройства, i-ый входсброса{1 i N-1) регистра состояния параллельных у зстков является i-ым входом конца параллельных участков устройства, i-ый вход установки ре- гистра начала микропрограммы является 1-ым входом метки начала параллельных участков устройства, выход блока формирования адреса микрокоманд соединен с адресным входом блока постоянной памяти, выход одновибратора соединен с входом сброса триггера управления, выход первого элемента задержки соединен с входами сброса регистра начала микропрограммы, выход которого соединен с первым входом второго блока элементов И, i-ый выход второго блока элементов И является 1-ым выходом метки конца параллельного участка устройства, прямой выход триггера управления соединен с входом запуска генерато50 5

0

5 0 5 0 5 0 5

ра тактовых импульсов, отличающееся тем, что, с целью расширения области применения за счет реализации любой дисциплины запуска и ожидания завершения параллельных участков микропрограммы, оно содержит регистр адреса следующей микрокоманды, регистр микроопераций, регистр формата микрокоманды, группы из(М-1) элементов И, второй и третий элементы задержки, причем выход адреса следующей микрокоманды блока постоянной памяти соединен с информационным входом регистра адреса следующей микрокоманды, выход микроопераций блока постоянной памяти соединен с информационным входом регистра микроопераций и первым входом первого блока элементов И, выход формата микрокоманды блока постоянной памяти соединен с информационным входом регистра формата микрокоманды, выход поля метки опроса состояния параллельных участков которого соединен с первым управляющим входом блока формирования адреса микрокоманд, выход поля метки запуска параллельных участков регистра формата микрокоманды соединен с инверсным входом первого элемента И и первым входом второго элемента И, выход которого соединен с входом сброса регистра микроопераций и вторым входом первого блока элементов И, выходы которого образуют группу выходов адреса устройства, i-ый выход первого блока элементов И соединен с первым входом i-ro элемента И группы элементов И, выход которого соединен с i-ым входом установки регистра состояния параллельных участков и является i-ым выходом метки начала параллельного участка устройства, N-ый вход блока элементов ИЛИ является входом кода операций устройства, i-ый вход метки начала параллельных участков устройства соединен с 0+1)-входом элемента ИЛИ, выход которого соединен с вторым управляющим входом блока формирования адреса микрокоманд и счетным входом триггера управления, выход Конец работы регистра микроопераций через одновибратор соединен с входом первого элемента задержки и вторым входом второго блока элементов И, первый выход генератора тактовых импульсов соединен с входами синхронизации регистра адреса следующей микрокоманды, регистра формата микрокоманды и входом второго элемента задержки, выход которого соединен с вторыми входами первого и второго элемента И и входом третьего элемента задержки, выход которого соединен с вторыми входами элементов И группы элементов И, второй выход генератора тактовых

импульсов соединен с синхровходом блока формирования адреса микрокоманд, выход первого элемента И соединен с синхровходом регистра микроопераций, выход которого является выходом микроопераций устройства, выход регистра адреса следующей микрокоманды соединен с третьим ин- формационным входом блока формирования адреса микрокоманд, выход регистра состояния параллельных участков соединен с четвертым информационным входом блока формирования адреса микрокоманд.

2.Устройствопоп.1, отличающее- с я тем, что блок формирования адреса микрокоманд содержит первый и второй мультиплексоры, коммутатор адреса, коммутатор условий, первый и второй элементы И, элемент задержки, элемент ИЛИ и счетчик адреса, причем управляющие входы первого и второго мультиплексоров соединены между собой и с первым информационным входом коммутатора адреса и образуют третий информационный вход блока формирования адреса микрокоманд, информационный вход первого мультиплексора является первым информационным входом блока формирования адресов микрокоманд, информационный вход второго мультиплексора является четвертым информационным входом блока формирования адреса микрокоманд, второй информационный вход коммутатора адреса является вторым информационным входом блока формирования адреса микрокоманд, управляющий вход коммутатора условий является первым управляющим входом блока формирования адреса микрокоманд, управляющий вход коммутатора адреса соединен с входом элемента задержки и является вторым управляющим входом блока формирования адреса

микрокоманд, первый вход первого и прямой вход второго элементов И соединены между собой и образуют вход синхронизации блока формирования адреса микрокоманд, выход первого мультиплексора

соединен с прямым информационным входом коммутатора условий, выход которого соединен с вторым входом первого элемента И и инверсным входом второго элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с входом записи счетчика адреса, выход которого является выходом блока формирования адреса микрокоманд, выход второго мультиплексора соединен с инверсным информационным входом коммутатора условий, выход элемента задержки соединен с вторым входом элемента ИЛИ, выход первого элемента И соединен с суммирующим входом счетчика адреса, выход коммутатора адреса

соединен с информационным входом счетчика адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении микропрограммных устройств управления распределенных цифровых систем, проектируемых на однотипных БИС и реализующих параллельные алгоритмы обработки информации. Цель изобретения - расширение области применения устройства за счет реализации любой дисциплины запуска и ожидания завершения параллельных участков микропрограммы. Для этого устройство содержит блок постоянной памяти, блок формирования адреса микрокоманд, регистр адреса следующей микрокоманды, регистр микроопераций, регистр формата микрокоманды, регистр начала микропрограмм, регистр состояния параллельных участков, триггер управления, генератор импульсов, элемент ИЛИ, блок элементов ИЛИ, первый и второй элементы И, первый и второй блоки элементов И, группу элементов И, одновибратор, первый и третий элементы задержки, 1 з.п. ф-лы, 6 ил. СП

а

Фиг. /

i

а f

Or/5

Фиг.З

Фиг.2

АСА КО I1н

МО

Ас, КО И, А, а, АЈ ...

|jf-JМ,

г..Ч

эдышх ИДИ Ј6 блом I KCMqnrerop 39 омотчик 4& рогястр Iii

о2

Г Г УорматЬ

2-tt i hit- /

-ь1h-4-ч 9 &

емпит И 1ь 1И«р7

t

Фиг.б

| Микропрограммное устройство управления | 1976 |

|

SU596947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1980 |

|

SU959080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-07—Публикация

1989-04-18—Подача