Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи данных.

Целью изобретения является повышение диагностической способности устройства.

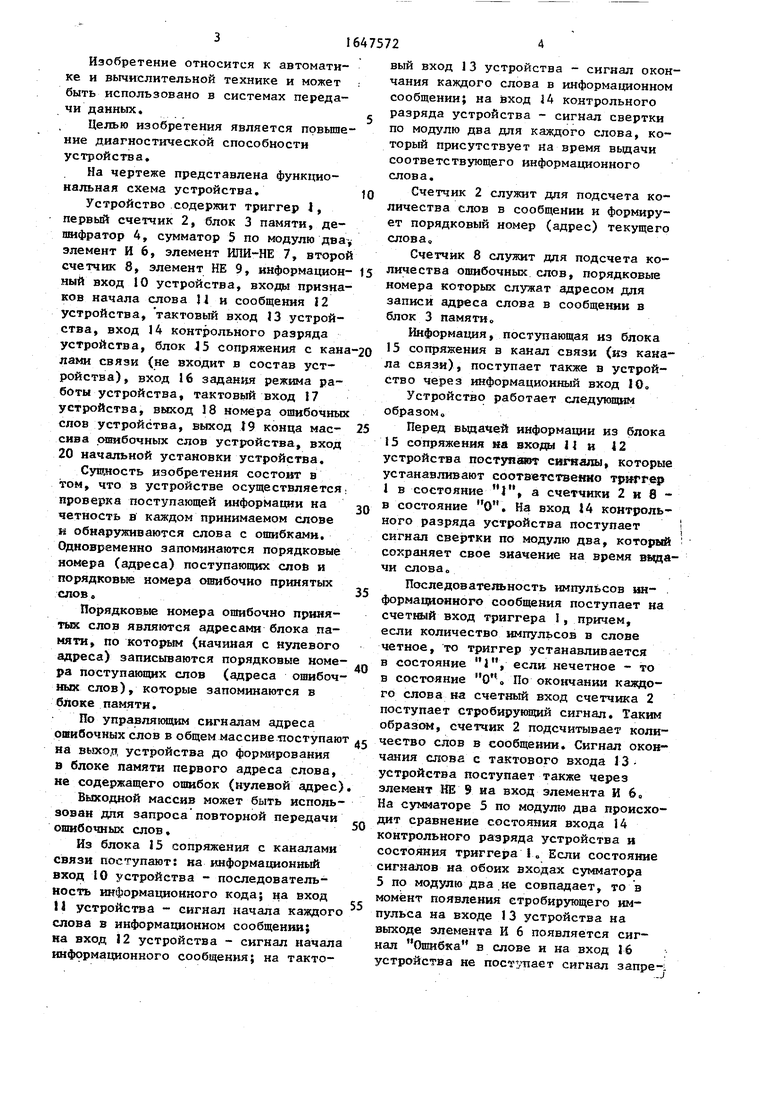

На чертеже представлена функциональная схема устройства.

Устройство содержит триггер I, первый счетчик 2, блок 3 памяти, де- пшфратор 4, сумматор 5 по модулю два-, элемент И 6, элемент ИЛИ-НЕ 7, второй счетчик 8, элемент НЕ 9, информацией- ный вход 10 устройства, входы признаков начала слова 11 и сообщения 12 устройства, тактовый вход 13 устройства, вход 14 контрольного разряда устройства, блок 45 сопряжения с кана лами связи (не входит в состав устройства), вход 16 задания режима работы устройства, тактовый вход 17 устройства, выход 18 номера ошибочных слов устройства, выход 19 конца мае- сива ошибочных слов устройства, вход 20 начальной установки устройства.

Сущность изобретения состоит в том, что в устройстве осуществляется проверка поступающей информации на четность в каждом принимаемом слове к обнаруживаются слова с ошибками. Одновременно запоминаются порядковые номера (адреса) поступающих слов и порядковые номера ошибочно принятых слов

Порядковые номера ошибочно принятых слов являются адресами блока памяти, по которым (начиная с нулевого адреса) записываются порядковые номе- pa поступающих слов (адреса ошибочных слов), которые запоминаются в блоке памяти.

По управляющим сигналам адреса ошибочных слов в общем массиве поступают на вьжод устройства до формирования в блоке памяти первого адреса слова, не содержащего ошибок (нулевой адрес)

Выходной массив может быть использован для запроса повторной передачи ошибочных слов.

Из блока 15 сопряжения с каналами связи поступают: на информационный вход 10 устройства - последовательность информационного кода; на вход 11 устройства - сигнал начала каждого слова в информационном сообщении; на вход 12 устройства - сигнал начала информационного сообщения; на такто

5 0 5

о

.Q

с

5

0

5

вый вход 13 устройства - сигнал окончания каждого слова в информационном сообщении; на вход 14 контрольного разряда устройства - сигнал свертки по модулю два для каждого слова, который присутствует на время выдачи соответствующего информационного слова.

Счетчик 2 служит для подсчета количества слов в сообщении и формирует порядковый номер (адрес) текущего слова.

Счетчик 8 служит для подсчета количества ошибочных слов, порядковые номера которых служат адресом для записи адреса слова в сообщении в блок 3 памятио

Информация, поступающая из блока 15 сопряжения в канал связи (из канала связи), поступает также в устройство через информационный вход 10

Устройство работает следующим образом.,

Перед выдачей информации из блока 15 сопряжения на входы Ли 12 устройства поступают сигналы, которые устанавливают соответственно триггер 1 в состояние 1, а счетчики 2 и 8 - в состояние О. На вход 14 контрольного разряда устройства поступает сигнал свертки по модулю два, который сохраняет свое значение на время ввада- чи слова.

Последовательность импульсов информационного сообщения поступает на счетный вход триггера I, причем, если количество импульсов в слове четное, то триггер устанавливается в состояние 1, если нечетное - то в состояние О По окончании каждого слова на счетный вход счетчика 2 поступает стробирующий сигнал. Таким образом, счетчик 2 подсчитывает количество слов в сообщении. Сигнал окончания слова с тактового входа 13 - устройства поступает также через элемент НЕ 9 на вход элемента И 6„ На сумматоре 5 по модулю два происходит сравнение состояния входа 14 контрольного разряда устройства и состояния триггера 1„ Если состояние сигналов на обоих входах сумматора 5 по модулю два не совпадает, то в момент появления стробирующего импульса на входе 13 устройства на выходе элемента И 6 появляется сигнал Ошибка в слове и на вход 16 устройства не поступает сигнал запре-.

та записи блока памяти. Сигналом Ошибка в блок 3 памяти записывается адрес (номер) слова, в котором обнаружена ошибка Одновременно счетчик 8 считает количество слов, в которых содержались ошибки, и формируют адрес для блока 3 памяти, по которому записывается номер ошибочного слова. Задним фронтом импульса ошибки счетчик 8 подготавливает новый адрес, по которому будет записан очередной номер ошибочного слова„ Таким образом, счетчик 2 формирует

10

мер, по обратному каналу на передающую сторону для повторной их передачи.

Формула изобретения

Устройство для контроля последовательного кода, содержащее триггер, первый счетчик и дешифратор, причем единичный вход триггера и установочный вход первого счетчика являются соответственно входами признака начала слова и признака начала сообщения

порядковые номера слов (адреса слов), устройства, счетный вход триггера которые при наличии ошибки будут запи- является информационным входом устрой

мер, по обратному каналу на передающую сторону для повторной их передачи.

Формула изобретения

Устройство для контроля последовательного кода, содержащее триггер, первый счетчик и дешифратор, причем единичный вход триггера и установочный вход первого счетчика являются соответственно входами признака начала слова и признака начала сообщения

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения дискретных датчиков с электронной вычислительной машиной | 1982 |

|

SU1024898A2 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1399761A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для ввода информации | 1984 |

|

SU1251056A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи данных. Цель изобретения - повышение диагностической способности устройства. Устройство содержит триггер 1, счетчики 2, 8, блок 3 памяти, дешифратор 4, сумматор 5 по модулю два, элемент И 6, элемент ИЛИ-НЕ 7 и элемент НЕ 9. В устройстве осуществляется проверка поступающей информации на четность в каждом слове. Ведется подсчет принятых слов на счетчике 2. При обнаружении ошибки в принятом слове номер ошибочного слова переписывается в блок 3 памяти по адресу, формируемому счетчиком 8, который подсчитывает число ошибочных слов. По окончании приема информации счетчик 8 обнуляется и начинается считывание из блока 3 памяти номеров ошибочных слов, пока не появляется сигнал на выходе дешифратора 4 нулевой комбинации. 1 ил. (Л

саны в блок 3 памяти по адресам, указанным счетчиком 8. Первое ошибочное слово будет записано по нулевому ад-

ресу, следующее - по первому и т„д.

После окончания передачи информации на вход 16 устройства подается сигнал запрета записи блока 3 памяти и сигнал сброса с входа 20 устройства на сброс счетчика 8 Если по нулевому адресу блока 3 памяти не записан ад- рее слова с ошибкой, то дешифратор 4 сформирует на выходе 19 устройства сигнал Конец массива ошибочных слов Если по нулевому адресу блока 3 памяти записан адрес слова с ошибкой, то этот адрес появляется на выходе 48 номера ошибочных слов устройства. Затем, при появлении на входе 17 устройства сигналов считывания адреса ошибочных слов, счетчик 8 каждым импульсом с входа 17 устройства будет увеличиваться на I, т.е. по первому адресу блока 3 памяти появляется адрес следующего слова с ошибкой и т.д.,- пока на выходе дешифратора 4

не будет сформирован сигнал конца массива ошибочных слов (по наличию на входах дешифратора 4 всех нулей).

Устройство может работать как на передаче, так и на приеме.

В первом случае после передачи пакета информации начинают передаваться номера (адреса) ошибочных слов для повторенияэтих слов. Во втором случае на приеме формируются адреса - слов, принятых с ошибками, и информация об этих словах передается, напри

ства, счетный вход первого счетчика является первым тактовым входом устройства, отличающееся тем, что, с целью повышения диагностической способности устройства, в него введены второй счетчик, блок памяти, сумматор по модулю два, элемент И, элемент НЕ и элемент ИЛИ-НЕ,

причем первый вход сумматора по модулю два является входом контрольного разряда устройства, прямой выход триггера соединен с вторым входом сумматора по модулю два, выход которого соединен с первым входом элемента И, выход которого соединен с входом записи-чтения блока памяти и первым входом элемента ИЛИ-НЕ, выход которого соединен со счетным входом второго счетчика, информационный выход которого соединен с адресным входом блока памяти, информационный выход которого является выходом номера ошибочных слов устройства и соединен

с информационным входом дешифратора, нулевой выход которого является выходом конца массива ошибочных слов устройства, тактовый вход устройства через элемент НЕ подключен к второму

входу элемента.И, третий вход которого является входом задания режима работы устройства, первый и второй установочные входы второго счетчика подключены соответственно к входу признака начала сообщения и входу начальной установки устройства, второй вход элемента ИЛИ-НЕ подключен к тактовому входу устройства.

| Устройство для контроля параллельного двоичного кода на четность | 1974 |

|

SU530332A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1991-05-07—Публикация

1989-05-22—Подача