1

(21)4694276/21

(22) 30.03.89

(-16)07.05.91. Бюл. № 17

(7)А.Л.Круглов, В.Е.Петров и Г.Е.Максимов

(53)821.374(088.8)

(56)Авторское свидетельство СССР № 1441467, кл. НОЗ КЗ/64. 25.08.86.

Олтикозлектронные методы обработки изображения./Под ред. проф. С.Б.Гуревича. Л.: Наука, Лен.отд., 1982, с.153.

(54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ УПРАВЛЕНИЯ

(57)Изобретение относится к импульсной технике и может быть использовано для управления прибором с зарядной связью,

Цель изобретения - расширение функциональных возможностей путем регулирования длительности импульса накопления с помощью цифрового кода с одновременным повышением быстродействия за счет получения параллельного формирования управляющих импульсов и импульса накопления - достигается за счет введения буферного каскада 9, триггеров 11. 12, 13, 14, инвертора 10, элемента ИЛИ 15, элементов И 16, 17, 18, 19, 20, формирователя 21 фаз, формирователя 22 импульсов, кодовых шин 26, 27 и организации новых функциональных связей. Устройство также содержит генератор 1 импульсов, счетчики 2, 3, 4 импульсов, буферные каскады 5, 6, 7, 8. выходные шины 23, 24, 25, 28, 29. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по длительности | 1983 |

|

SU1150746A1 |

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| Устройство для передачи геофизической информации | 1987 |

|

SU1564579A1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1988 |

|

SU1541622A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Цифровой фазометр | 1988 |

|

SU1511706A1 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

28

23 -

М 25

ON

Тн 23

Изобретение относится к импульсной технике и может быть использовано для управления прибором с зарядной связью (ПЗС), в котором необходимо изменять длительность импульса накопления с помощью цифрового кода.

Цель изобретения - расширение фу: циональных возможностей путем регулирования длительности импульса накопления с помощью цифрового кода с одновременным повышением быстродействия за счет полунения параллельного формирования управляющих импульсов и импульса накопления, повышение быстродействия.

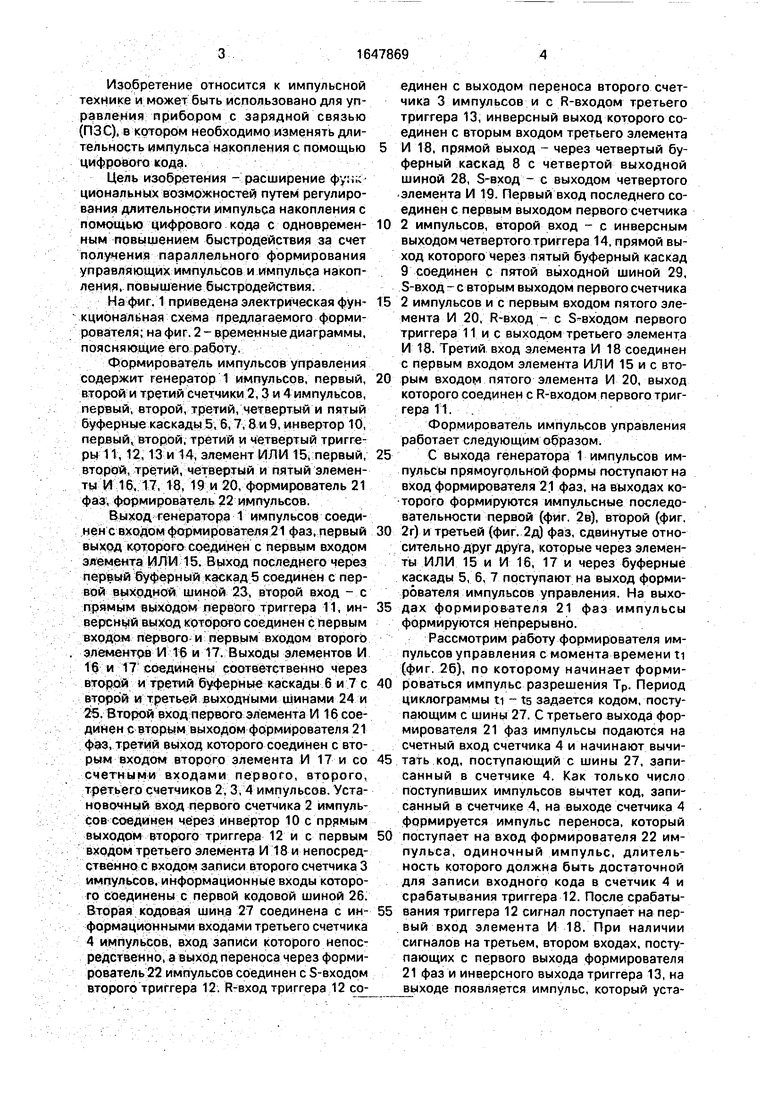

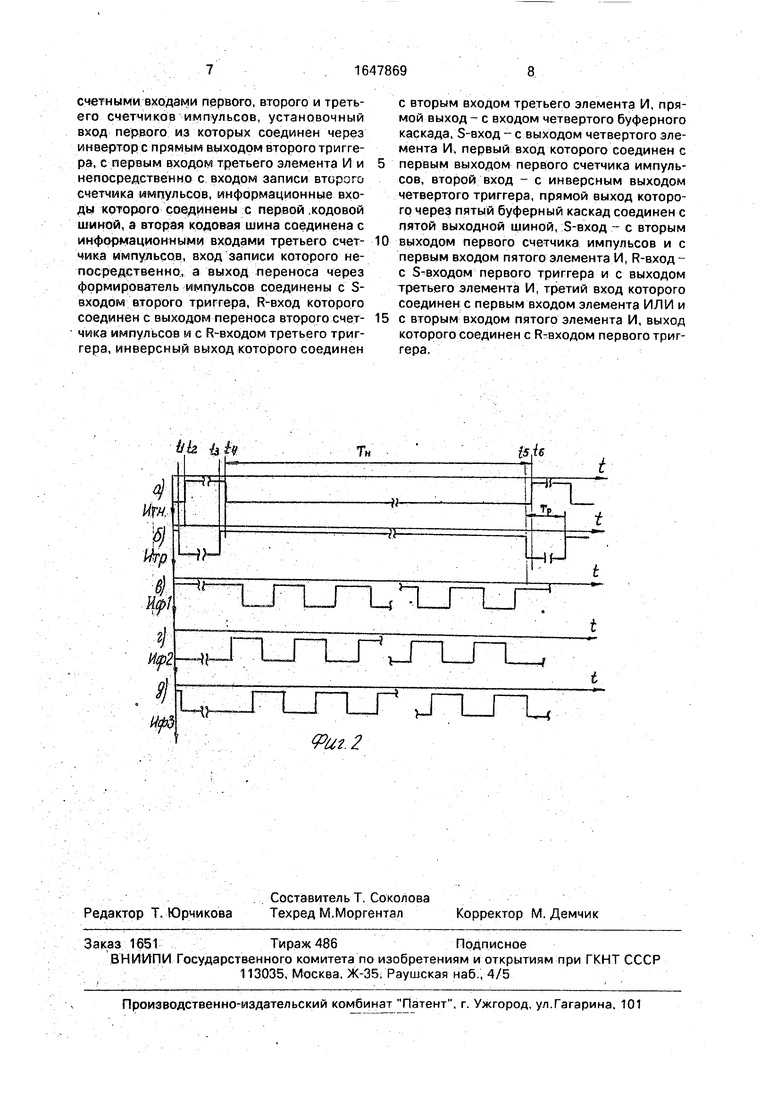

На фмг. 1 приведена электрическая функциональная схема предлагаемого формирователя; на фиг. 2 - временные диаграммы, поясняющие его работу,

Формирователь импульсов управления содержит генератор 1 импульсов, первый, второй и третий счетчики 2,3 и 4 импульсов, первый, второй, третий, четвертым и пятый буферные каскады 5, б, 7,8 и 9, инвертор 10, первыйг второй, третий и четвертый триггеры 11,12,13 и 14, элемент ИЛИ 15, первый, второй, третий, четвертый и пятый элементы И 16. 17, 18, 19 и 20, формирователь 21 фаз, формирователь 22 импульсов.

Выход генератора 1 импульсов соединен с входом формирователя 21 фаз, первый выход которого соединен с первым входом элемента ИЛИ 15. Выход последнего через первый буферный каскад 5 соединен с первой выходной шиной 23, второй вход - с прямым выходом первого триггера 11, инверсный выход которого соединен с первым входом первого и первым входом второго элементов И 16 и 17. Выходы элементов И 16 и 17 соединены соответственно через второй и третий буферные каскады 6 и 7 с второй и третьей выходными шинами 24 и 25, Второй вход первого элемента И 16 соединен с вторым выходом формирователя 21 фаз, третий выход которого соединен с вторым входом второго элемента И 17 и со счетными входами первого, второго, третьего счетчиков 2,3,4 импульсов. Установочный вход первого счетчика 2 импульсов соединен через инвертор 10с прямым выходом второго триггера 12 и с первым входом третьего элемента И 18 и непосредственно с входом записи второго счетчика 3 импульсов, информационные входы которого соединены с первой кодовой шиной 26. Вторая кодовая шина 27 соединена с информационными входами третьего счетчика 4 импульсов, вход записи которого непосредственно, а выход переноса через формирователь 22 импульсов соединен с S-входом второго триггера 12. R-вход триггера 12 соединен с выходом переноса второго счетчика 3 импульсов и с R-входом третьего триггера 13, инверсный выход которого соединен с вторым входом третьего элемента

И 18, прямой выход - через четвертый буферный каскад 8 с четвертой выходной шиной 28, S-вход - с выходом четвертого элемента И 19. Первый вход последнего соединен с первым выходом первого счетчика

0 2 импульсов, второй вход - с инверсным выходом четвертого триггера 14, прямой выход которого через пятый буферный каскад 9 соединен с пятой выходной шиной 29, S-вход - с вторым выходом первого счетчика

5 2 импульсов и с первым входом пятого элемента И 20, R-вход - с S-входом первого триггера 11 и с выходом третьего элемента И 18. Третий вход элемента И 18 соединен с первым входом элемента ИЛИ 15 и с вто0 рым входом пятого элемента И 20, выход которого соединен с R-входом первого триггера 11.

Формирователь импульсов управления работает следующим образом.

5 С выхода генератора 1 импульсов импульсы прямоугольной формы поступают на вход формирователя 21 фаз, на выходах которого формируются импульсные последовательности первой (фиг, 2в), второй (фиг.

0 2г) и третьей (фиг. 2д) фаз, сдвинутые относительно друг друга, которые через элементы ИЛИ 15 и И 16, 17 и через буферные каскады 5, 6, 7 поступают на выход формирователя импульсов управления. На выхо5 дах формирователя 21 фаз импульсы формируются непрерывно.

Рассмотрим работу формирователя импульсов управления с момента времени ti (фиг. 26), по которому начинает форми0 роваться импульс разрешения Тр. Период циклограммы ti - ts задается кодом, поступающим с шины 27. С третьего выхода формирователя 21 фаз импульсы подаются на счетный вход счетчика 4 и начинают вычи5 тать код, поступающий с шины 27, записанный в счетчике 4. Как только число поступивших импульсов вычтет код, записанный в счетчике 4, на выходе счетчика 4 формируется импульс переноса, который

0 поступает на вход формирователя 22 импульса, одиночный импульс, длительность которого должна быть достаточной для записи входного кода в счетчик 4 и срабатывания триггера 12. После срабаты5 вания триггера 12 сигнал поступает на первый вход элемента И 18. При наличии сигналов на третьем, втором входах, поступающих с первого выхода формирователя 21 фаз и инверсного выхода триггера 13, на выходе появляется импульс, который устанавливает триггер 11 в состояние 1 на прямом выходе и О на инверсном. Сигнал 1м поступает на второй вход элемента ИЛИ 15, установив на его выходе 1, а сигнал О - на вторые входы элементов И 16, 17, устанавливая их выходы в состояние О, тем самым заканчивается формирование последовательности выходных фазных импульсов. На первом выходе формирователя импульсов управления устанавливается высокий уровень напряжения, а на втором и третьем выходах - низкий уровень. Одновременно по R-входу триггер 14 устанавливается в состояние О и через буферный каскад 9 сигнал поступает на шину 29, что является началом формирования импульса разрешения Тр ПЗС (момент времени ti на фиг. 26), Одновременно по наличию сигнала 1 на выходе триггера 12 через инвертор 10 дается разрешение на работу счетчиков 3 и 2. При этом импульсы, поступившие с третьего выхода формирователя 21 фаз, начинают вычитать код, записанный в счетчике 3 с шины 26, а счетчик 2 начинает считать поступившие импульсы,

Сигнал с первого выхода счетчика 2 определяет время ti - ta, данный выход может быть подключен к одному из младших разрядов счетчика в зависимости от необходимого времени ti - 12. Сигнал Г на первом выходе счетчика 2 через первый вход элемента И 19 лри наличии сиг нала Г, появившимся по ti на втором входе элемента И 19, устанавливает триггер 13, его прямой выход в состояние 1, тем самым заканчивается формирование импульса накопления Тн, который через четвертый буферный каскад 8 поступает на шину 28 (фиг. 2а, б). Через время t2 - 1з (фиг. 2а, б) на втором выходе счетчика 2 появляется сигнал 1, который устанавливает триггер 14 в состояние 1, тем самым заканчивается формирование импульса разрешения Тр, равного ti - 13 (фиг. 26). Одновременно сигнал со счетчика 2 поступает на первый вход элемента И 20 и при наличии сигнала с первого выхода формирователя 21 фаз на его выходе формируется сигнал, устанавливающий триггер 11 в состояние О, тем самым дается разрешение на прохождение фазных импульсов с первого, второго и третьего выходов формирователя 21 фаз на выходные шины формирователя импульсов управления.

После считывания кода со счетчика 3 импульсами, поступающими на его счетный вход, на выходе переноса счетчика 3 появляется сигнал, который устанавливает триггер 13 в состояние О, и тем самым начинает формироваться импульс накопления Тн в момент времени т.4 (фиг. 2а). Одновременно триггер 12 устанавливается в состояние О и через инвертор 10 записывается код в счетчик 3, поступающий с шины 26, при этом запрещается прием импульсов

5 счетчиком 3 и счетчик 2 сбрасывается в исходное состояние. Счетчики 2, 3 находятся в установленном исходном состоянии, пока на выходе счетчика 4 не появится им- пульс переноса и сработает триггер 12. Да10 лее процесс повторяется.

Буферные каскады 5.6,7, 8, 9 позволяют логические импульсы положительной полярности преобразовать в импульсы с параметрами, обеспечивающими нормальную

15 работу ПЗС. С помощью кода, поступающего с шины 27 в счетчик 4, можно изменять период всей циклограммы ti - ts (фиг. 26), а значит, регулировать длительность импульса накопления м - те (фиг. 2а). При

0 необходимости сохранения частоты строк

с - т длительность импульса накоплеЧэ I

ния Тн можно регулировать поступающим кодом с шины 26 и счетчиком 3, которые 5 позволяют изменять начало импульса накопления, т.е. регулировать время з - 14. Длительность импульса разрешения в обоих случаях остается постоянной, равной ti -13.

0 Формула изобретения

Формирователь импульсов управления, содержащий генератор импульсов, первый, второй, третий счетчики импульсов, первый, второй, третий, четвертый буферные каска5 ды, выходы которых соединены с соответствующими выходными шинами, пятую выходную шину, отличающийся тем, что, с целью расширения функциональных возможностей с одновременным повыше0 нием быстродействия, в него введены пятый буферный каскад, первый, второй, третий, четвёртый триггеры, инвертор, элемент ИЛИ, первый,второй,третий,четвертый,пятый элементы И,формирователь фаз .формирователь импуль5 сов.первэя и вторая кодовые шины, причем выход генератора импульсов соединен с входом формирователя фаз, первый выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с входом первого

0 буферного каскада, второй вход - с прямым выходом первого триггера, инверсный выход которого соединен с первым входом первого и первым входом второго элементов И, выходы которых соединены соответствен 5 но с входами второго и третьего буферных каскадов, а второй вход первого элемента И соединен с вторым выходом формирователя фаз, третий выход которого соединен с вторым входом второго элемента И и со

счетными входами первого, второго и третьего счетчиков импульсов, установочный вход первого из которых соединен через инвертор с прямым выходом второго триггера, с первым входом третьего элемента И и непосредственно с входом записи второго счетчика импульсов, информационные входы которого соединены с первой .кодовой шиной, а вторая кодовая шина соединена с информационными входами третьего счетчика импульсов, вход записи которого непосредственно, а выход переноса через формирователь импульсов соединены с S- входом второго триггера, Я -вход которого соединен с выходом переноса второго счетчика импульсов и с R-входом третьего триггера, инверсный выход которого соединен

0

5

с вторым входом третьего элемента И, прямой выход- с входом четвертого буферного каскада, S-вход - с выходом четвертого элемента И, первый вход которого соединен с первым выходом первого счетчика импульсов, второй вход - с инверсным выходом четвертого триггера, прямой выход которого через пятый буферный каскад соединен с пятой выходной шиной, S-вход - с вторым выходом первого счетчика импульсов и с первым входом пятого элемента И, R-вход - с S-входом первого триггера и с выходом третьего элемента И, третий вход которого соединен с первым входом элемента ИЛИ и с вторым входом пятого элемента И, выход которого соединен с R-входом первого триггера.

Авторы

Даты

1991-05-07—Публикация

1989-03-30—Подача