Изобретение относится к вычислительной технике и может быть использовано для построения оперативных запоминающих устройств.

Цель изобретения - повышение быстродействия.

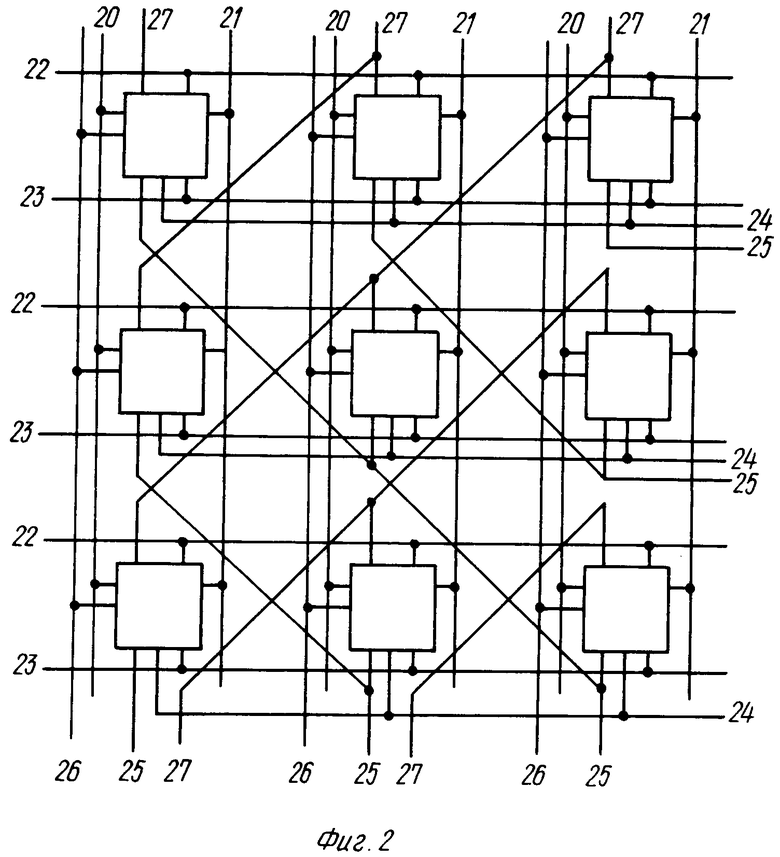

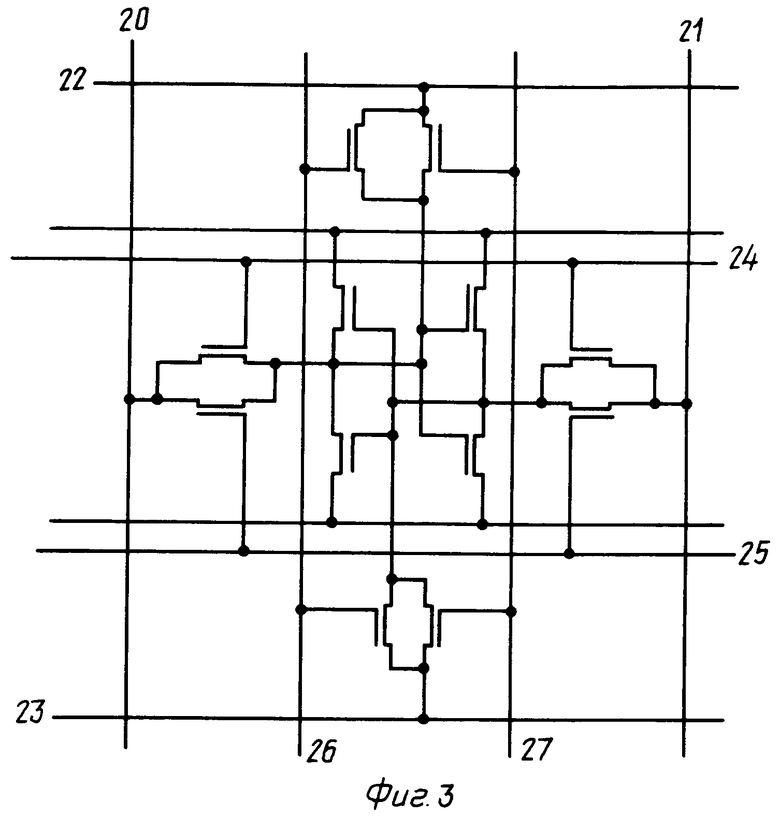

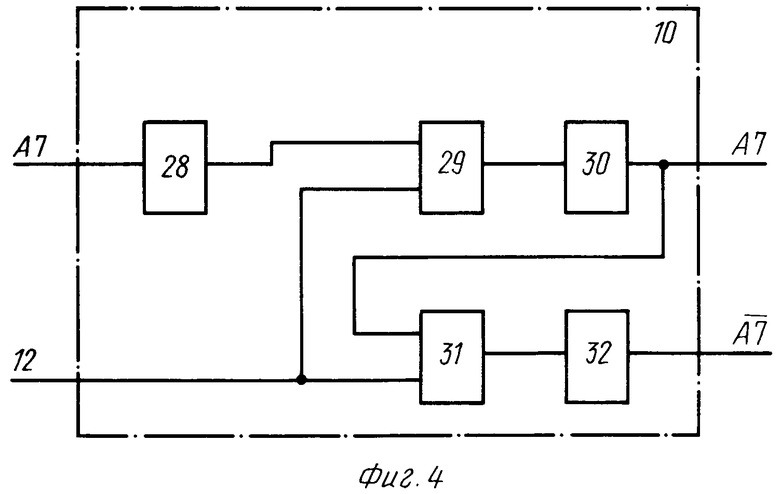

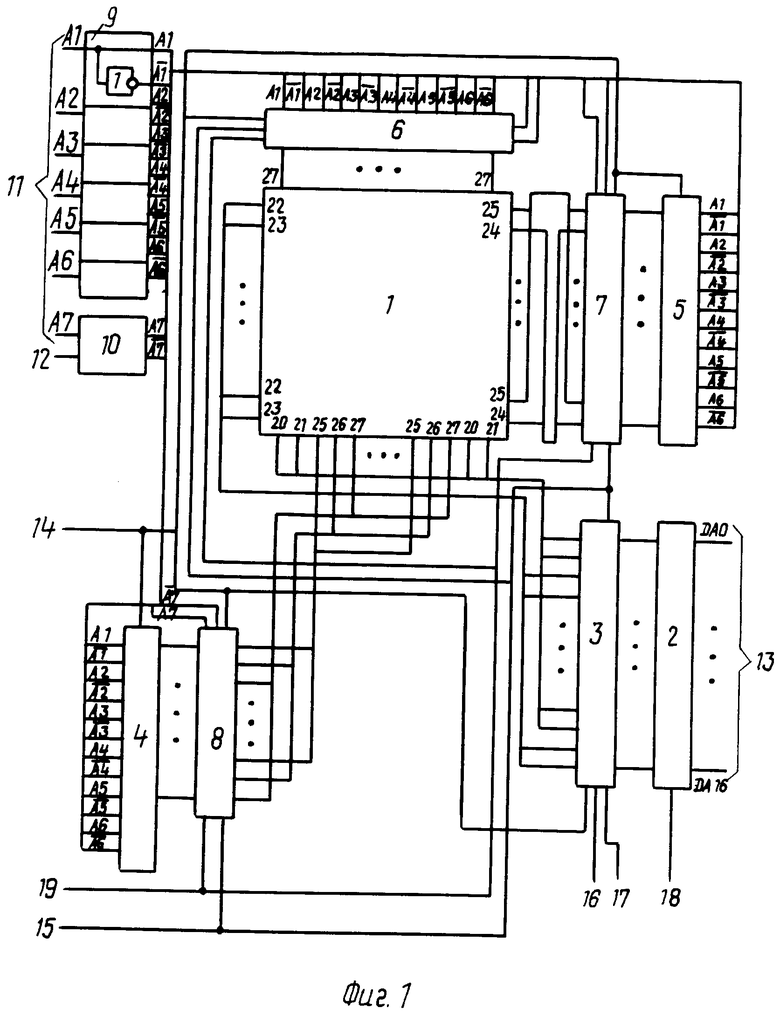

На фиг. 1 приведена функциональная схема запоминающего устройства; на фиг. 2 - схема фрагмента блока памяти; на фиг.3 - схема элемента памяти; на фиг.4 - схема блока управления.

На фиг. 1-4 приняты следующие обозначения: блок 1 памяти, усилитель 2 записи-считывания, коммутатор 3 данных, первый 4, второй 5 и третий 6 дешифраторы, первый 7 и второй 8 коммутаторы адреса, блок 9 инверторов, блок 10 управления, адресные входы 11, вход 12 задания работы с полными диагоналями, информационные входы-выходы 13, вход 14 разрешения выборки устройства, вход 15 задания режима работы по строкам или столбцам, первый 16 и второй 17 входы выбора фрагмента блока памяти устройства, вход 18 управления записи-считывания устройства, вход 19 задания режима, входы прямых 20 и инверсных 21 данных столбцов блока памяти, входы прямых 22 и инверсных 23 данных строк блока памяти, входы 24 выборки строк блока памяти, входы 25 выборки диагоналей первой группы блока памяти, входы 26 выборки столбцов блока памяти, входы 27 выборки диагоналей второй группы блока памяти, элемент НЕ 28, элемент ИЛИ-НЕ 29, элемент НЕ 30, элемент ИЛИ-НЕ 31, элемент НЕ 32.

Запоминающее устройство работает следующим образом. В режиме хранения уровень напряжения на входе 14 устройства имеет низкий уровень, уровень напряжения на остальных внешних входах значения не имеет. Низкий логический уровень на входе 14 запрещает работу дешифраторов 4, 5 и 6 и коммутаторов 3, 7 и 8. Таким образом, на выходах дешифраторов 4, 5 и 6 и коммутаторов 7 и 8 имеется низкий логический уровень и входы 24, 25, 26 и 27 находятся под его действием, следовательно, транзисторы связи в элементах, подключенные к этим входам, закрыты.

При обращении к запоминающему устройству на адресных входах 11 выставляется адрес, на информационных входах 13 выставляются данные, на вход 12 подаются низкий логический уровень, если работы производится с неполными диагоналями, и высокий логический уровень при работе с полными диагоналями, на входе 15 выставляются низкий логический уровень, если запись-считывание происходит по прямым и инверсным входам 22 и 23 данных строк, высокий логический уровень, если запись-считывание происходит по прямым и инверсным входам 20 и 21 данных столбцов соответственно, на входе 19 устанавливаются высокий логический уровень, если обращение будет к входам 25 выборки диагоналей первой группы или входам 27 выборки диагоналей второй группы, и низкий логический уровень, если обращение будет к входам 26 выборки столбцов или входам 24 выборки строк.

На входы 16 и 17 в двоичном коде задается адрес фрагмента: по столбцам 16х64, где 16 - количество элементов памяти по вертикали матрицы накопителя; 64 - количество элементов памяти по горизонтали матрицы накопителя; по строкам 16х64, где 16 - количество элементов памяти по горизонтали матрицы накопителя; 64 - количество элементов памяти по вертикали матрицы накопителя. На вход 18 подаются низкий логический уровень при записи информации и высокий логический уровень при чтении информации. После того, как управляющие сигналы, данные и адрес выставлены подается высокий логический уровень на вход 14, и происходит обращение к устройству.

Число диагоналей в накопителе определяется по следующей формуле

(n + m) -1 = K где n - число элементов памяти по строкам;

m - число элементов памяти по столбцам;

К - число диагоналей, при матрице 64х64 число диагоналей одной группы равно 127, дешифратор 6 дешифрирует диагонали (1-64) второй группы, дешифратор 4 и коммутатор 8 выбирают столбцы (1-64), диагонали (1-64) первой группы и диагонали (65-127) второй группы, дешифратор 5 и коммутатор 7 выбирают строки (1-64) и диагонали (65-127) первой группы при нулевом уровне напряжения на входе 12. Все дешифраторы работают раздельно, происходит выборка неполных диагоналей.

При высоком уровне напряжения на входе 12 на выходах блока управления имеются высокие логические уровни, что приводит к одновременной работе дешифраторов 4 и 5 и коммутаторов 7 и 8. Таким образом, происходит одновременная выборка диагоналей первой группы (1-64) и их дополнений (65-127) или одновременной работе дешифраторов 4 и 6 и коммутатора 8. Таким образом, происходит одновременная выборка диагоналей второй группы (1-64) и их дополнений (65-127).

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2025796C1 |

| Ассоциативное запоминающее устройство | 1991 |

|

SU1833917A1 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| Запоминающее устройство с обнаружением отказавших блоков | 1980 |

|

SU903974A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения оперативных запоминающих устройств. Цель изобретения - повышение быстродействия. Запоминающее устройство содержит блок 1 памяти, усилитель 2 записи-считывания, коммутатор 3 данных, дешифраторы 4-6, коммутаторы 7-8 адреса, блок 9 инверторов, блок 10 управления, адресные входы 11, управляющие входы 12, 14-19, информационные входы-выходы 13. В устройстве обращение к полным диагоналям возможно за один такт, следовательно, время обращения при работе с полными диагоналями сокращается вдвое. 4 ил.

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блок памяти, усилитель записи-считывания, первый и второй дешифраторы, первый и второй коммутаторы адреса, коммутатор данных, информационные входы усилителя записи-считывания являются информационными входами устройства, вход выборки усилителя записи-считывания является входом записи считывания устройства, информационные входы коммутатора данных соединены с соответствующими выходами усилителя записи-считывания, выходы первой группы коммутатора данных соединены с соответствующими входами прямых и инверсных данных строк блока памяти, выходы второй группы коммутатора данных соединены с соответствующими входами прямых и инверсных данных столбцов блока памяти, информационные входы первого и второго коммутаторов адреса соединены с выходами соответственно первого и второго дешифраторов, выходы первой группы первого коммутатора адреса соединены с соответствующими входами выборки строк блока памяти, выходы второй группы первого коммутатора адреса соединены с соответствующими входами выборки диагоналей первой группы блока памяти, выходы первой группы второго коммутатора адреса соединены с соответствующими входами выборки столбцов блока памяти, выходы второй группы второго коммутатора адреса соединены с соответствующими входами выборки диагоналей второй группы блока памяти, входы управления первого и второго дешифраторов объединены и являются входом разрешения выборки устройства, первые входы управления первого и второго коммутаторов адреса объединены и являются входом задания режима устройства, первый и второй управляющие входы коммутатора данных являются соответственно первым и вторым входами выбора фрагмента блока памяти устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены третий дешифратор, блок инверторов, блок управления, первый вход задания режима которого является адресным входом устройства, входы инверторов являются адресными входами группы устройства, прямые и инверсные выходы блока инверторов соединены с соответствующими входами первого, второго и третьего дешифраторов, первый и второй выходы блока управления соединены соответственно с вторым и третьим управляющими входами первого и второго коммутаторов адреса и с адресными входами третьего дешифратора, второй вход задания режима блока управления является входом задания режима работы с полными диагоналями устройства, вход задания режима устройства соединен с вторым входом управления третьего дешифратора, вход разрешения выборки устройства соединен с третьим входом управления третьего дешифратора, с третьим входом управления коммутатора данных, четвертыми входами управления первого и второго коммутаторов адреса, выходы третьей группы второго коммутатора адреса соединены с соответствующими входами выборки диагоналей первой группы блока памяти, выходы третьего дешифратора соединены с соответствующими входами выборки диагоналей второй группы блока памяти, пятый управляющий вход второго коммутатора адреса соединен с пятым управляющим входом первого коммутатора адреса, четвертым управляющим входом коммутатора данных, четвертым управляющим входом третьего дешифратора и является входом задания режима работы по строкам или столбцам устройства.

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-12-30—Публикация

1989-03-30—Подача