(54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ

«ЖБОНАЧЧИЕВО-ДЕСЯТИЧНЫХ КОДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| КОМБИНАЦИОННЫЙ СУММАТОР СТРУКТУРНЫХ КОДОВ | 1991 |

|

RU2023288C1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Устройство для сложения п-разрядных десятичных чисел | 1980 |

|

SU900282A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

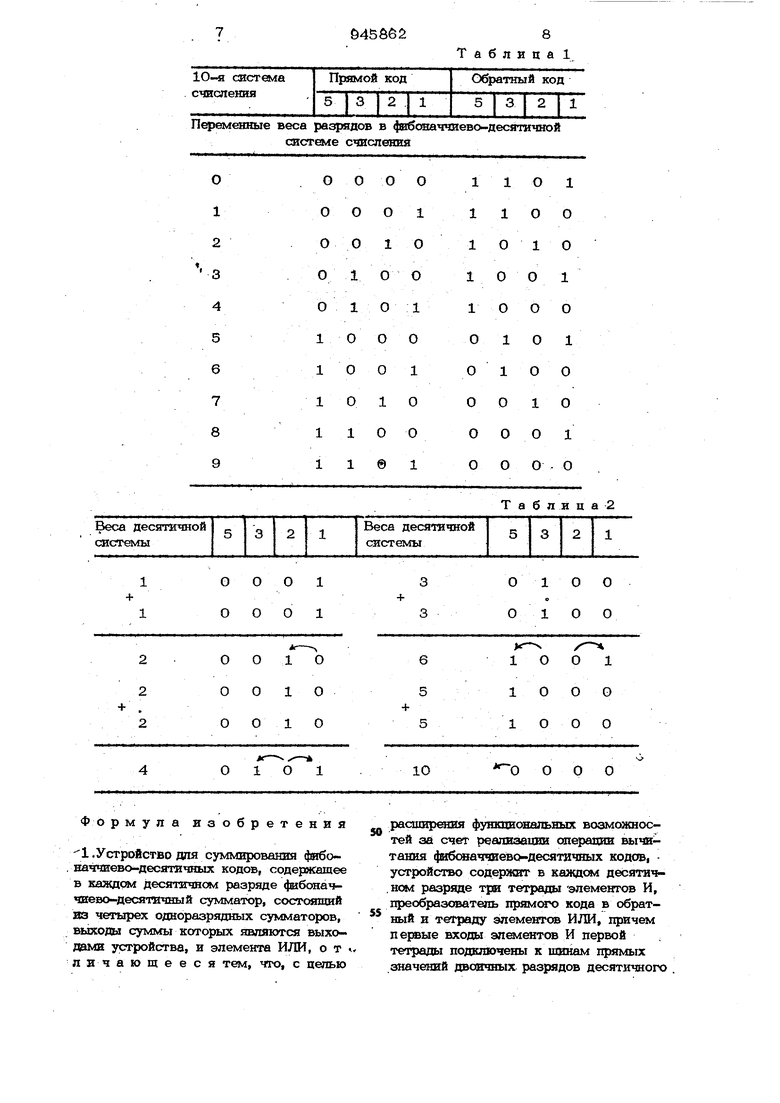

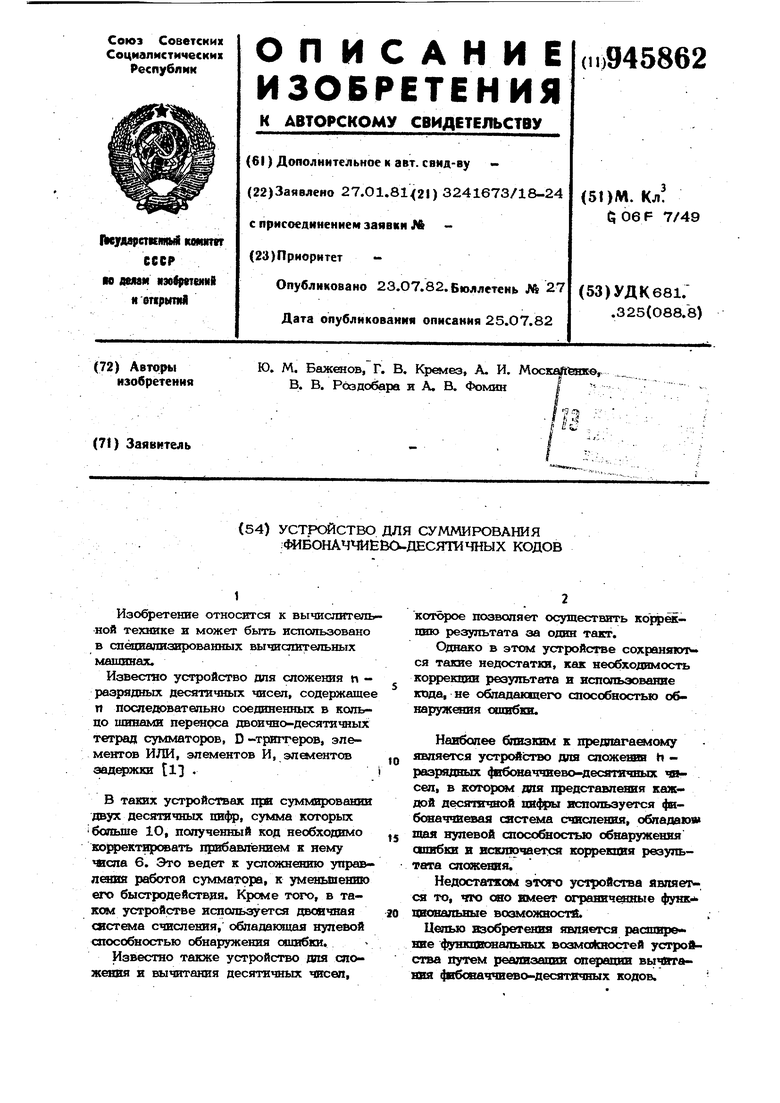

Изобретение относится к вычиспятелы ной технике и может быть использовано в спёциапизврованных вычислительных машинах. Известно устройство для сложения п разрядных десятичных чисел, содержаще п последовательно соединенных в кольцо шинами переноса двоично-десятичных тетрад сумматоров, D -триггеров, элементов ИЛИ, элементов И, элементов задержки В таких устройствак при суммировании двух десятичных пвфр, сумма которых больше 1О, полученный код необходимо конректщровать прибавяениетл к нему часла 6. Это ведет к усложнению управления работой сумматора, к уменьшению его быстродействия. Кроме того, в таком устройстве используется двсячная сястема счисления, обладаклцая нулевой способностью обнаружения сшибки. Известно также устройство для сложения и вычитания десятичных чисел. позволяет осуществить ко ррекдию результата за ощга такт. Однако в этом устройстве сохраняю ся такие недостатки, как необходимость коррекции результата и использование кода, не обладающего способностью обнаружения ошибки. Наиболее близким к предлагаемому является устрЫ1ство для сложешв И разрядных 4вбоначчиево-десятичных чвсел, в KCffOpoM цпя 1федставления каждой десятичной пи4|ры используется фибсяаччиевая сястема счисления, обладают тая нулевой способностью обнаружения сшибки и ясключается коррекция результата сложения. Недостатком этого усоройства является то, ягго 08О вмеет ограниченные функцвональные возможности. Целью изобретения является расшнре ние фунющсшальных возмо оюстей устройства путем реалвзацихс операпив вычвтания фабсвач:чиево-десятячных кодов. Поставленная цеяь достигается тем, что устройство для сукшшрования фибона чиево-десятичных кодов, содержащее в каждом десятичном разряде фибоначчиево десятичный сумматор, состоящий из четырех одноразрядных сумматоров, выходы суммы которых 5голяются выходами устройства и элемента ИЛИ, содержит в каждом десятичном разряде три тетрады элементов И, преобразователь прямого кода в обратный и тетраду элементов ИЛИ, причем первые входы элементов И первой тетрады подключены к шинам пря мых значений двоичных разрядов десятичного разряда первого операнда устройства, вторые входы элементов И первой тетрада подключены к управляющем входу приема в прямом коде первого операнда устройства, а выходы элементов И первой тетрады подключены к соответствующим первым входам однораз рядных сумматоров, первые входы элементов И второй тетрады подключены к шинам прямых значений двоичных разрядов деся-Лчного разряда второго oneранда устройства, вторые входы элементов И второй тетрады подключены к управляющему входу приема в прямом, коде второгю операнда устройства, первый вход преобразователя прямого кода в обратный подключен к шине инверсного значения первого двоичного разряда десятичного разряда второго операнда устройства, второй и третий входы преобразователя прямого кода в обратный подключень к шине инверсного значения второго двоичного разряда десятичного разряда второго операнда устройства, четвертый вход преобразователя прямого кода в обратный подключен к 1шше инвер ного значения третьего двоичного разряда десятичного разряда второго операн да устройства, первый вход первого элемента И третьей тетрады подключен к первому выходу преобразователя прямого кода в обратный, первый вход второго элемента И третьей тетрады соединен с первым входом второго элемента И второй т.етрады, первый вход третьего элемента И третьей тетрады подключен к второму выходу преобразователя прямого кода в обратный, первый вход четвертог элемента И третьей тетрады подключен к шине инверсного значения четвертого двоичного разряда десятичного разряда второго операнда устройства, BTojMbie входы элементов И третьей тетрады под ключены к управляющему входу приема в обратном коде второго операнда устройства, выходы элементов И третьей тетрады подключены к первым входам соответствующих элементов тетрады элементов ИЛИ, вторые входы которых подключены к выходам элементов И второй тетрады, а выходы элементов ИЛИ тетрады подключены к вторым входам соответствующих одноразрядных суммйторов, а также тем, что преобразователь прямого кода в обратный состоит из двух элементов И, причем первый и второй входы первого элемента И подключены к первому и второму входам преобразователя соответственно, а выход первого элемента И подключен к первому выходу пребразователя, первый и второй входы второго элемента И подключены к третьему Я четвертому входам преобразователя соответственно, а выход второго эпемента И подключен к второму выходу :5)еобразователя прямого кода в обратный. Реализация операшш вычитания фибоначчиево-десятичных кодов обеспечивается путем преобразования вычитаемото ( Ъ , Ъ , tt., -b ), в обсеггный ибоначчйево-десятичный код. Обратный код образуется дополнений каждой дес$ггячной до девятки. Логические функ- или, реализуемые преобразователем, определяются из табл. 1. Учитьюая, что прямые коды постуяа- ют на вход преобразователя только в нормальной форме, т.е. других кодовых комбинаций помимо перечисленных в таблице р графе Прямой код на входе преобразователя быть не может, на основании таблицы выражаем Y j r , , Y4 как функшш от Ъ ,3,ti, b : , ьа основании этих выражений стрсаггся преобразователь кода каждой десятичной цифры. Очевидно, что при преобразовании обратного кода в прямой логические функции, реализуемые преобразователем, останутся прежними, т.е. преобразователь может быть использован и для преобразования из обратного кода в прямой. На чертеже приведена функциональная схема одного десятичного разряда устройства. 5& Схема состсят из трех тетрад эпементов И 1 - 3, преобразователя 4 пря мого кода в обратный, тетрады элементов ИЛИ 5, фябоначчиево-десятичного сумматора 6. Тетрады элементов И 1 и 2 предназначены для 1риема в сумматор операндов в прямом коде. Первые входы элементов И этих тетрад соединены с управляющими входами приема в прямом коде первого операнда { Пр ПК ) и вто.рого операнда (fip ПК( ) соответственно а вторые входы представляют собой входы операндов устройства °4°4 L« l Ч Ч Ч Тетрада элементов И 3 предназначена для приема в фибона-ччиево-десятичный сумматор обратного кода второго операнда, перовые входы элементов И этой тетрады соединены с управляющим входом приема в обратном коде второго операнда ( ПрОХА ), вторые входы соединены с выходом преобразователя прямого кода в обратный X,N , Y ,Ч, Преобразователь 4 прямого кода в обратный предназначен для преобразования прямого десятично-фибоначчиевого) кода в обратный. Он состсжт из элементов И 7 и 8, которые реализуют логические функции N зЦ Фибоначчиево-десятичный сумматор 6 представляет собой совокупность четырех одноразрядных сумматоров, предназначенньк для суммирования двух десятично-4иброначчиев| х цифр А и В, которые соответствуют .разрядам с весами . 5, 3, 2 и 1, соединенных между собой ;аеп51ми переносов на основании правил суммирования в тетрадах. Выходы сумма являются внешними выходами устройства. Устройство работает следующим обра зе. Одновременно на входы операндов устройства поступают коды суммируемы десятичных чисел А и В в нормальной форме системы Фибоначчи. Если должна выполняться операция сложения кодов, т : на первые входы тетрад элементов И и 2 поступают управляющие сигналы 2-6 ПрПК .и ПрПК, вследствие чего числа А и В поступают на входы ябоначчиевод есятичного сумматора 6 в прямом коде. Суммирование в фибоначчиево-десяти1Ьном сумматоре приведено в табл. 2. Сложетше кодов производится за 2 такта: 1-ый такт - формирование непоп- с ных сумм и переносов Р РП . Р Рд причем переносы PIJ и Pg не, могут возникнуть одновременно ввиду того, что операнды А и В представлены в нормаль ной форме; 2-ой такт - формирование полной суммы S , Si Sft f 1 На этом процесс споження фи наччиево-десятичных кодов оканчивается. вьшолнении операции вычитания кодов на первые входы тетрады элементов И 1 также поступает сигнал ПрПК , а на первые входы тетрады элементов И 3 - сигнал ПрОК, в результате чего первый операнд. поступает на входы фнбоначчяево-десятичного сумматора в прямом коде, а второй операнд, уже преобразованный на преобразователе 4 прямого кода в обрат- ный в соотв ствв с логическими функцийми Х ,2. 1 3 3% V - 1э4 ВЫХОДОВ преобразователя через тетраду элементов И 3 поступает на входы фибонйччиево-десятичногч) сумматора в обратном коде. После суммирования на фнбоначчиево-десятячном сумматоре, . которое вьшолняется аналогично, на выходе фибоначчиево-десятичного сумматора формируется обратный код разности. По сравнению с известным 4ибся аччиево-десятичным сумматором, предлагаемое устройство сохраняет все его достоинства и обладает более широкими функциональными возмажност$п ш, т.е. креме операшш сложения кодов реализует за счет использования преобразователя прямого фибоначчкево-десятнчноГо кода в обратный я операцию вычитания кодов. Т. к. время преобразования мало (время задержки коньюнкторов), то введение преобразователя не умензьшает быстродействия предлагаемого устройства по сравнению с известным.

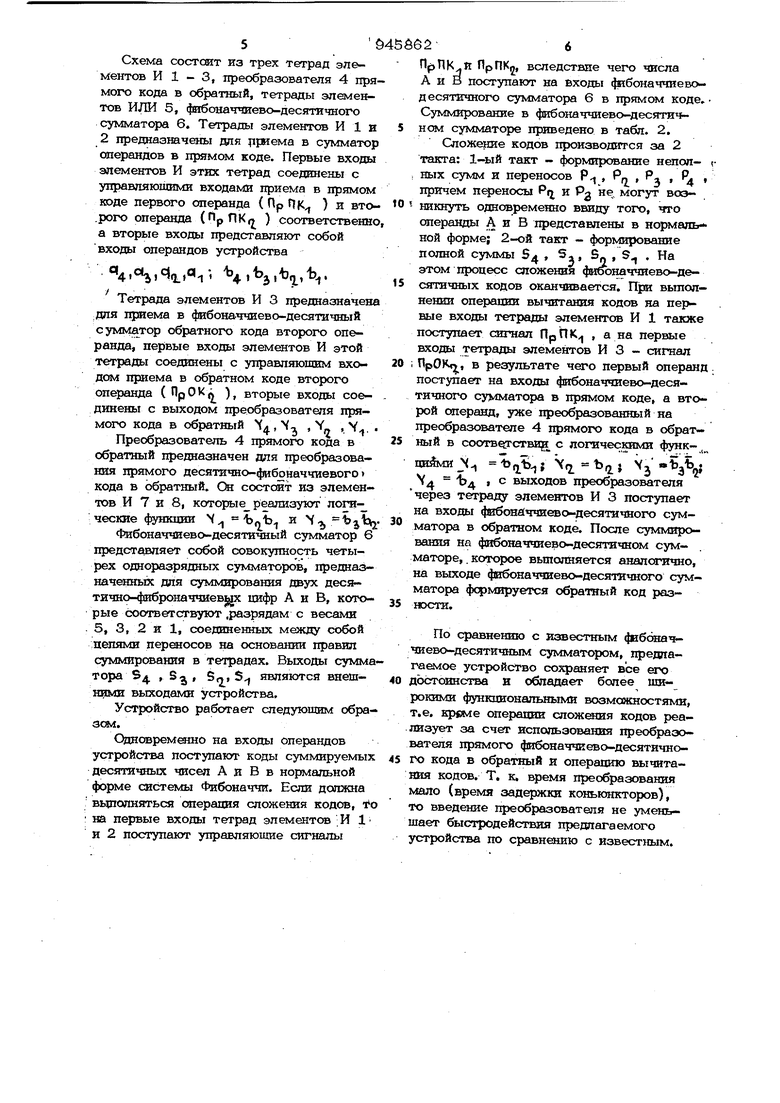

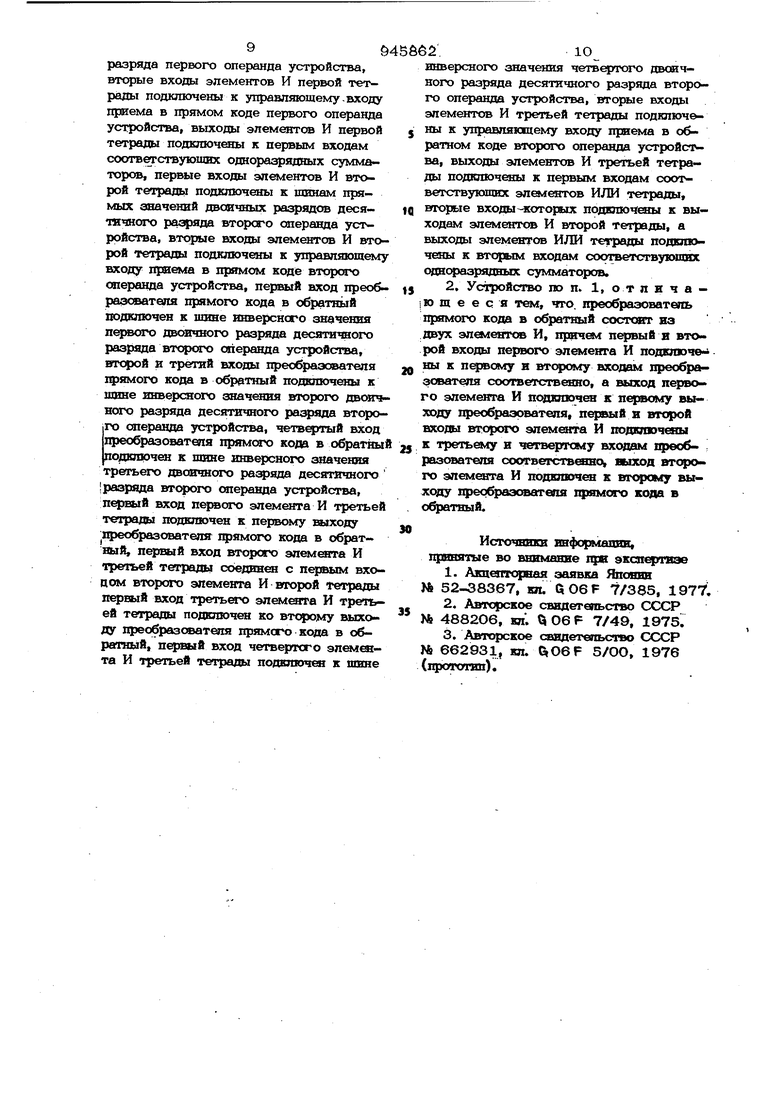

Переменные веса разрядов в фБгбаваччвево-десяшчной системе счислений

яа четырех однсразр51дных сумматоров, выходы суммы которых 5тпяются выходами устройства, и элемента ИЛИ, о т личающееся тем, что, с цепью

щюобразоватепь прямсвхэ кода в обратный и тетраду элементов ИЛИ, причем первые входы элементов И первой тетрады подключены к шинам прямых значений даоичных разрядов десятичного

разряда первого операнда устройства, вторые входы элементов И первой тетр ады подключены к управляющему.входу приема в прямом коде первого операнда устройства, выходы элементов И первой тетрады подключены к первым входам соответствующих одноразрядных сумматоров, первые входы элементов И второй тетрады подключены к шшшм прямых значений двсжчных разрядов десятичного разряда второго операнда устройства, вторые шсоды элементов И второй тетрады подключены к управл5Ш)шему входу теряема в прямом коде второго операнда устройства, первый вход преобразоеатепя прямого кода в обратный подключен к шине инверсного значения двоичного разряда десяти ого разряда вторсго операада устройсхга, второй в третий входы преобразсжателя i siMoro кода в обратный подключены к шине шшерсного значенЕЯ второго двсягоного разрзда десятичного paspafua второго операнда устройства, четвертый вход преобразователя прямого кода в обратны подключен к шнне инверсного значения третьего двоичного разряда десятичного разряда второго операнда устройства, первый вход первого элемента И третьей тетрады подключен к первому выходу преобразоватеяя щ ямого кода в обратный, первый вход вторсзго элемеята И третьей тетрады сбединен с первым входом второго элемента И второй -тетрады перБЫЙ вход третьего элемента И третьей тетрады подключен ко второму выходу преобразователя прямого кода в обратный, первый вход четвертого эпвм та И третьей тетрады подалючея к шхсне

инверсного значения четвертого двоичного разряда десятичного разряда второго операнда устройства, вторые входы элементов И третьей тетрады подключоны к управляющему входу проема в обратном коде второго операнда устройства, выходы элементов И третьей тетрады подключены к первым входам соответствующих ИЛИ тетрады,

входы toToptux лодвлючены к выходам элементов И второй тетрады, а выходы элементов ИЛИ тетрады подключены к вторлм входам соответствукшшх одвс разрядных сумматоров

ны к nejffiOMy в iBftapoMy входам преобразователя соответственно, а выход первого элемента И подключен к первому выходу тфесбразрвателя, первый в второй ВХОФ1 второго элемента И подключены

к третьему в четвертому входам преоб- , разователя ооотвегствеввс выход второго элемента И подключев к второму выходу ярербраасжатепя щшмого кода в обратный.

И |L QiffgfiC|K ВНфорМ311ИИ§ ПСШНЯТЫб во ВНИМЯВИб ЭКСЯСР1

52-38367, кп. (5O6F 7/385, 1977,

Авторы

Даты

1982-07-23—Публикация

1981-01-27—Подача