Изобретение относится к устройствам тестового контроля логических схем и диагностики неисправностей и является усовершенствованием известного устройства, описанного в авт .св. № 746553. ,

Целью изобретения является повышение достоверности контроля за счет исключения потерь информации о неисправностях в регистре.

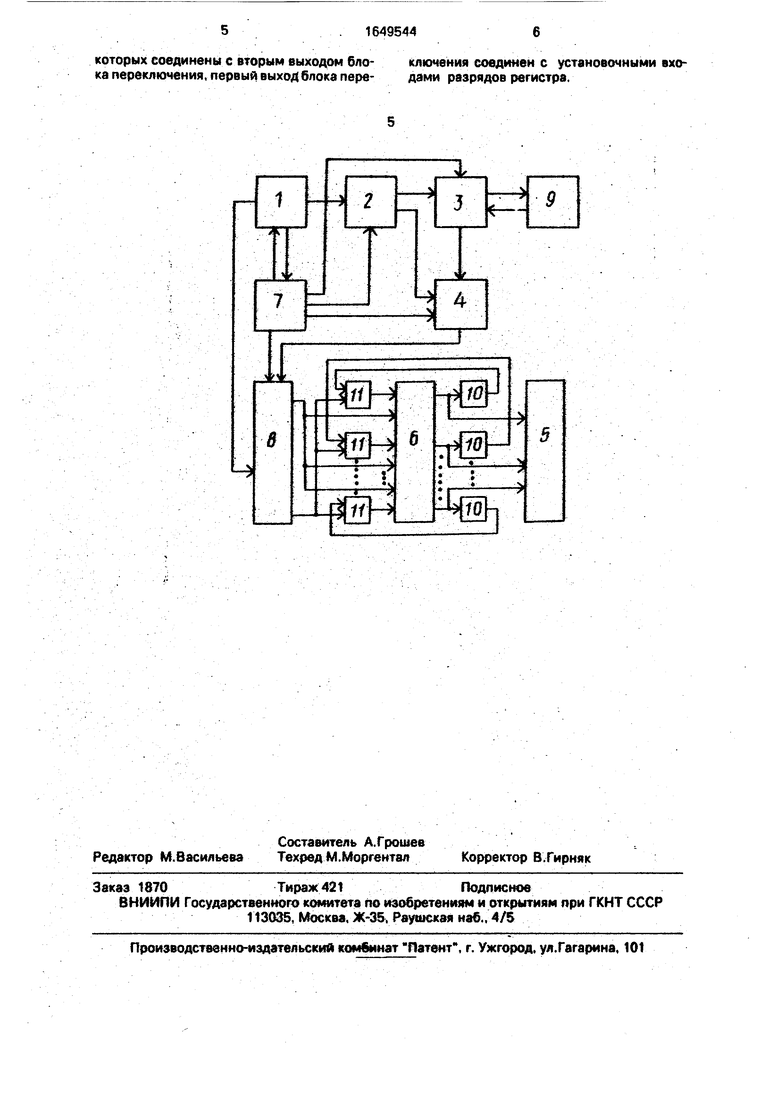

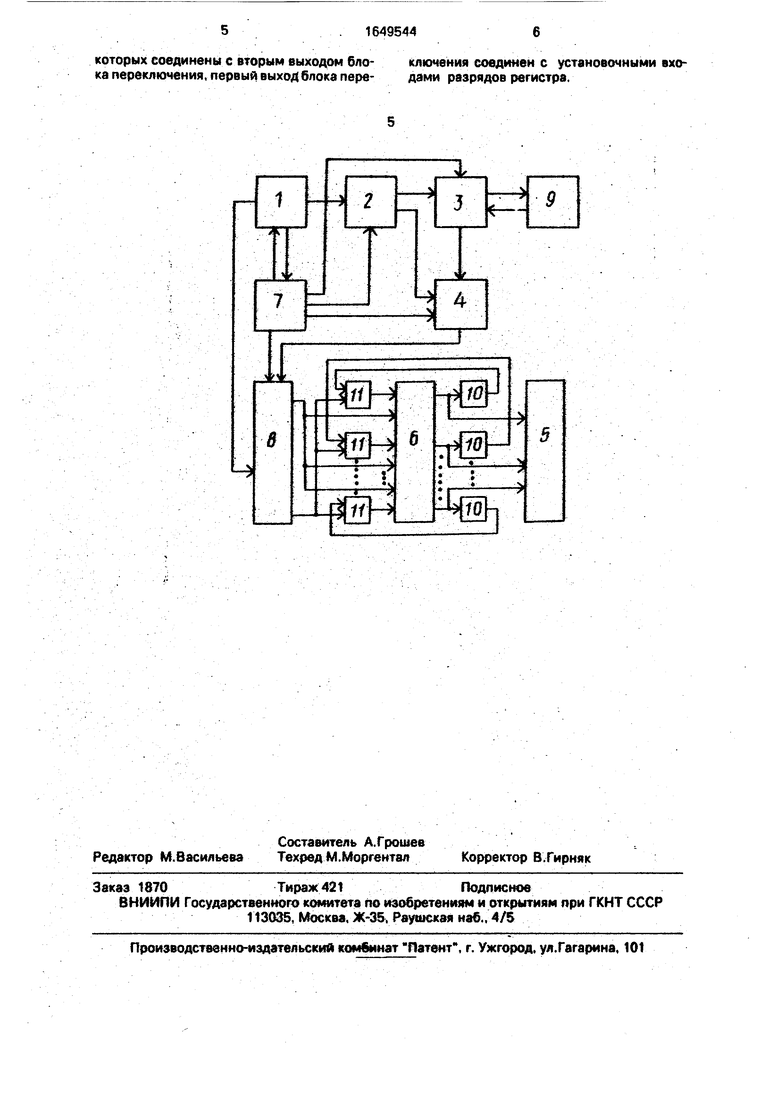

На чертеже представлена структурная схема устройства для контроля цифровых блоков.

Устройство содержит блок Л ввода, блок 2 памяти, коммутатор 3, блок 4 сравнения, блок 5 индикации, регистр 6, блок 7 управления, блок 8 переключения, контролируемый 9 блок, элементы задержки 10, элементы И 11,

Устройство работает следующим образом.

В исходном состоянии блок 2 памяти и регистр 6 по командам с блока 7 управления установлены в нулевое состояние (цепи

сброса не показаны) Вначале с блока 1 ввода вводится информация о проверяемых неисправностях и по командам с блока 7 управления через блок 8 переключения записывается в регистр 6 Информация о проверяемых неисправностях является перечнем неисправностей, проверяемых в контролируемом блоке 9 Разрядность регистра 6 равна максимальному количеству проверяемых неисправностей в блоке 9. Регистр 6 может быть выполнен, например, в виде набора RS-триггеров, -количество которых равно максимальном количеству проверяемых неисправностей а блоке 9. При этом R-входы триггеров являются входами сброса соответствующих разрядов регистра 6. S-входы триггеров являются установочными входами соответствующих разрядов регистра 6, а инверсные выходы триггеров являются выходами регистра 6. При вводе информации о проверяемых неисправностях соответствующие разряды регистра 6 устанавливаются в 1, если соЈ

О

ч ел

hJ

ответствующая неисправность проверяется в данном объекте контроля. После подготовки регистра б по командам с блока 7 управления тестовая информация записывается в блок 2 памяти. Стимулы из блока 2 памяти поступают через коммутатор 3 на входы контролируемого блока 9, а эталоны - на первые входы блока 4 сравнения, Управление работой коммутатора 3 осуществляется из блока 7 управления.

По результатам сравнения, если контролируемый блок исправен, появляется высокий потенциал на выходе блока 4 сравнения. После подачи на входы блока 9 очередного набора по команде с блока 7 управления из блока 1 вводится диагностическая информация (номера неисправностей, проверяемых в каждом тесте), которая через блок 8 переключения и элементы И 11 поступает на установку в О разрядов регистра в. Диагностическая информация представляет собой позиционный код, длина которого (разрядность) равна общему количеству проверяемых неисправностей, причем только в разрядах позиционного кода, соответствующих проверяемым в данном тесте неисправностям, записаны 1. Если в очередном тесте не обнаружены неисправности, т.е. на выходе блока 4 сравнения 1, то разряды регистра б, соответствующие коду диагностической информации данного теста, устанавливаются в О. Сигнал на выходе блока 4 сравнения разрешает запись диагностической информации в регистр 1. Если же в очередном тесте обнаружена неисправность, то установление в О разрядов регистра 6 не происходит. После ввода диагностической информации по командам с блока 7 управления в блок 2 памяти вводится следующий тест, который поступает затем на входы блока 9, и начинается ввод диагностической информации.

Рассмотрим работу устройства в ситуации, когда диагностическая информация, соответствующая разным тестам, содержит 1 в некоторых одних и тех же разрядах и тест, в котором не обнаружены неисправности, следует за тестом, в котором были обнаружены неисправности. В этом случае после прохождения теста, в котором были обнаружены неисправности, работа устройства аналогична рассмотренному выше и в регистр 6 записывается 1 в соответствующих разрядах. При прохождении затем теста, в котором не было обнаружено неисправностей, разряды регистра 6, соответствующие коду диагностической информации данного теста, устанавливаются в О, за исключением тех разрядов регистра,

в которых Г совпали для разных тестов. Запись и стирание информации в регистр 6 происходит следующим образом.

Время задержки At элементами 10 выбирается исходя из того, чтобы сигнал 1, устанавливающий в О разряды регистра при отсутствии неисправности, поступил на второй вход соответствующего элемента И 11 и далее на нулевой вход соответствующего разряда регистра 6 до прихода О с инверсного выхода данного разряда на первый вход элемента И 11. В этом случае на обоих входах элемента И 11 будет Г, следовательно и на нулевом входе соответствующего разряда регистра 6 будет 1, т. е. данный разряд будет установлен в О. При обнаружении неисправности установление в О разрядов регистра 6 не происходит., так как на второй вход элементов И 11 не

приходит 1 и на выходе элементов И 11 будет О. При этом для последующих тестов на первом входе элементов И 11 для разрядов, в которых записана 1, постоянно будет присутствовать О и, следовательно.

если в данном разряде будет 1 в каком-либо последующем тесте, в котором неисправности не обнаружены, то стирания 1 в данном разряде не произойдет, т.е. в регистре 6 сохранится информация о всех обнаруженных неисправностях.

После прохождения всех тестов в регистре б устанавливаются 1 тех разрядов, которые соответствуют неисправностям, проверяемым в неисправных тестах, и соответствующие в исправных тестах (исправный считается тест, на котором неисправность не проявляется, неисправным - в котором неисправность контролируемого блока 9 проявляется). Таким образом,

блоком 4 сравнения фиксируется факт наличия неисправности, а в регистре 6 фиксируются номера неисправностей, которые после проверки отображаются блоком 5 индикации. Зная номер неисправности, по

таблице неисправностей находят номер неисправного элемента и вид неисправности.

Формула изобретения Устройство для контроля цифровых блоков по авт.св. № 746553, отличающее- с я тем. что, с целью повышения достоверности контроля за счет исключения потерь информации о неисправностях в регистре, в него введены п элементов задержки и г элементов И, причем выход каждого элемента И соединен с входом сброса соответствующего разряда регистра, выход каждого разряда регистра соединен через соответствующие элементы задержки с первыми входами элементов И, вторые входы

которых соединены с вторым выходом бло- ключения соединен с установочными вхо- ка переключения, первый выход блока пере- дами разрядов регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1985 |

|

SU1247898A2 |

| Устройство для контроля цифровых блоков | 1978 |

|

SU746553A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для диагностики неисправностей технических объектов | 1987 |

|

SU1515175A2 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

Изобретение относится к устройствам тестового контроля логических схем и диагностики неисправностей и является усовершенствованием известного устройства, описанного в авт ев № 746553 Целью изобретения является повышение достоверности контроля за счет исключения потерь информации о неисправностях в регистре Устройство содержит блок ввода, блок памяти, коммутатор, блок сравнения, блок индикации, регистр, блок управления, блок переключения, контролируемый блок, п элементов задержки, п элементов И 1 ил

| Устройство для контроля цифровых блоков | 1978 |

|

SU746553A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-15—Публикация

1988-06-15—Подача