Изобретение относится к вычислительной технике и может быть использовано в двухмапшнных вычислительных комплексах для обмена информацией между двумя ЭВМ.

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения программной установки различных режимов обмена.

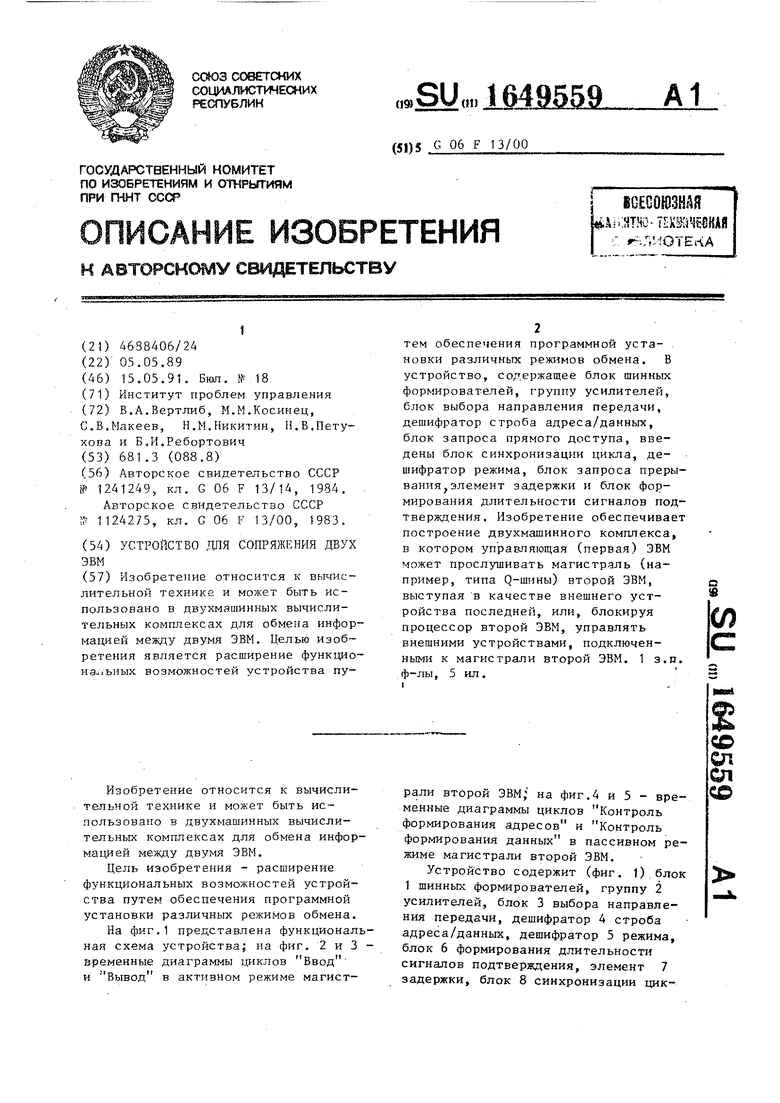

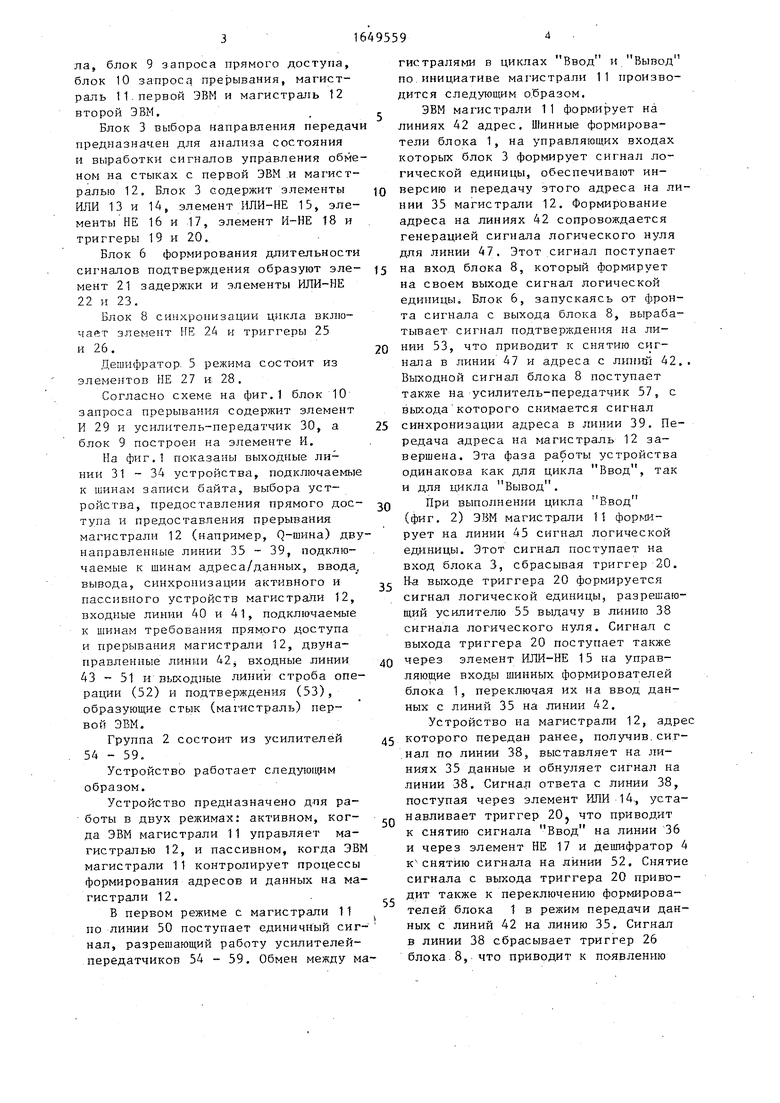

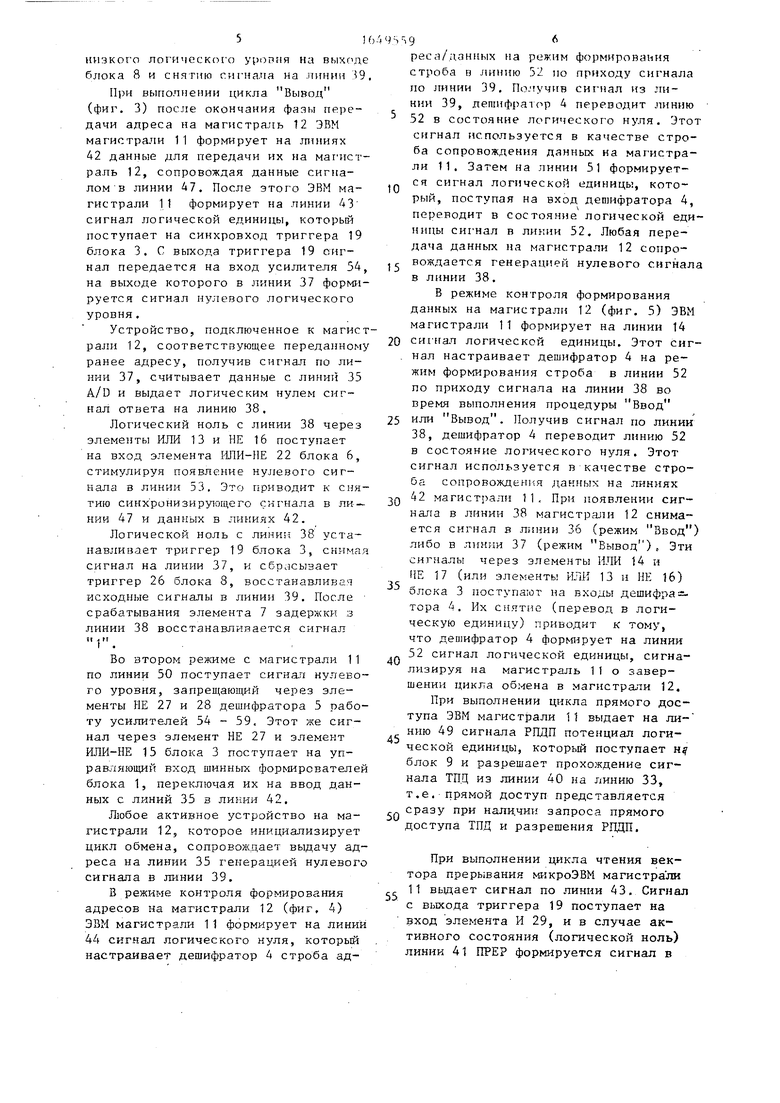

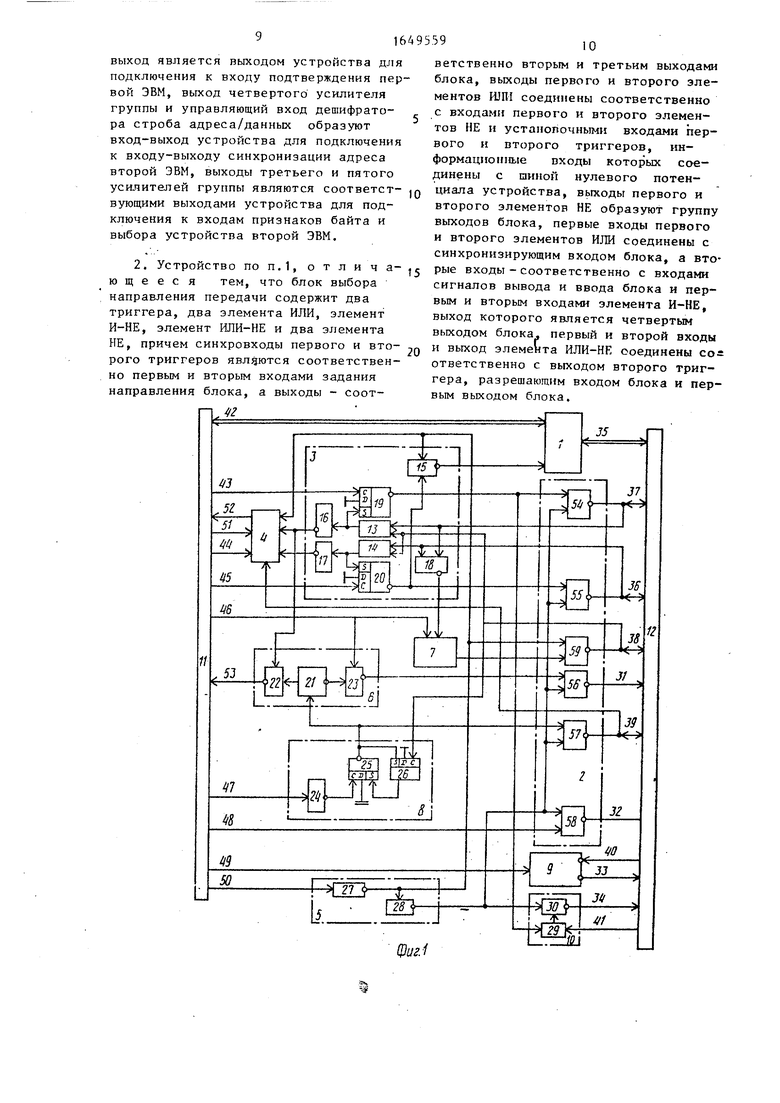

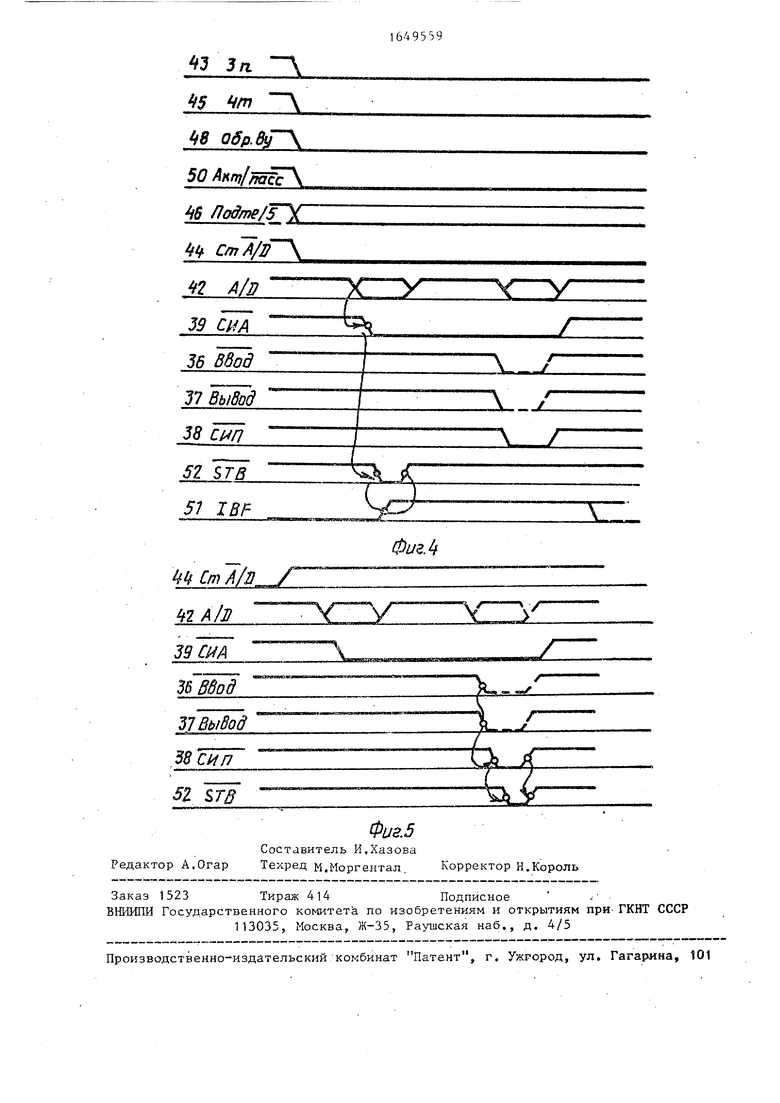

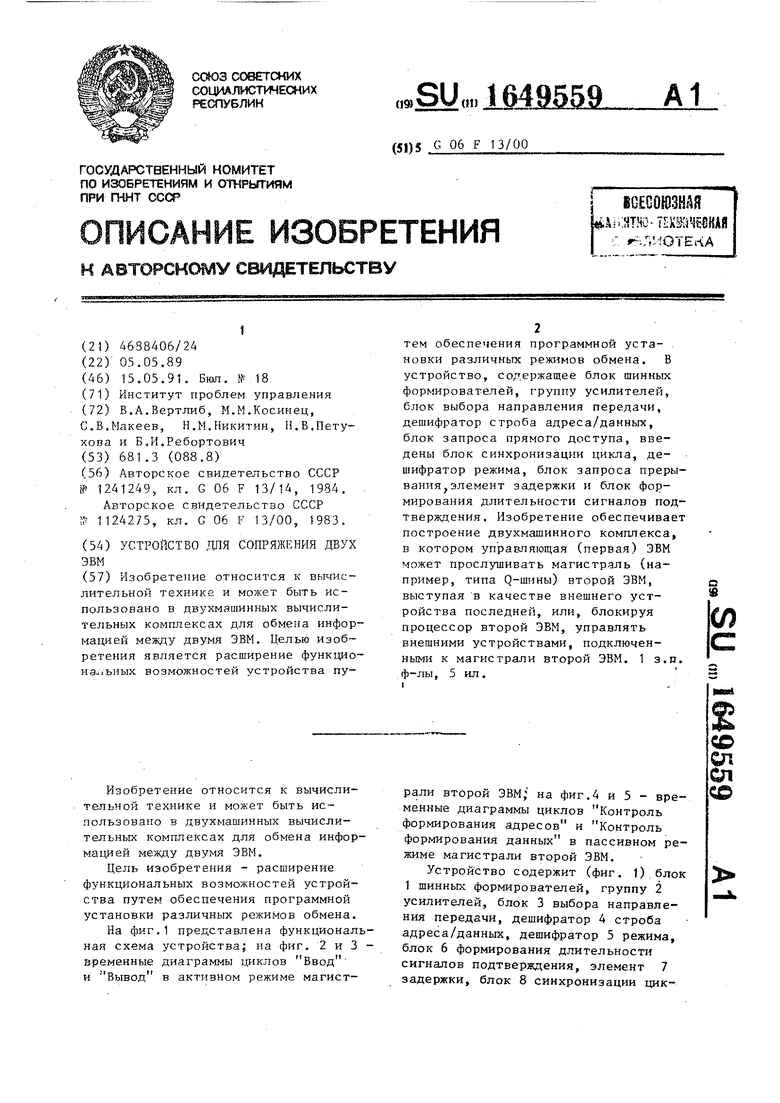

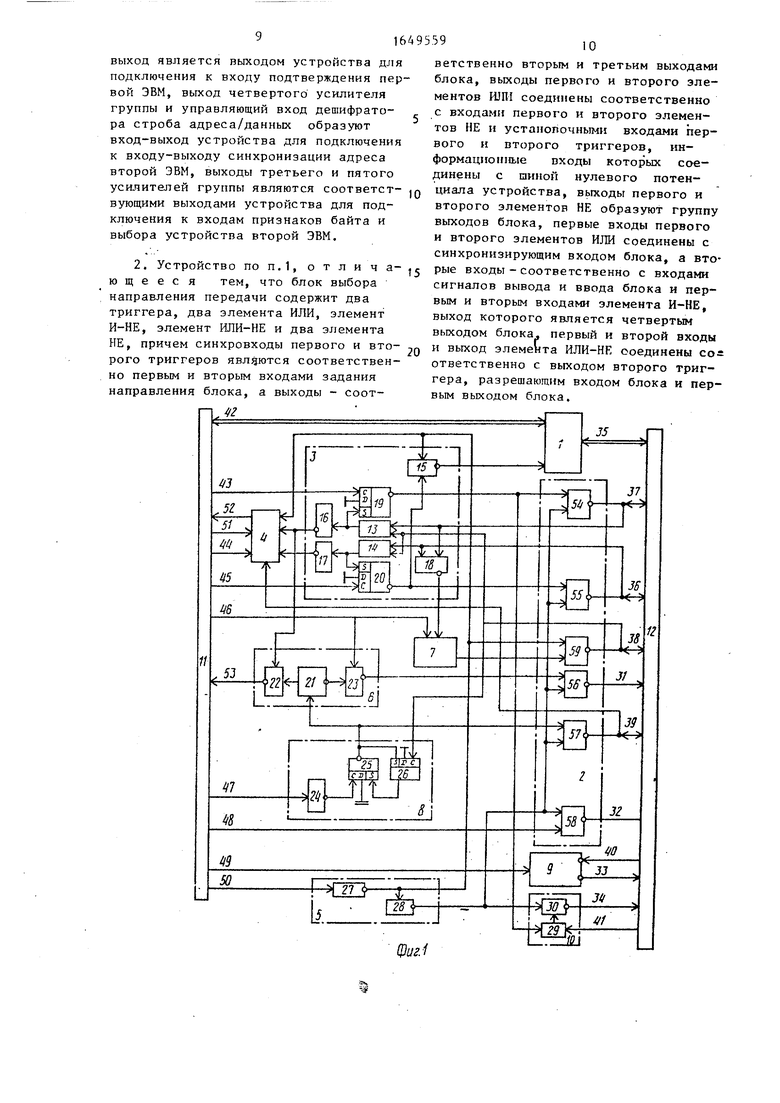

На фиг.1 представлена функциональная схема устройства; на фиг. 2 и 3 - временные диаграммы циклов Ввод и Вывод в активном режиме магистрали второй ЭВМ; на фиг.4 и 5 - временные диаграммы циклов Контроль формирования адресов и Контроль формирования данных в пассивном режиме магистрали второй ЭВМ.

Устройство содержит (фиг. 1) блок 1 шинных формирователей, группу 2 усилителей, блок 3 выбора направления передачи, дешифратор 4 строба адреса/данных, дешифратор 5 режима, блок 6 формирования длительности сигналов подтверждения, элемент 7 задержки, блок 8 синхронизации цикCD

сл

СЛ

ла, блок 9 запроса прямого доступа, блок 10 запросу прерывания, магистраль 11 первой ЭВМ и магистраль 12 второй ЭВМ.

Блок 3 выбора направления передач предназначен для анализа состояния и выработки сигналов управления обменом на стыках с первой ЭВМ и магистралью 12. Блок 3 содержит элементы ИЛИ 13 и 14, элемент ИЛИ-НЕ 15, элементы НЕ 16 и 17, элемент И-НЕ 18 и триггеры 19 и 20.

Блок 6 формирования длительности сигналов подтверждения образуют элемент 21 задержки и элементы ИЛИ-НЕ 22 и 23.

Блок 8 синхронизации цикла вклю- элемент НЕ 24 и триггеры 25 и 26.

Дешифратор 5 режима состоит из элементов НЕ 27 и 28.

Согласно схеме на фиг.1 блок 10 запроса прерывания содержит элемент И 29 и усилитель-передатчик 30, а блок 9 построен на элементе И.

На фиг.1 показаны выходные линии 31-34 устройства, подключаемые к шинам записи байта, выбора устройства, предоставления прямого доступа и предоставления прерывания магистрали 12 (например, Q-шина) двунаправленные линии 35 - 39, подключаемые к шинам адреса/данных, ввода, вывода, синхронизации активного и пассивного устройств магистрали 12, входные линии 40 и 41, подключаемые к шинам требования прямого доступа и прерывания магистрали 12, двунаправленные линии 42, входные пинии 43 - 51 и выходные линии строба операции (52) п подтверждения (53), образующие стык (магистраль) первой ЭВМ,

Группа 2 состоит из усилителей 54 - 59.

Устройство работает следующим образом.

Устройство предназначено дня работы в двух режимах: активном, когда ЭВМ магистрали 11 управляет магистралью 12, и пассивном, когда ЭВМ магистрали 11 контролирует процессы формирования адресов и данных на магистрали 12.

В первом режиме с магистрали 11 по линии 50 поступает единичный сигнал, разрешающий работу усилителей- передатчиков 54 - 59. Обмен между ма

5

0

5

0

5

0

5

0

5

гистралями в циклах Ввод и Вывод по инициативе магистрали 11 производится следующим образом.

ЭВМ магистрали 11 формирует на линиях 42 адрес. Шинные формирователи блока 1, на управляющих входах которых блок 3 формирует сигнал логической единицы, обеспечивают инверсию и передачу этого адреса на линии 35 магистрали 12. Формирование адреса на линиях 42 сопровождается генерацией сигнала логического нуля для линии 47. Этот сигнал поступает на вход блока 8, который формирует на своем выходе сигнал логической единицы. Блок 6, запускаясь от фронта сигнала с выхода блока 8, вырабатывает сигнал подтверждения на линии 53, что приводит к снятию сигнала в линии 47 и адреса с линю 42.. Выходной сигнал блока 8 поступает также на усилитель-передатчик 57, с выхода которого снимается сигнал синхронизации адреса в линии 39. Передача адреса на магистраль 12 завершена. Эта фаза работы устройства одинакова как для цикла Ввод, так и для цикла Вывод.

При выполнении цикла Ввод (фиг. 2) ЭВМ магистрали 11 формирует на линии 45 сигнал логической единицы. Этот сигнал поступает на вход блока 3, сбрасывая триггер 20. fta выходе триггера 20 формируется сигнал логической единицы, разрешающий усилителю 55 выдачу в линию 38 сигнала логического нуля. Сигнал с выхода триггера 20 поступает также через элемент ИЛИ-НЕ 15 на управляющие входы шинных формирователей блока 1, переключая их на ввод данных с линий 35 на линии 42.

Устройство на магистрали 12, адрес которого передан ранее, получив сигнал по линии 38, выставляет на линиях 35 данные и обнуляет сигнал на пинии 38. Сигнал ответа с линии 38, поступая через элемент ИЛИ 14, устанавливает триггер 20} что приводит к снятию сигнала Ввод на линии 36 и через элемент НЕ 17 и дешифратор 4 к4снятию сигнала на линии 52. Снятие сигнала с выхода триггера 20 приводит также к переключению формирователей блока 1 в режим передачи данных с линий 42 на линию 35. Сигнал в линии 38 сбрасывает триггер 26 блока 8, что приводит к появлению

низкого логически о урогшя на выход блока Я и снятию гигнапа на пинии 9

При выполнении цикла Вывод (фиг. 3) после окончания фазы пере- дачи адреса на магистраль 12 ЭВМ магистрали 11 формирует на линиях 42 данные для передачи их на магистраль 12, сопровождая данные сигналом в линии 47. После этого ЭВМ ма- гистрали 11 формирует на пинии 43 сигнал логической единицы, который поступает на синхровход триггера 19 блока 3. С выхода триггера 19 оиг- нал передается на вход усилителя 54 на выходе которого в линии 37 формируется сигнал нулевого логического уровня.

Устройство, подключенное к магисрали 12, соответствующее переданном ранее адресу, получив сигнал по линии 37, считывает данные с линий 35 A/D и выдает логическим нулем сигнал ответа на линию 38.

Логический ноль с линии 38 через элементы ИЛИ 13 и НЕ 16 поступает на вход элемента Ш1И-НЕ 22 блока 6, стимулируя появление нулевого сигнала в линии 53. Это приводит к снятию синхронизирующего сигнала в ли- нич 47 и данных в линиях 42.

Логической ноль с линии 38 устанавливает триггер 19 блока 3, снима сигнал на линии 37, и сбрасывает триггер 26 блока 8, восс ганавливг ч исходные сигналы в линии 39. После срабатывания элемента 7 задержки з линии 38 восстанавливается сигнал

И . It

Во втором режиме с магистрали 11 по линии 50 поступает сигнал нулевого уровня, запрещающий через элементы НЕ 27 и 28 дешифратора 5 работу усилителей 54 - 59, Этот же сигнал через элемент НЕ 27 и элемент ИЛИ-НЕ 15 блока 3 поступает на управляющий вход шинных формирователе блока 1, переключая их на ввод данных с линий 35 в 42.

Любое активное устройство на ма- гистрали 12, которое инициализирует цикл обмена, сопровождает выдачу адреса на линии 35 генерацией нулевог сигнала в линии 39.

В режиме контроля формирования адресов на магистрали 12 (фиг, 4) ЭВМ магистрали 11 формирует на лини 44 сигнал логического нуля, который настраивает дешифратор 4 строба ад

15

20

25

30

.

10, т

в 35

40 45

50

55

) j Ь i 9л

рее а/данных на режим формирования строба в линию 52 по приходу сигнала по линии 39. Получив сигнал из линии 39, дешифратор 4 переводит линию 52 в состояние логического нуля. Этот сигнал используется в качестве строба сопровождения данных на магистрали 11. Затем на линии 51 формируется сигнал логической единицы, который, поступая на вход дешифратора 4, переводит в состояние логической единицы сигнал в линии 52, Любая передача данных на магистрали 12 сопровождается генерацией нулевого сигнала в линии 38.

В режиме контроля формирования данных на магистрали 12 (фиг. 5) ЭВМ магистрали 11 формирует на линии 14 CHI нал логической единицы. Этот сигнал настраивает дешифратор 4 на режим формирования строба в линии 52 по приходу сигнала на линии 38 во время выполнения процедуры Ввод или Вывод. Получив сигнал по линии 38, дешифратор 4 переводит линию 52 в состояние логического нуля. Этот сигнал используется в качестве строба сопровождения данных на линиях 42 магистрали 11, При появлении сигнала в линии 38 магистрали 12 снимается сигнал в линии 36 (режим Ввод) либо в линии 37 (режим Вывод) Эти сигналь через элементы ИЛИ 14 н НЕ 17 (или элементы ИЛИ 13 и НЕ 16) блока 3 поступают на входы дешифра - тора 4. Их снятие (перевод в логическую единицу) приводит к тому, что дешифратор 4 формирует на линии 52 сигнал логической единицы, сигнализируя на магистраль 11 о завершении цикла обмена в магистрали 12.

При выполнении цикла прямого доступа ЭВМ магистрали 1t выдает на ли- нию 49 сигнала РПДП потенциал логической единицы, который поступает н блок 9 и разрешает прохождение сигнала ТПЦ из линии 4Q на линию 33, т.е. прямой доступ представляется сразу при наличии запроса прямого доступа ТПД и разрешения РПДП.

При выполнении цикла чтения вектора прерывания микроЭВМ магистрали 11 выдает сигнал по линии 43. Сигнал с выхода триггера 19 поступает на вход элемента И 29, ив случае активного состояния (логической ноль) линии 41 ПРЕР формируется сигнал в

линии 34 ППРО и осуществляется цикл чтения вектора прерывания.

Формула изобретения

1. Устройство для сопряжения двух ЭВМ, содержащее блок шинных формирователей, первая и вторая группы информационных входов-выходов которого являются соответствующими группами входов-выходов устройства для подключения к информационным шинам первой и второй ЭВМ, блок выбора направления передачи, первым выходом подключенный к управляющему входу блока шинных Формирователей, дешифратор строба адреса/данных, выход которого чвлпетсч выходом устройства для подключения к входу синхронизаци первой ЭВМ,, а первая группа информационных входов соединена с группой выходов блока выбора направления передачи, первый и второй входы задания направления которого являются соответствующими входами устройства для подключения к выходам записи и чтения первой ЭВМ, группу усилителей и блок запроса прямого доступа, входы разрешения и запроса которого являются соответствующими входами устройства для подключения к выходу разрешения первой ЭВМ и выходу запроса прямого доступа второй ЭВМ, с отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения программной установки различных режимов обмена, в него вве

Q

третий выходы блока выбора направления передачи соединены соответственно с информационными входами первого и второго усилителей группы, информационные входы третьего и четвертого усилителей группы подключены соответственно к первому выходу блока формирования длительности сигналов подтверждения и выходу блока синхронизации, цикла, запускающий вход которого является входом устройства для подключения к синхронизирующему выходу первой ЭВМ, вход сброса блока синхронизации цикла, соединенный с синхронизирующим входом блока выбора направления передачи, и выход шестого усилителя группы образуют вход- выход устройства для подключения к входу-выходу ответа второй ЭВМ, выходы первого и второго усилителей группы, соединенные соответственно с входами сигналов вывода и ввода блока выбора направления передачи, образуют соответствующие входы-выходы устройства для подключения к входам-выходам сигналов управления выводом и вводом второй ЭВМ, информационный вход шестого усилителя группы соединен с выходом элемента задержки, входом пуска подключенного к четвертому выходу блока выбора направления передачи, второй выход которого соединен с первым вхо- дом запроса прерывания блока запроса прерывания, второй вход запроса прерывания и выход которого являются соответствующими входом и выходом устройства для подключения к выходу

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1987 |

|

SU1411764A1 |

| Устройство для сопряжения масс-спектрометра с ЭВМ | 1988 |

|

SU1580379A1 |

| Многопроцессорная система | 1988 |

|

SU1605247A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1986 |

|

SU1368883A1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1793440A1 |

Изобретение относится к вычислительной технике и может быть использовано в двухмашинных вычислительных комплексах для обмена информацией между двумя ЭВМ. Целью изобретения является расширение функцио- на льных возможностей устройства путем обеспечения программной установки различных режимов обмена. В устройство, содержащее блок шинных формироватепей, группу усилитепей, блок выбора направления передачи, дешифратор строба адреса/данных, блок запроса прямого доступа, введены блок синхронизации цикла, дешифратор режима, блок запроса прерывания, элемент задержки и блок формирования длительности сигналов подтверждения. Изобретение обеспечивает построение двухмашинного комплекса, в котором управляющая (первая) ЭВМ может прослушивать магистраль (например, типа Q-шины) второй ЭВМ, выступая в качестве внешнего устройства последней, или, блокируя процессор второй ЭВМ, управлять внешними устройствами, подключенными к магистрали второй ЭВМ. 1 з.п. ф-лы, 5 ил. о

дены блок синхронизации цикла, дешиф- Q требования прерывания и входу предоратор режима, блок запроса прерывания, блок формирования длительности сигналов подтверждения и элемент задержки, причем вход дешифратора режима является входом устройства для подключения к выходу режима первой ЭВМ, а первый выход подключен к разрешающим входам с первого по пятый усилителей группы и разрешающему входу блока запроса прерывания, второй выход дешифратора режима соединен с разрешающими входами шестого усилителя группы, блока выбора направления передачи и дешифратора строба адреса/данных, вторая группа информационных входов которого является группой входов устройства для подключения к группе синхронизирующих выходов первой ЭВМ, второй и

ставления прерывания второй ЭВМ, выход блока запроса прямого доступа является выходом устройства для подключения к входу предоставления пря- 5 мого доступа второй ЭВМ, информационный вход пятого усилителя группы и вход сброса элемента задержки, соединенный с первым входом разрешения блока формирования длительности сигналов подтверждения, являются соответствующими входами устройства для подключения к выходам сигналов подтверждения и выбора устройства первой ЭВМ, вход пуска и второй вход разрешения блока формирования длительности сигналов подтверждения соединены соответственно с выходом блока синхронизации цикла и группой выходов блока выбора направления передачи, а второй

0

5

выход является выходом устройства для подключения к входу подтверждения первой ЭВМ, выход четвертого усилителя группы и управляющий вход дешифратора строба адреса/данных образуют вход-выход устройства для подключения к входу-выходу синхронизации адреса второй ЭВМ, выходы третьего и пятого усилителей группы являются соответст- вующими выходами устройства для подключения к входам признаков байта и выбора устройства второй ЭВМ.

15

И-НЕ, элемент ИЛИ-НЕ и два элемента выходом олока. первый и второй входы НЕ, причем синхровходы первого и вто- 20 „ ВЫХоД элемента ИЛИ-НЕ соединены со- рого триггеров являются соответствен- ответственно с выходом второго триг- но первым и вторым входами задания Гера, разрешающим входом блока и пер- направления блока, а выходы - соот- Вым выходом блока.

ветственно вторым и третьим выходами блока, выходы первого и второго элементов ИЛИ соединены соответственно с входами первого и второго элементов НЕ и установочными входами первого и второго триггеров, информационные входы которых соединены с шиной нулевого потенциала устройства, выходы первого и второго элементов НЕ образуют группу выходов блока, первые входы первого и второго элементов ИЛИ соединены с синхронизирующим входом блока, а вторые входы - соответственно с входами сигналов вывода и ввода блока и первым и вторым входами элемента И-НЕ, выход которого является четвертым выходом блока, первый и второй входы

0

5

выходом олока. первый и второй входы „ ВЫХоД элемента ИЛИ-НЕ соединены со- ответственно с выходом второго триг- Гера, разрешающим входом блока и пер- Вым выходом блока.

ветственно вторым и третьим выходами блока, выходы первого и второго элементов ИЛИ соединены соответственно с входами первого и второго элементов НЕ и установочными входами первого и второго триггеров, информационные входы которых соединены с шиной нулевого потенциала устройства, выходы первого и второго элементов НЕ образуют группу выходов блока, первые входы первого и второго элементов ИЛИ соединены с синхронизирующим входом блока, а вторые входы - соответственно с входами сигналов вывода и ввода блока и первым и вторым входами элемента И-НЕ, выход которого является четвертым выходом блока, первый и второй входы

ЈJ Зп

M Cm A/D

-IX

Z

46 Подтв/3п5 -у

48 04МУ Y

SO Акт/ПАСС S

42 А/Я

52 STB

4-5 Чт

W Cm А/В

jL

Падтд/Эпб - W Offp.By

50 Акт/ШСС Г

Ј2 A/D

47 QBF

37 вывод

38

СИП

Фиг 2

SZ

Фиг.Э

К 3iz 45 Чт Л

обр.8у

50 Ант/паЈс

Ц Лодте/ТУ; 44 СпгА/2Г

W A/J}

39 СИ А

36 Ввод

17 Вывод

38 СИП

52 STB

№ А/Д

39 Ш

V

38 ВЫ

ЪТВыВод

ЪВСНП

51 STff

/

L

Фиг.Ь

LUjLL

Ь-

5

i

t

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-15—Публикация

1989-05-05—Подача