Изобретение относится к вычислительной технике и может быть использовано в устройствах преобразования и кодирования информации.

Целью изобретения является расширение области применения преобразователя за счет обеспечения циклического преобразования асинхронно изменяющегося во времени входного кода.

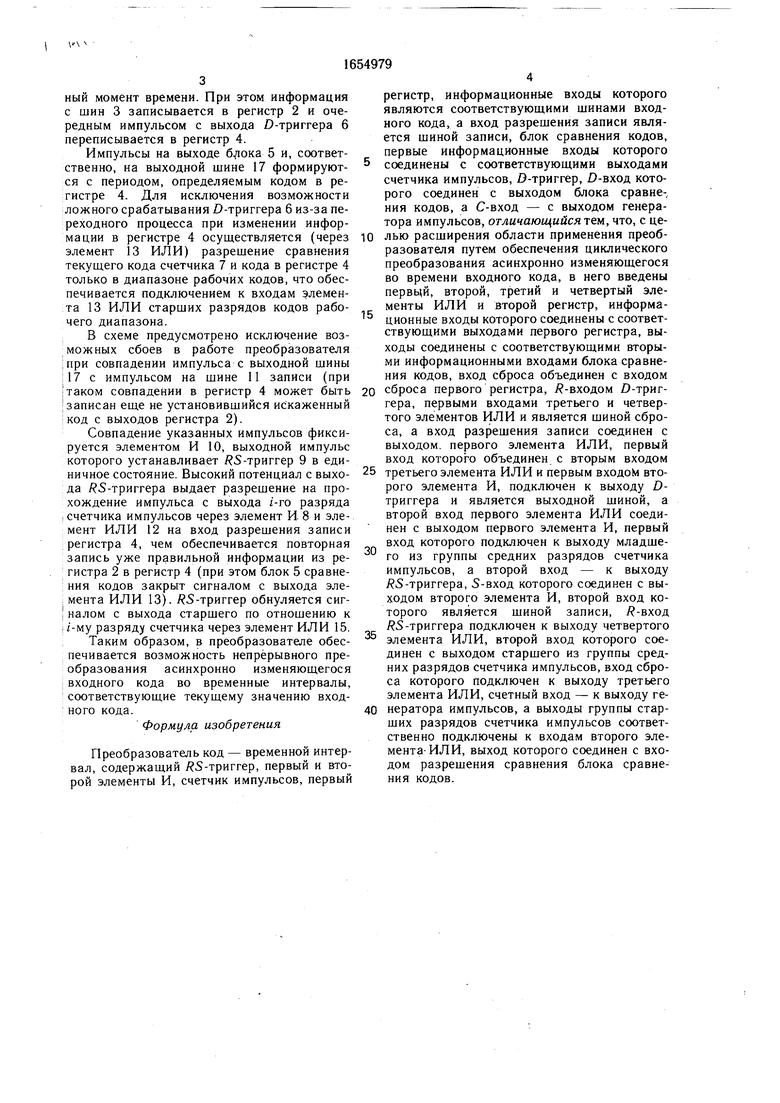

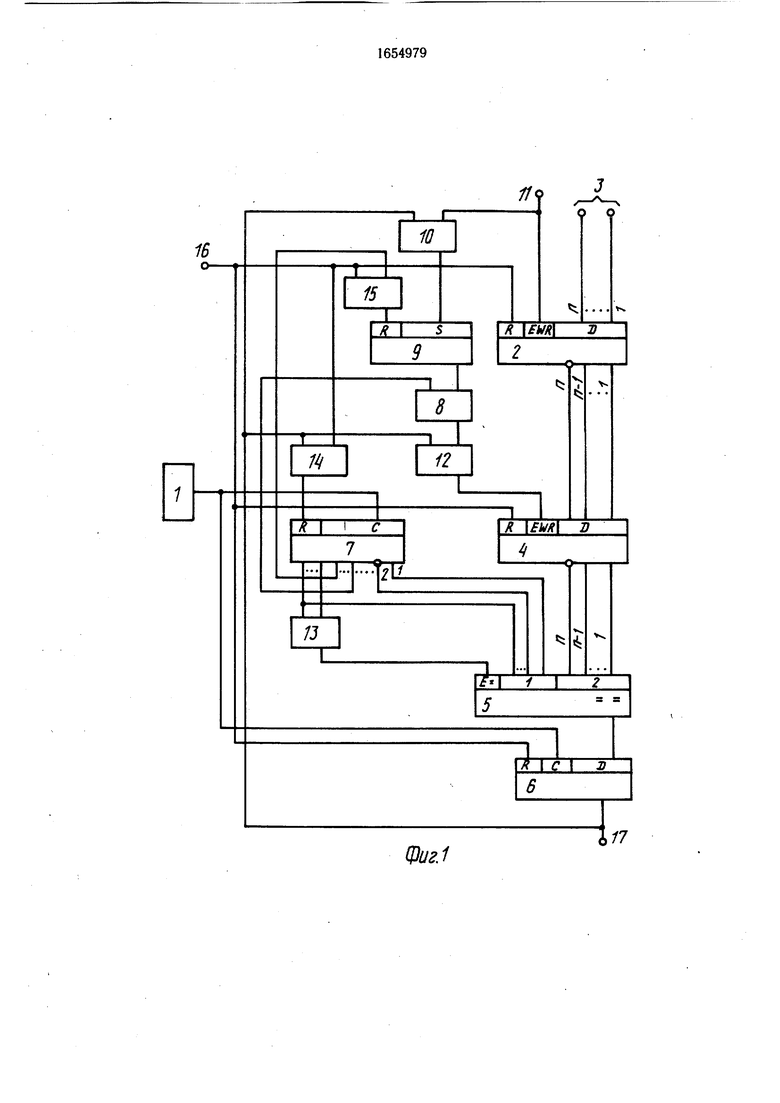

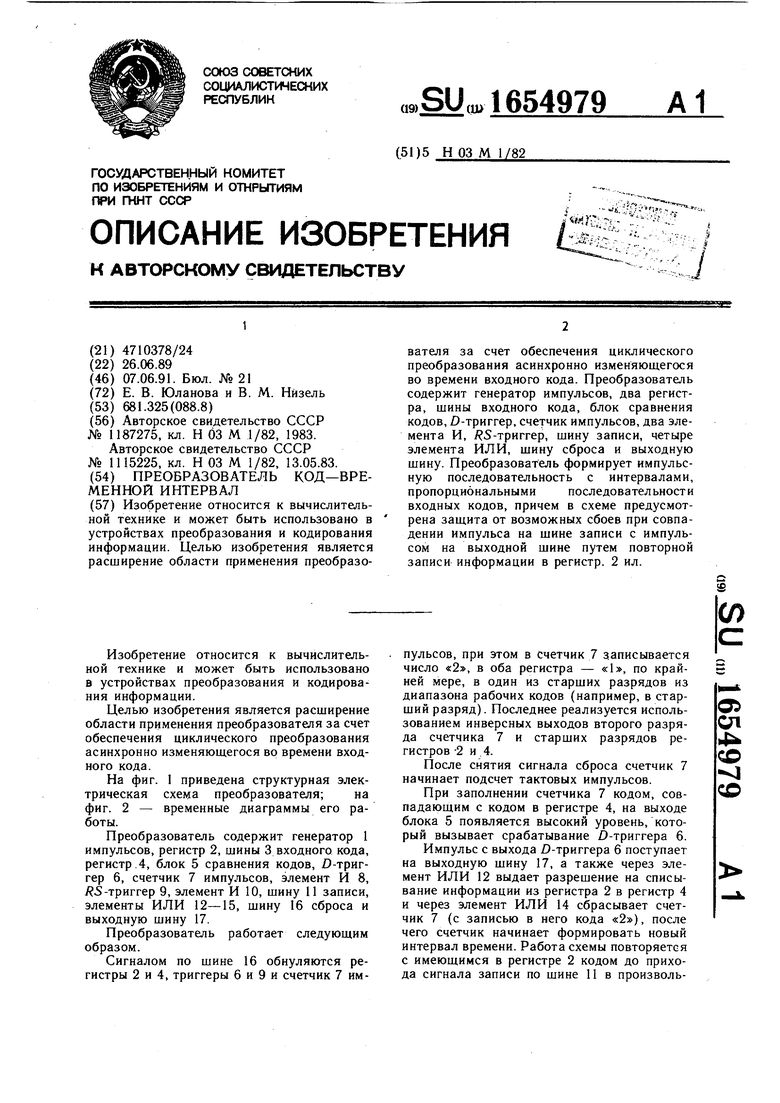

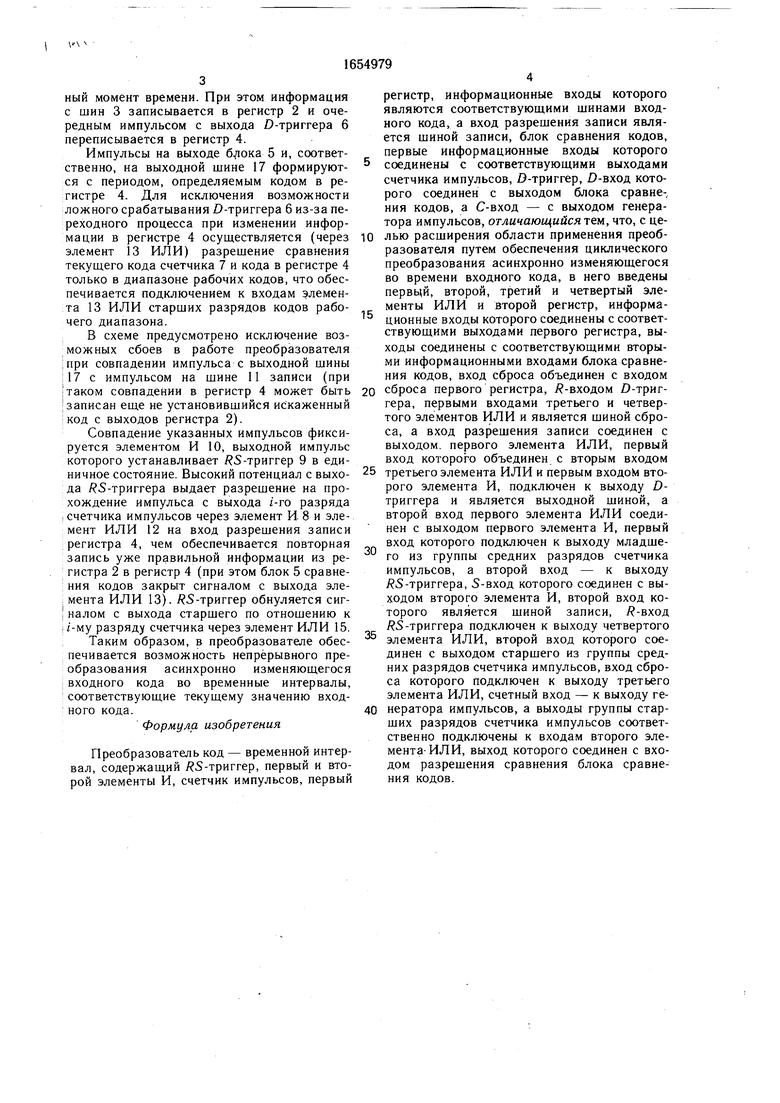

На фиг. 1 приведена структурная электрическая схема преобразователя; на фиг. 2 - временные диаграммы его работы.

Преобразователь содержит генератор 1 импульсов, регистр 2, шины 3 входного кода, регистр 4, блок 5 сравнения кодов, D-триг- гер 6, счетчик 7 импульсов, элемент И 8, / 5-триггер 9, элемент И 10, шину 11 записи, элементы ИЛИ 12-15, шину 16 сброса и выходную шину 17.

Преобразователь работает следующим образом.

Сигналом по шине 16 обнуляются регистры 2 и 4, триггеры 6 и 9 и счетчик 7 импульсов, при этом в счетчик 7 записывается число «2, в оба регистра - «1, по крайней мере, в один из старших разрядов из диапазона рабочих кодов (например, в старший разряд). Последнее реализуется использованием инверсных выходов второго разряда счетчика 7 и старших разрядов регистров -2 и 4.

После снятия сигнала сброса счетчик 7 начинает подсчет тактовых импульсов.

При заполнении счетчика 7 кодом, совпадающим с кодом в регистре 4, на выходе блока 5 появляется высокий уровень, который вызывает срабатывание Ј -триггера 6.

Импульс с выхода D-триггера 6 поступает на выходную шину 17, а также через элемент ИЛИ 12 выдает разрешение на списывание информации из регистра 2 в регистр 4 и через элемент ИЛИ 14 сбрасывает счетчик 7 (с записью в него кода «2), после чего счетчик начинает формировать новый интервал времени. Работа схемы повторяется с имеющимся в регистре 2 кодом до прихода сигнала записи по шине 11 в произвольоэел

4ъ

СО

|

со

ный момент времени. При этом информация с шин 3 записывается в регистр 2 и очередным импульсом с выхода D-триггера 6 переписывается в регистр 4.

Импульсы на выходе блока 5 и, соответственно, на выходной шине 17 формируются с периодом, определяемым кодом в регистре 4. Для исключения возможности ложного срабатывания D-триггера б из-за переходного процесса при изменении информации в регистре 4 осуществляется (через элемент 13 ИЛИ) разрешение сравнения текущего кода счетчика 7 и кода в регистре 4 только в диапазоне рабочих кодов, что обеспечивается подключением к входам элемента 13 ИЛИ старших разрядов кодов рабочего диапазона.

В схеме предусмотрено исключение возможных сбоев в работе преобразователя при совпадении импульса с выходной шины 17 с импульсом на шине 11 записи (при таком совпадении в регистр 4 может быть записан еще не установившийся искаженный код с выходов регистра 2).

Совпадение указанных импульсов фиксируется элементом И 10, выходной импульс которого устанавливает / 5-триггер 9 в единичное состояние. Высокий потенциал с выхода S-триггера выдает разрешение на прохождение импульса с выхода z -го разряда счетчика импульсов через элемент И 8 и элемент ИЛИ 12 на вход разрешения записи регистра 4, чем обеспечивается повторная запись уже правильной информации из регистра 2 в регистр 4 (при этом блок 5 сравнения кодов закрыт сигналом с выхода элемента ИЛИ 13). / 5-триггер обнуляется сиг- 1 налом с выхода старшего по отношению к /-му разряду счетчика через элемент ИЛИ 15

Таким образом, в преобразователе обеспечивается возможность непрерывного преобразования асинхронно изменяющегося входного кода во временные интервалы, соответствующие текущему значению входного кода.

Формула изобретения

Преобразователь код - временной интервал, содержащий / 5-триггер, первый и второй элементы И, счетчик импульсов, первый

регистр, информационные входы которого являются соответствующими шинами входного кода, а вход разрешения записи является шиной записи, блок сравнения кодов, первые информационные входы которого

соединены с соответствующими выходами счетчика импульсов, D-триггер, D-вход которого соединен с выходом блока сравнения кодов, а С-вход - с выходом генератора импульсов, отличающийсятем, что, с целью расширения области применения преобразователя путем обеспечения циклического преобразования асинхронно изменяющегося во времени входного кода, в него введены первый, второй, третий и четвертый элементы ИЛИ и второй регистр, информационные входы которого соединены с соответствующими выходами первого регистра, выходы соединены с соответствующими вторыми информационными входами блока сравнения кодов, вход сброса объединен с входом

0 сброса первого регистра, / -входом D-триггера, первыми входами третьего и четвертого элементов ИЛИ и является шиной сброса, а вход разрешения записи соединен с выходом первого элемента ИЛИ, первый вход которого объединен с вторым входом

5 третьего элемента ИЛИ и первым входом второго элемента И, подключен к выходу D- триггера и является выходной шиной, а второй вход первого элемента ИЛИ соединен с выходом первого элемента И, первый вход которого подключен к выходу младшего из группы средних разрядов счетчика импульсов, а второй вход - к выходу У 5-триггера, S-вход которого соединен с выходом второго элемента И, второй вход которого является шиной записи, #-вход RS-триггера подключен к выходу четвертого

5 элемента ИЛИ, второй вход которого соединен с выходом старшего из группы средних разрядов счетчика импульсов, вход сброса которого подключен к выходу третьего элемента ИЛИ, счетный вход - к выходу ге0 нератора импульсов, а выходы группы старших разрядов счетчика импульсов соответственно подключены к входам второго элемента ИЛИ, выход которого соединен с входом разрешения сравнения блока сравнения кодов.

0

Фиг.1

17

/ oSif

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Преобразователь код-временной интервал | 1985 |

|

SU1305865A1 |

| Преобразователь код-момент времени | 1981 |

|

SU970685A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах преобразования и кодирования информации. Целью изобретения является расширение области применения преобразователя за счет обеспечения циклического преобразования асинхронно изменяющегося во времени входного кода. Преобразователь содержит генератор импульсов, два регистра, шины входного кода, блок сравнения кодов, D-триггер, счетчик импульсов, два элемента И, / 5-триггер, шину записи, четыре элемента ИЛИ, шину сброса и выходную шину. Преобразователь формирует импульсную последовательность с интервалами, пропорциональными последовательности входных кодов, причем в схеме предусмотрена защита от возможных сбоев при совпадении импульса на шине записи с импульсом на выходной шине путем повторной записи информации в регистр. 2 ил.

U

XG$/JO

tf W ,tf)

Фиг

Ko9f/t

КодЯ MoWS

П П

| Авторское свидетельство СССР № 1187275, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь код-временной интервал | 1983 |

|

SU1115225A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-06-07—Публикация

1989-06-26—Подача