w

Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1992 |

|

RU2060538C1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| Система коммутации | 1986 |

|

SU1359783A1 |

Изобретение относится к вычислительной технике и может быть использовано для адресации памяти многопроцессорных вычислительных комплексов. Целью изобретения является расширение функциональных возможностей за счет формирования логических адресов переменной структуры. Устройство содержит группу переключателей 1, группу шифраторов 2, группу мультиплексоров 3, группу сумматоров 4, группу регистров 5. группу входных коммутаторов 6,

сь ел а

СП

со

группу схем сравнения 7, выходной коммутатор 8, счетчик 9, элемент ИЛИ 10, мультиИзобретение относится к вычислительной технике и может быть использовано для адресации памяти многопроцессорных вычислительных комплексов.

Целью изобретения является расширение функциональных возможностей путем формирования логических адресов переменной структуры.

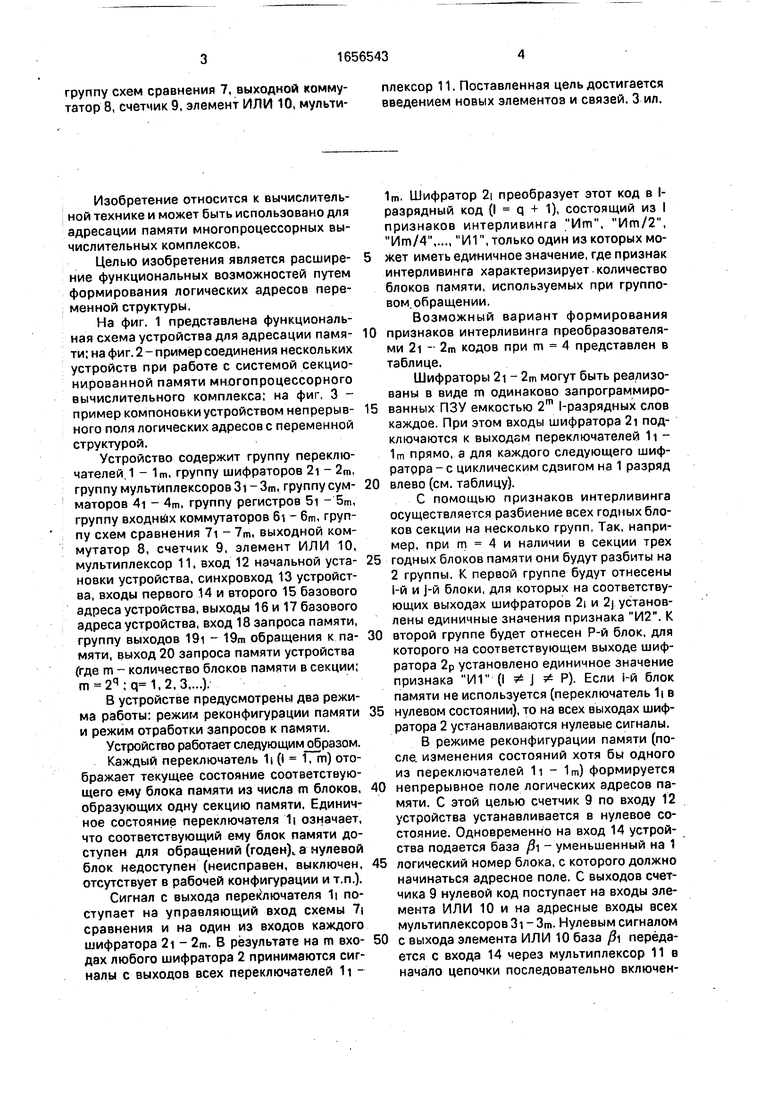

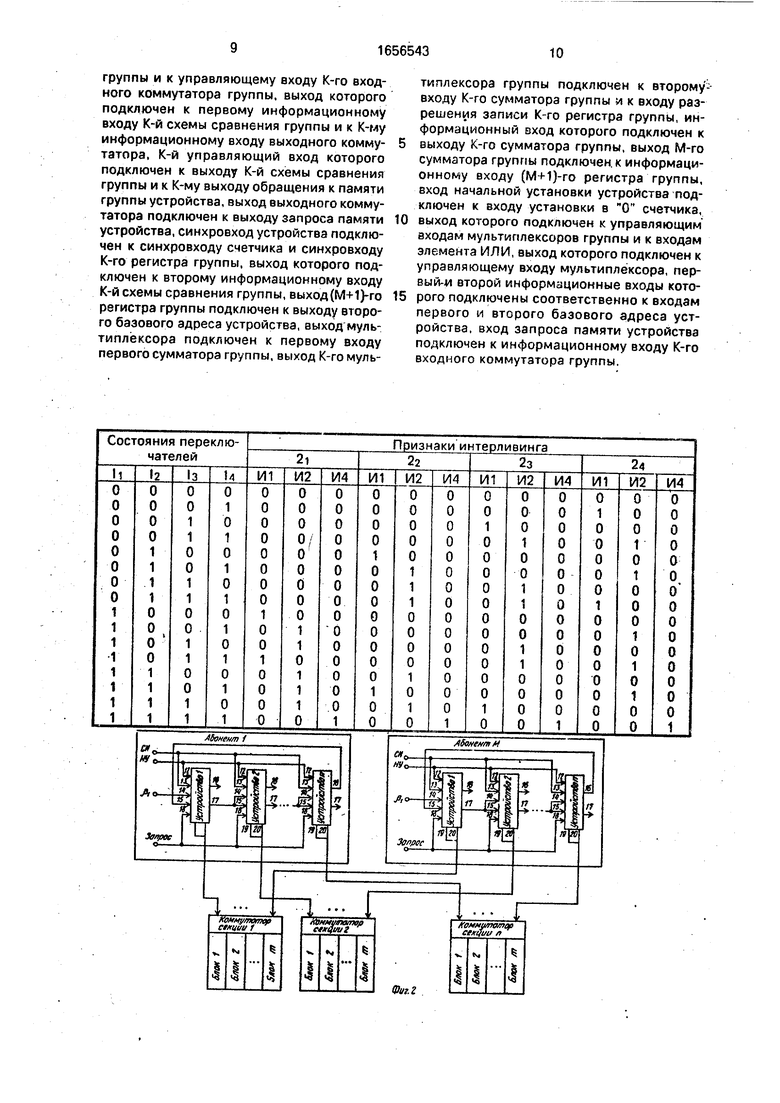

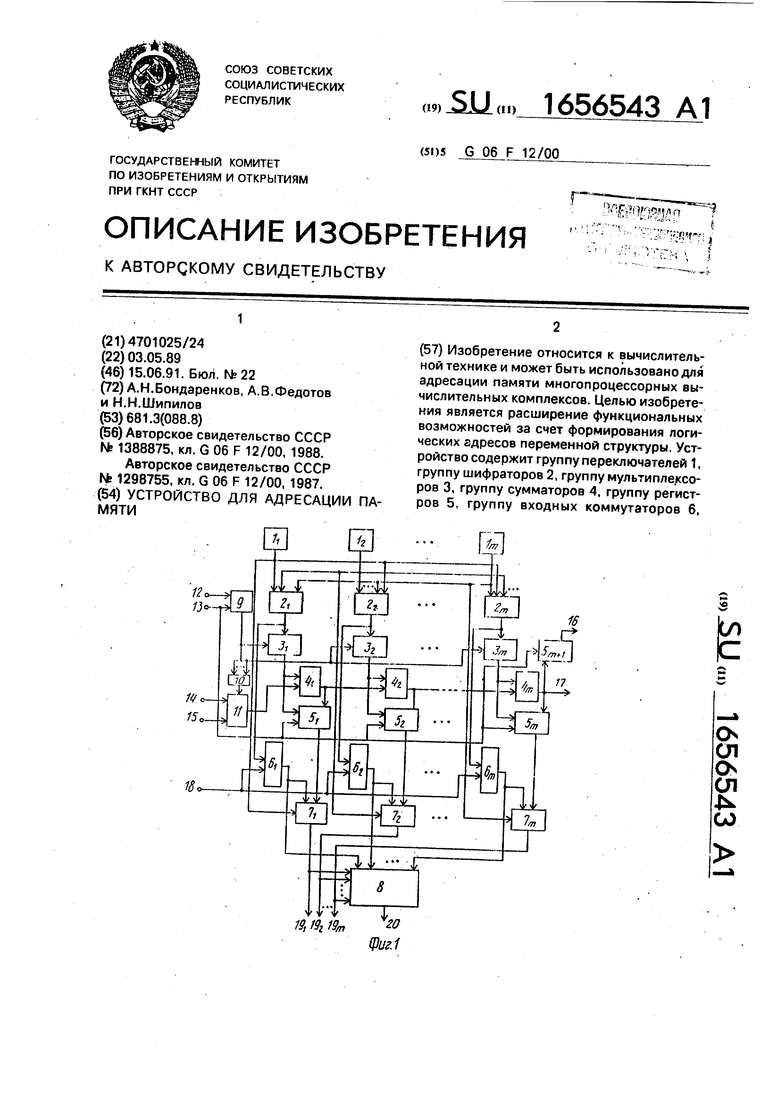

На фиг. 1 представлена функциональная схема устройства для адресации памяти; на фиг. 2 - пример соединения нескольких устройств при работе с системой секционированной памяти многопроцессорного вычислительного комплекса; на фиг, 3 - пример компоноьки устройством непрерывного поля логических адресов с переменной структурой.

Устройство содержит группу переключателей, 1 - 1т, группу шифраторов 2i - 2m, группу мультиплексоров 3i 3m. группу сумматоров 4ч - 4т, группу регистров 5i - 5m, группу входных коммутаторов 61 - 6m, группу схем сравнения 7i - 7m. выходной коммутатор 8, счетчик 9, элемент ИЛИ 10, мультиплексор 11, вход 12 начальной установки устройства, синхровход 13 устройства, входы первого 14 и второго 15 базового адреса устройства, выходы 16 и 17 базового адреса устройства, вход 18 запроса памяти, группу выходов 19i - 19m обращения к памяти, выход 20 запроса памяти устройства (где m - количество блоков памяти в секции; m 2q;q 1,2,3,...).

В устройстве предусмотрены два режима работы: режим реконфигурации памяти и режим отработки запросов к памяти.

Устройство работает следующим образом.

Каждый переключатель 1i (J 1, т) отображает текущее состояние соответствующего ему блока памяти из числа m блоков, образующих одну секцию памяти. Единичное состояние переключателя 1i означает, что соответствующий ему блок памяти доступен для обращений (годен), а нулевой блок недоступен (неисправен, выключен, отсутствует в рабочей конфигурации и т.п.).

Сигнал с выхода переключателя 1| поступает на управляющий вход схемы 7| сравнения и на один из входов каждого шифратора 2i - 2m. В результате на m входах любого шифратора 2 принимаются сигналы с выходов всех переключателей 1i плексор 11, Поставленная цель достигается введением новых элементов и связей. 3 ил,

1m. Шифратор 2| преобразует этот код в I- разрядный код (I q + 1), состоящий из I признаков интерливинга Ит, Ит/2, Ит/4,..., И1, только один из которых может иметь единичное значение, где признак интерливинга характеризирует количество блоков памяти, используемых при групповом обращении,

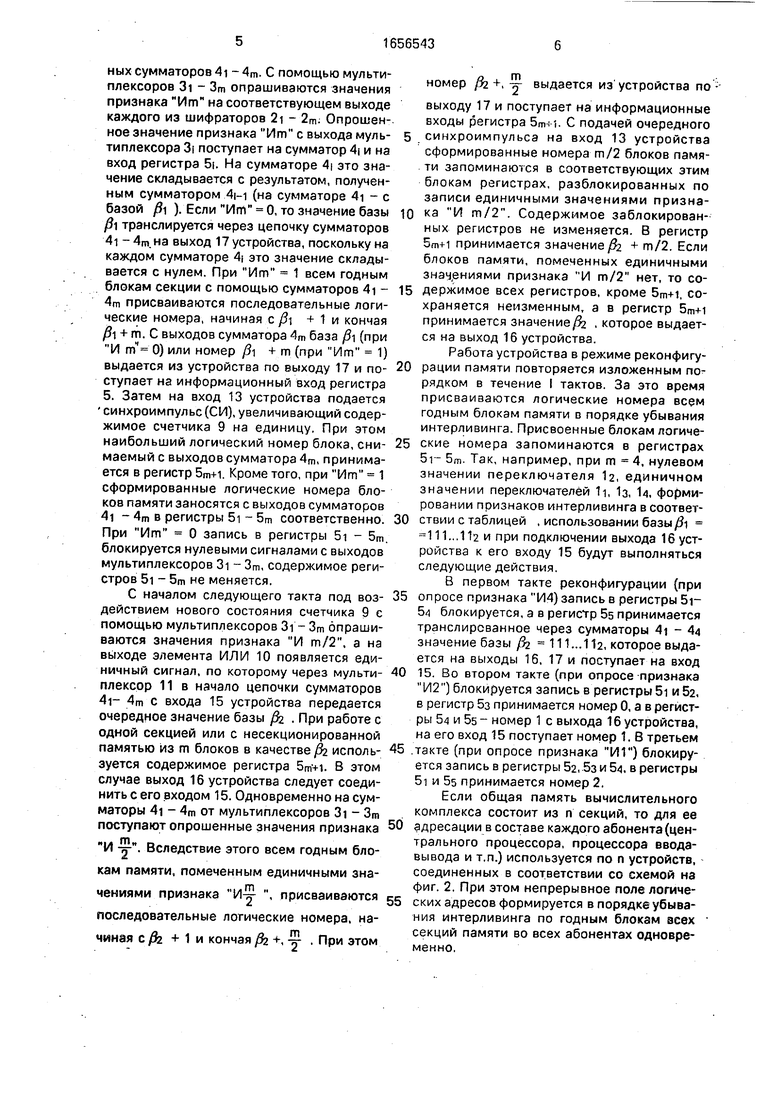

Возможный вариант формирования

признаков интерливинга преобразователями 2i - 2m кодов при m 4 представлен в таблице.

Шифраторы 2i - 2т могут быть реализованы в виде m одинаково запрограммированных ПЗУ емкостью 2т 1-разрядных слов каждое. При этом входы шифратора 2i подключаются к выходам переключателей 1i - 1m прямо, а для каждого следующего шифратора - с циклическим сдвигом на 1 разряд

влево (см. таблицу).

С помощью признаков интерливинга осуществляется разбиение всех годных блоков секции на несколько групп. Так, например, при m 4 и наличии в секции трех

годных блоков памяти они будут разбиты на 2 группы. К первой группе будут отнесены 1-й и j-й блоки, для которых на соответствующих выходах шифраторов 1 и 2j установлены единичные значения признака И2. К

второй группе будет отнесен Р-й блок, для которого на соответствующем выходе шифратора 2Р установлено единичное значение признака И1 (i J Р). Если 1-й блок памяти не используется (переключатель 1| в

нулевом состоянии), то на всех выходах шифратора 2 устанавливаются нулевые сигналы. В режиме реконфигурации памяти (после, изменения состояний хотя бы одного из переключателей 1i - 1m) формируется

непрерывное поле логических адресов памяти. С этой целью счетчик 9 по входу 12 устройства устанавливается в нулевое состояние. Одновременно на вход 14 устройства подается база - уменьшенный на 1

логический номер блока, с которого должно начинаться адресное поле. С выходов счетчика 9 нулевой код поступает на входы элемента ИЛИ 10 и на адресные входы всех мультиплексоров 31 - 3m. Нулевым сигналом

с выхода элемента ИЛИ 10 база передается с входа 14 через мультиплексор 11 в начало цепочки последовательно включенных сумматоров 4i - 4m. С помощью мультиплексоров 3i - 3m опрашиваются значения признака Игл на соответствующем выходе каждого из шифраторов 2i - 2m. Опрошенное значение признака Ит с выхода муль- типлексора 3i поступает на сумматор 4 и на вход регистра 5i. На сумматоре 4| это значение складывается с результатом, полученным сумматором 4ы (на сумматоре 4i - с базой ). Если Ит 0. то значение базы fa транслируется через цепочку сумматоров 4i - 4m.на выход 17 устройства, поскольку на каждом сумматоре 4| это значение складывается с нулем. При Ит 1 всем годным блокам секции с помощью сумматоров 4i - 4m присваиваются последовательные логические номера, начиная с + 1 и кончая + т. С выходов сумматора 4т база /5i (при И т 0) или номер + т (при Ит 1) выдается из устройства по выходу 17 и по- ступает на информационный вход регистра 5. Затем на вход 13 устройства подается синхроимпульс (СИ), увеличивающий содержимое счетчика 9 на единицу. При этом наибольший логический номер блока, сни- маемый с выходов сумматора 4т, принимается в регистр 5m+i. Кроме того, при Ит 1 сформированные логические номера блоков памяти заносятся с выходов сумматоров 4i - 4m в регистры 61 - 5m соответственно. При Ит 0 запись в регистры 5i - 5m блокируется нулевыми сигналами с выходов мультиплексоров 3i - 3m, содержимое регистров 5i - 5m не меняется.

С началом следующего такта под воз- действием нового состояния счетчика 9 с помощью мультиплексоров 3i - 3m опрашиваются значения признака И т/2, а на выходе элемента ИЛИ 10 появляется единичный сигнал, по которому через мульти- плексор 11 в начало цепочки сумматоров 4i- 4m с входа 15 устройства передается очередное значение базы Др . При работе с одной секцией или с несекционированной памятью из m блоков в качестве/ используется содержимое регистра 5т+1. В этом случае выход 16 устройства следует соединить с его входом 15. Одновременно на сумматоры 4i - 4m от мультиплексоров 3i - 3m поступают опрошенные значения признака

И у. Вследствие этого всем годным блокам памяти, помеченным единичными значениями признака Иу , присваиваются

последовательные логические номера, начиная с fa + 1 и кончая fa ч-, у . При этом

5 ю 15 0 5 0

5 0

§

5

0

номер fh +, у выдается из устройства по

выходу 17 и поступает на информационные входы регистра 5тп. С подачей очередного синхроимпульса на вход 13 устройства сформированные номера т/2 блоков памяти запоминаются в соответствующих этим блокам регистрах, разблокированных по записи единичными значениями признака И т/2. Содержимое заблокированных регистров не изменяется. В регистр 5™+ принимается значение/% + т/2. Если блоков памяти, помеченных единичными значениями признака И т/2 нет, то содержимое всех регистров, кроме 5m+i. сохраняется неизменным, а в регистр 5т-м принимается значение/ . которое выдается на выход 16 устройства.

Работа устройства в режиме реконфигурации памяти повторяется изложенным порядком в течение I тактов. За это время присваиваются логические номера всем годным блокам памяти о порядке убывания интерливинга. Присвоенные блокам логические номера запоминаются в регистрах 5i- 5m. Так, например, при m 4, нулевом значении переключателя 12, единичном значении переключателей 1i, 1з, 14, формировании признаков интерливинга в соответствии с таблицей , использовании базы 111..,112 и при подключении выхода 16 устройства к его входу 15 будут выполняться следующие действия.

В первом такте реконфигурации (при опросе признака И4) запись в регистры 5i блокируется, а в регистр 5s принимается транслированное через сумматоры 4i - 44 значение базы /% 111...112, которое выдается на выходы 16, 17 и поступает на вход 15. Во втором такте (при опросе признака И2) блокируется запись в регистры 5i и 52, в регистр 5з принимается номер 0, а в регистры 54 и 5s - номер 1 с выхода 16 устройства, на его вход 15 поступает номер 1. В третьем такте (при опросе признака И1) блокируется запись в регистры 52,5з и 54, в регистры 5i и 5s принимается номер 2.

Если общая память вычислительного комплекса состоит из п секций, то для ее адресации в составе каждого абонента (центрального процессора, процессора ввода- вывода и т.п.) используется по п устройств, соединенных в соответствии со схемой на фиг. 2. При этом непрерывное поле логических адресов формируется в порядке убывания интерливинга по годным блокам всех секций памяти во всех абонентах одновременно.

В режиме отработки запросов к памяти подача синхроимпульсов на вход 13 устройства не производится и содержимое всех регистров 5i - 5m+i сохраняется неизменным. На вход 18 подается слово текущего запроса к памяти. В состав этого слова входит полный логический адрес ячейки памяти, а также признаки, характеризующие тип запроса (одиночный или групповой), режим обращения к памяти (запись, считывание, семафорное считывание,...) и т.п.

Непрерывное поле логических адресов, сформированное устройством в режиме реконфигурации памяти, состоит из нескольких участков, упорядоченных по убыванию их длин. На участке длиной 2 V6 (/б - объем одного блока памяти) обеспечивается интерливинг И2К, где К 0, 1, 2,...q. Структура логического адреса, принадлежащего такому участку, поясняется примером на фиг. 3, где показано непрерывное адресное поле, состоящее из трех участков с интерли- вингами И4, И2 и И1 соответственно. Для участка с интерливингом И2 х логический номер блока памяти задается (одапмакс + q - К старшими и К младшими разрядами адреса (пмакс - максимальное число секций в заданной системе памяти), а остальные разряды адреса задают порядковый номер ячейки в блоке памяти. Таким образом, полный логический номер любого блока памяти состоит в общем случае из двух переменных полей адреса. При этом границы полей однозначно определяются признаком интерливинга, которым помечен данный блок памяти. С учетом этого отработка запросов к памяти выполняется устройством следующим образом.

С входа 18 слово текущего запроса поступает на информационные входы всех коммутаторов 61 - 6m. На управляющие входы каждого коммутатора 61 с выходов шифратора 2i поступают признаки интерливинга 1-го блока памяти. Под воздействием единичного значения одного из признаков И2К коммутатором 6i выбираются разряды логического адреса, задающие полный логический номер блока памяти. Выделенный номер сравнивается в схеме 7 с содержимым регистра 5i, т.е. с логическим номером, который был ранее присвоем 1-му

блоку памяти. Остальные разряды слова текущего запроса, в том числе и разряды, образующие номер ячейки внутри блока памяти, поступают на 1-е информационные входы коммутатора 8. При совпадении логического номера, выделенного из слова текущего запроса, с номером, присвоенным 1-му блоку памяти, на выходе схемы 7| формируется единичный сигнал. Сравнение производится однозременно по всем годным

блокам памяти, т.е. всеми элементами 7i - 7m, на управляющие входы которых поступают единичные сигналы. Совпадение номеров фиксируется только схемой 7|. С

выхода схемы 7| единичный сигнал выдается на выход 19 устройства, откуда поступает в секцию памяти и свидетельствует об обращении к ее l-му блоку. Одновременно этот же сигнал поступает на один из управляющих входов коммутатора 8 и обеспечивает выдачу в систему памяти той части слова текущего запроса, которая была выделена коммутатором 6i и подавалась на i-e информационные входы коммутатора 8. Таким образом, на выходе 19i появляется единичный сигнал обращения к l-му блоку той секции памяти, которая обслуживается устройством (фиг. 2). Одновременно по выходам 20 выдается слово запроса к i-му блоку памяти

(номер N ячейки внутри блока и необходимые признаки). Сигнал обращения к блоку памяти и слово запроса поступают на входы коммутатора обслуживаемой секции (фиг. 2). При отсутствии обращений к тому же Олоку

со стороны более приоритетных абонентов и незанятости этого блока он запускается на отработку запроса, а запросчику от коммутатора секции выдается подтверждение о приеме запроса (связи, необходимые для

подтверждения, и числовые шины к описываемому устройству не относятся и на фиг. 2 не показаны). В следующем такте на входе 18 устройства появляется очередное слово запроса к памяти, и работа устройства повторяется изложенным порядком.

Формула изобретения Устройство для адресации памяти, содержащее группу сумматоров и группу схем

сравнения, причем К-й вход признака доступности блока памяти группы устройства подключен к стробирующему входу К-й схемы сравнения, К 1 М, где М - количество блоков памяти в секции, выход Р-го сумматора группы подключен к первому входу (Р+1)-го сумматора группы, (Р 1, М-1), выход М-го сумматора группы подключен к выходу первого базового адреса устройства, отличающееся тем. что, с целью

расширения функциональных возможностей путем формирования логических адресов переменной структуры, в него введены группа шифраторов, группа мультиплексоров, группа регистров, группа входных коммутаторов, счетчик, элемент ИЛИ, мультиплексор и выходной коммутатор, причем входы признака доступности блока памяти группы подключены к входам К-го шифратора группы, выход которого подключен к информационным входам К-го мультиплексора

группы и к управляющему входу К-го входного коммутатора группы, выход которого подключен к первому информационному входу К-й схемы сравнения группы и к К-му информационному входу выходного коммутатора, К-й управляющий вход которого подключен к выходу К-й схемы сравнения группы и к К-му выходу обращения к памяти группы устройства, выход выходного коммутатора подключен к выходу запроса памяти устройства, синхровход устройства подключен к синхровходу счетчика и синхровходу К-го регистра группы, выход которого подключен к второму информационному входу К-й схемы сравнения группы, выход (М+1)-го регистра группы подключен к выходу второго базового адреса устройства, выход мультиплексора подключен к первому входу первого сумматора группы, выход К-го муль

типлексора группы подключен к второму- входу К-го сумматора группы и к входу разрешения записи К-го регистра группы, информационный вход которого подключен к

выходу К-го сумматора группы, выход М-го сумматора группы подключен к информационному входу (МИ)-го регистра группы, вход начальной установки устройства подключен к входу установки в О счетчика,

выход которого подключен к управляющим входам мультиплексоров группы и к входам элемента ИЛИ, выход которого подключен к управляющему входу мультиплексора, пер- вый-м второй информационные входы которого подключены соответственно к входам первого и второго базового адреса устройства, вход запроса памяти устройства подключен к информационному входу К-го входного коммутатора группы.

Логический номер 5лока

/

о 1

2

3 О

3

о

1

2 5

4 5

5 4 5 6

I

| Устройство для адресации блоков памяти | 1986 |

|

SU1388875A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для адресации памяти | 1985 |

|

SU1298755A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-15—Публикация

1989-05-03—Подача