Л7ес/77ирсЈэния

Фиг1

Изобретение относится к импульсной технике и может быть использовано в амплитудных анализаторах, например, в ядерных спектрометрических исследованиях на автоматических необслуживаемых измерительных комплексах, к которым предъявляют требование высокой надежности.

Цель изобретения - повышение надежности анализатора.

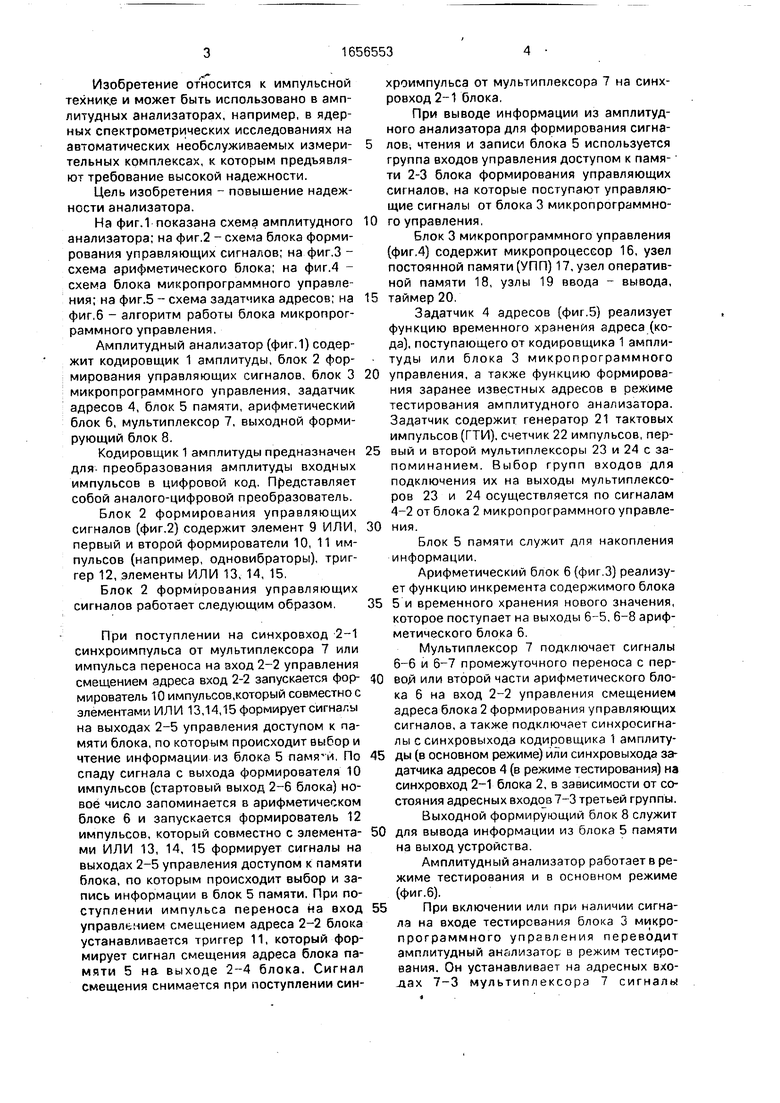

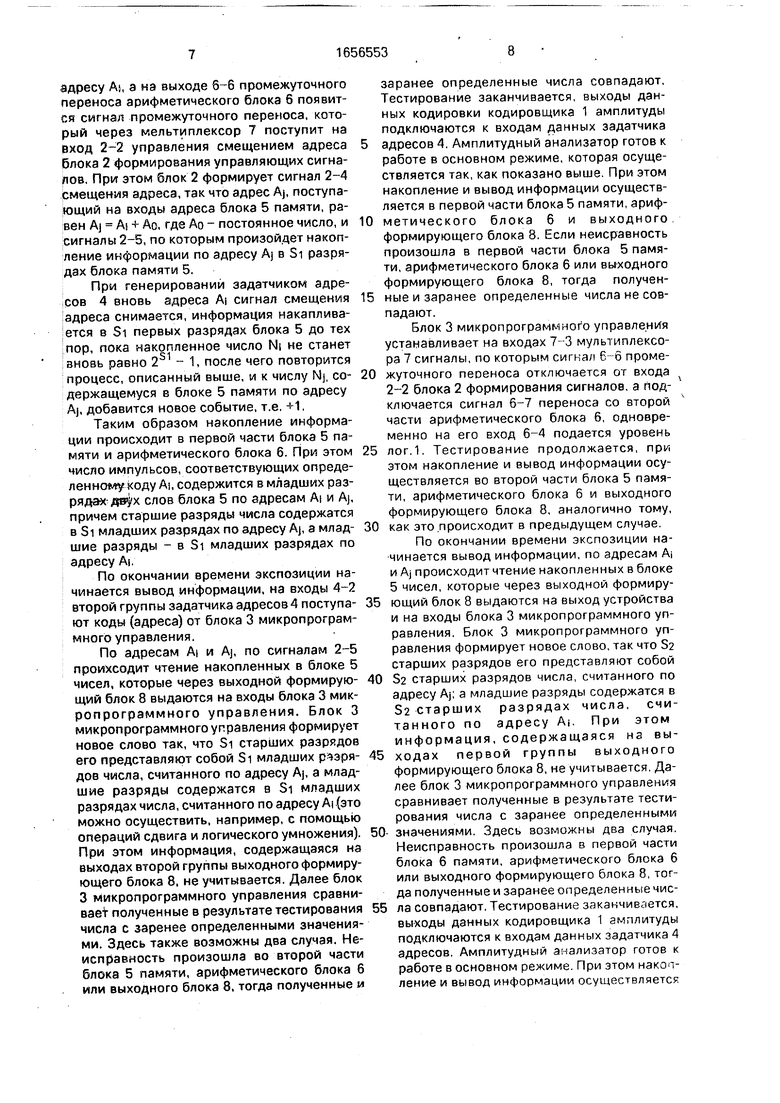

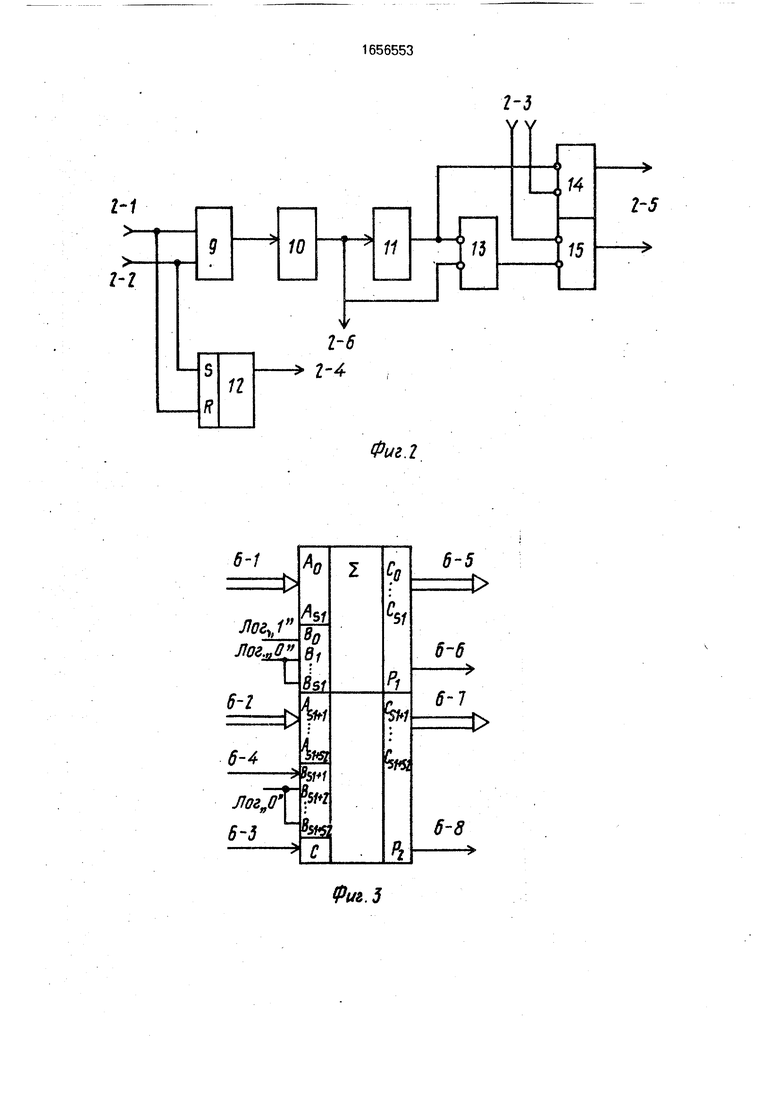

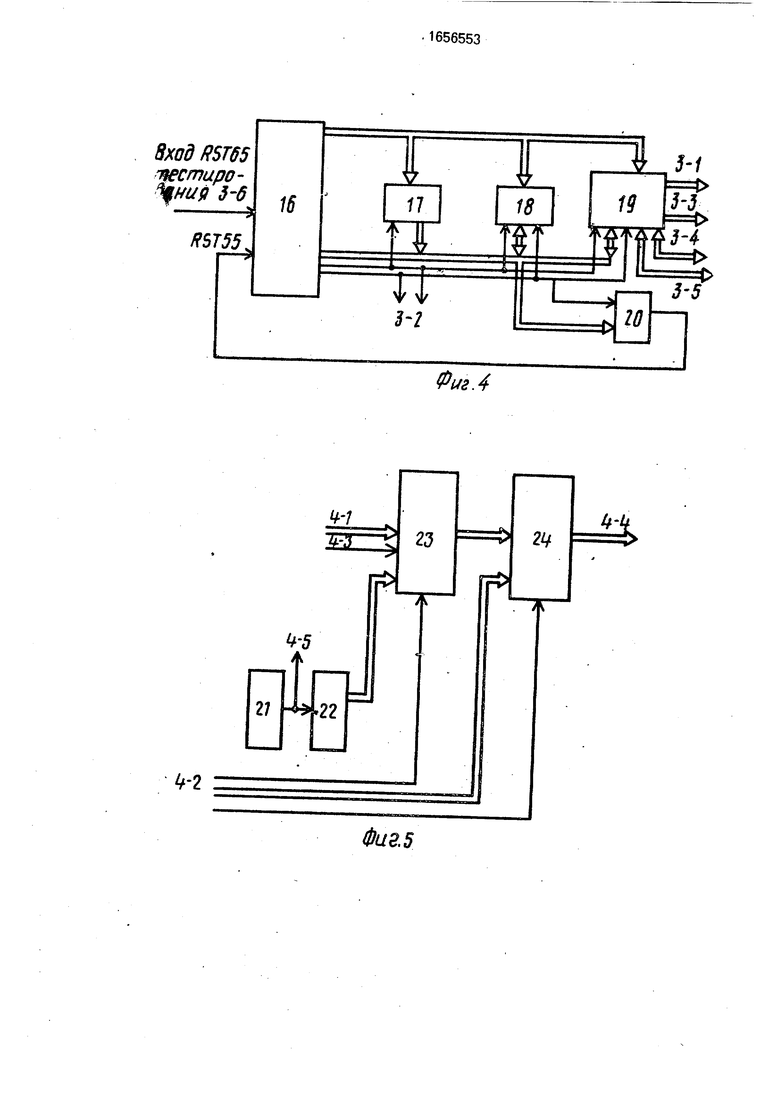

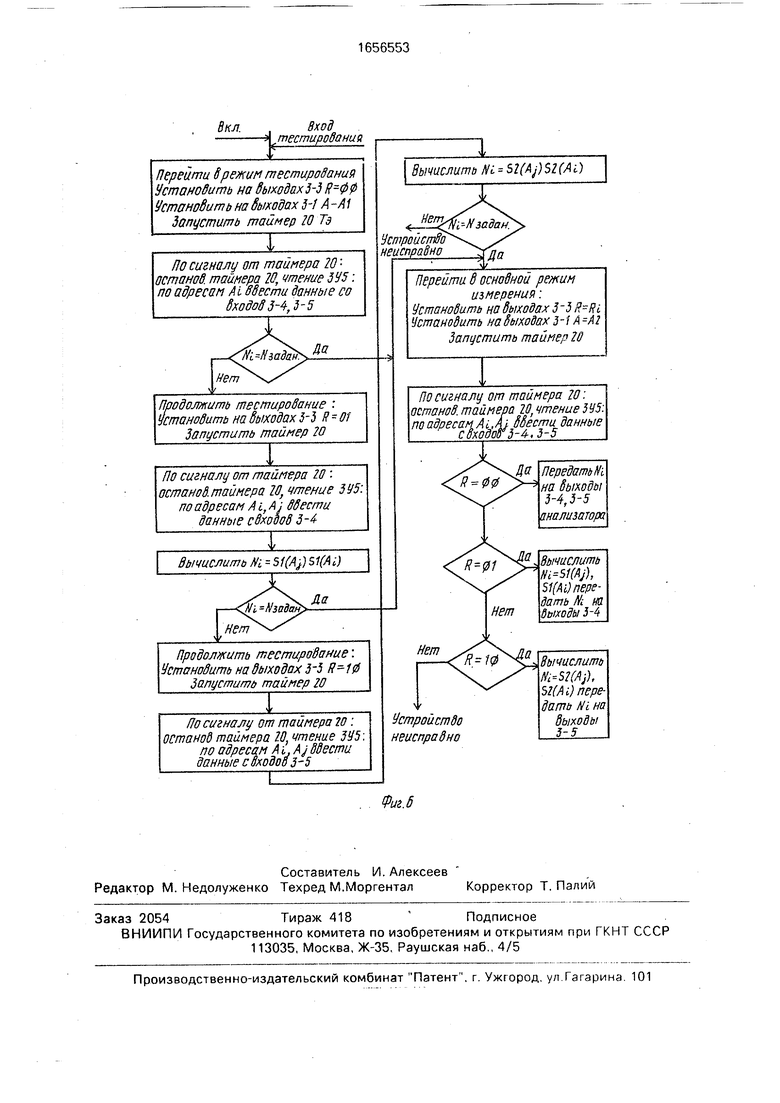

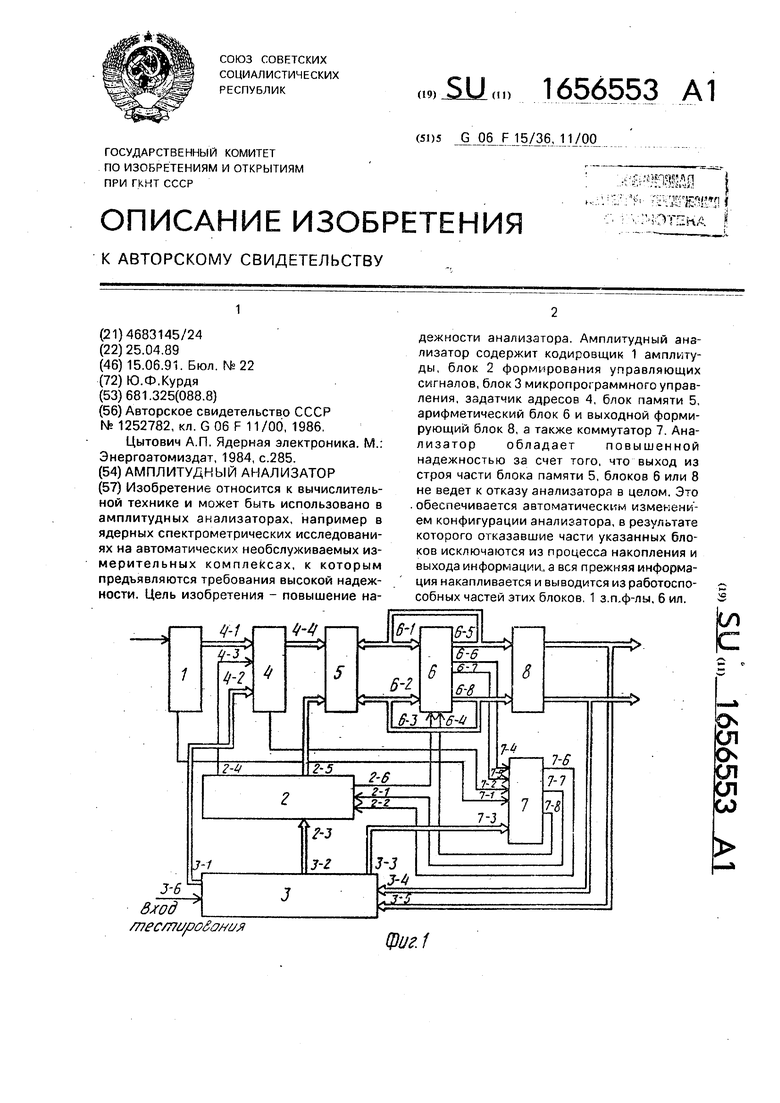

На фиг.1 показана схема амплитудного анализатора; на фиг.2 - схема блока формирования управляющих сигналов; на фиг.З - схема арифметического блока; на фиг.4 - схема блока микропрограммного управления; на фиг.5 - схема задатчика адресов; на фиг.6 - алгоритм работы блока микропрограммного управления.

Амплитудный анализатор (фиг.1) содержит кодировщик 1 амплитуды, блок 2 формирования управляющих сигналов, блок 3 микропрограммного управления, задатчик адресов 4, блок 5 памяти, арифметический блок 6, мультиплексор 7. выходной формирующий блок 8.

Кодировщик 1 амплитуды предназначен для преобразования амплитуды входных импульсов в цифровой код. Представляет собой аналого-цифровой преобразователь.

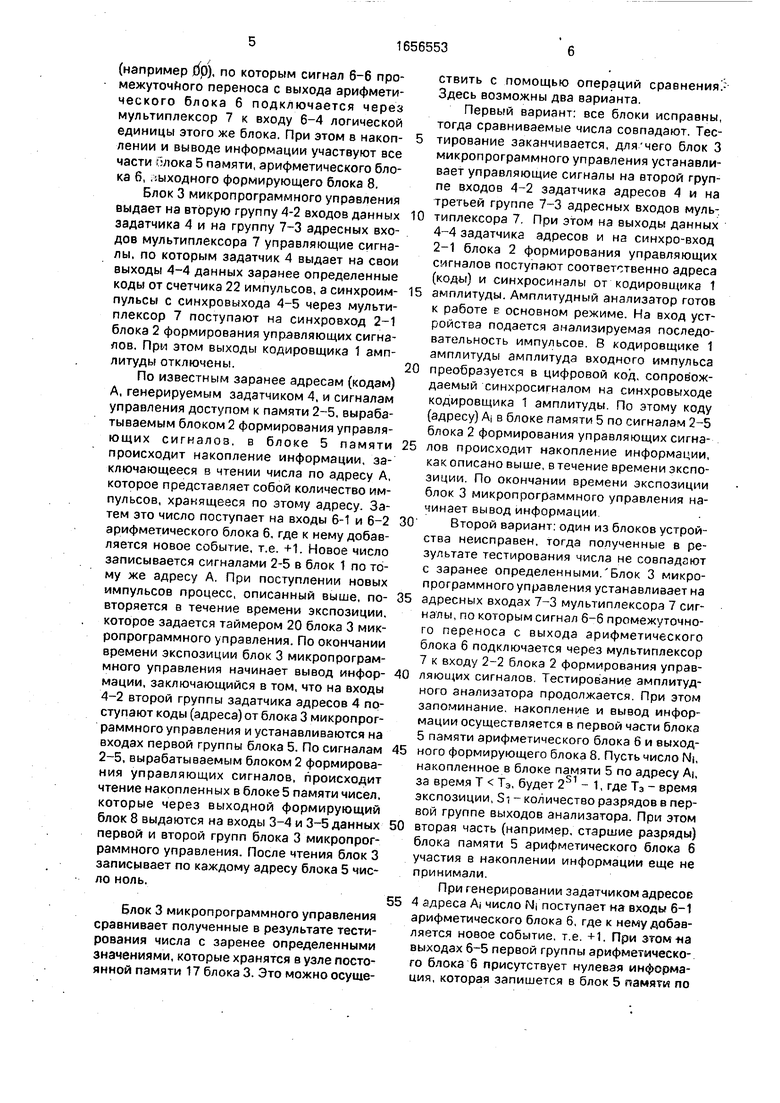

Блок 2 формирования управляющих сигналов (фиг.2) содержит элемент 9 ИЛИ, первый и второй формирователи 10, 11 импульсов (например, одновибраторы). триггер 12, элементы ИЛИ 13, 14, 15.

Блок 2 формирования управляющих сигналов работает следующим образом.

При поступлении на синхровход 2-1 синхроимпульса от мультиплексора 7 или импульса переноса на вход 2-2 управления смещением адреса вход 2-2 запускается формирователь 10 импульсов.который совместно с элементами ИЛИ 13,14,15 формирует сигналы на выходах 2-5 управления доступом к памяти блока, по которым происходит выбор и чтение информации из блока 5 памяти. По спаду сигнала с выхода формирователя 10 импульсов (стартовый выход 2-6 блока) новое число запоминается в арифметическом блоке 6 и запускается формирователь 12 импульсов, который совместно с элементами ИЛИ 13, 14, 15 формирует сигналы на выходах 2-5 управления доступом к памяти блока, по которым происходит выбор и запись информации в блок 5 памяти. При поступлении импульса переноса на вход управлением смещением адреса 2-2 блока устанавливается триггер 11, который формирует сигнал смещения адреса блока памяти 5 на выходе 2-4 блока. Сигнал смещения снимается при поступлении синхроимпульса от мультиплексора 7 на синхровход 2-1 блока,

При выводе информации из амплитудного анализатора для формирования сигналов, чтения и записи блока 5 используется группа входов управления доступом к памяти 2-3 блока формирования управляющих сигналов, на которые поступают управляющие сигналы от блока 3 микропрограммно0 го управления.

Блок 3 микропрограммного управления (фиг.4) содержит микропроцессор 16, узел постоянной памяти (УПП) 17, узел оперативной памяти 18, узлы 19 ввода - вывода,

5 таймер 20.

Задатчик 4 адресов (фиг.5) реализует функцию временного хранения адреса (кода), поступающего от кодировщика 1 амплитуды или блока 3 микропрограммного

0 управления, а также функцию формирования заранее известных адресов в режиме тестирования амплитудного анализатора. Задатчик содержит генератор 21 тактовых импульсов (ГТИ), счетчик 22 импульсов, пер5 вый и второй мультиплексоры 23 и 24 с запоминанием. Выбор групп входов для подключения их на выходы мультиплексоров 23 и 24 осуществляется по сигналам 4-2 от блока 2 микропрограммного управле0 ния.

Блок 5 памяти служит для накопления информации.

Арифметический блок 6 (фиг.З) реализует функцию инкремента содержимого блока

5 5 и временного хранения нового значения, которое поступает на выходы 6- 5. 6-8 арифметического блока 6.

Мультиплексор 7 подключает сигналы 6-6 и 6-7 промежуточного переноса с пер0 вой или второй части арифметического блока 6 на вход 2-2 управления смещением адреса блока 2 формирования управляющих сигналов, а также подключает синхросигналы с синхровыхода кодировщика 1 амплиту5 ды (в основном режиме) или синхровыхода задатчика адресов 4 (в режиме тестирования) на синхровход 2-1 блока 2, в зависимости от состояния адресных входов 7-3 третьей группы. Выходной формирующий блок 8 служит

0 для вывода информации из блока 5 памяти на выход устройства.

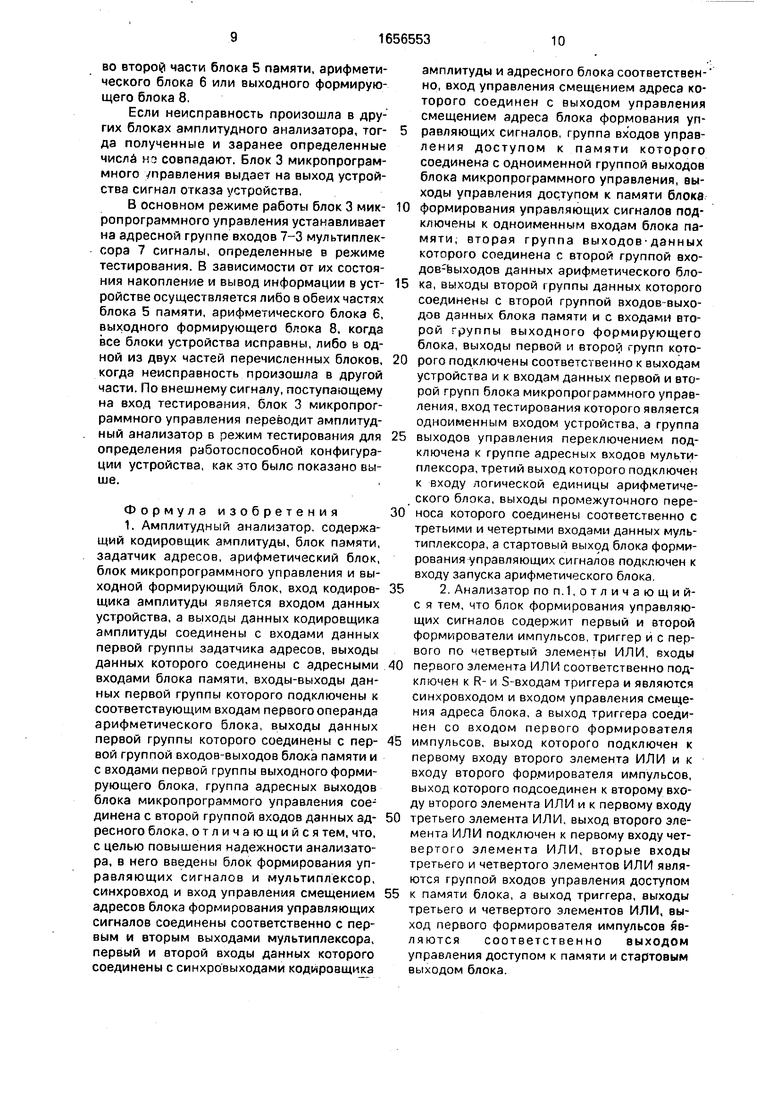

Амплитудный анализатор работает в режиме тестирования и в основном режиме (фиг.6).

5При включении или при наличии сигнала на входе тестирования блока 3 микропрограммного управления переводит амплитудный анализатор и режим тестирования. Он устанавливает на адресных входах 7-3 мультиплексора 7 сигналы

(например бО), по которым сигнал 6-6 промежуточного переноса с выхода арифметического блока б подключается через мультиплексор 7 к входу 6-4 логической единицы этого же блока. При этом в накоп- лении и выводе информации участвуют все части лока 5 памяти, арифметического блока б, входного формирующего блока 8.

Блок 3 микропрограммного управления выдает на вторую группу 4-2 входов данных задатчика 4 и на группу 7-3 адресных входов мультиплексора 7 управляющие сигналы, по которым задатчик 4 выдает на свои выходы 4-4 данных заранее определенные коды от счетчика 22 импульсов, а синхроим- пульсы с синхровыходя 4-5 через мультиплексор 7 поступают на синхровход 2-1 блока 2 формирования управляющих сигналов. При этом выходы кодировщика 1 амплитуды отключены.

По известным заранее адресам (кодам) А, генерируемым задатчиком 4, и сигналам управления доступом к памяти 2-5. вырабатываемым блоком 2 формирования управляющих сигналов, в блоке 5 памяти происходит накопление информации, заключающееся в чтении числа по адресу А, которое представляет собой количество импульсов, хранящееся по этому адресу. Затем это число поступает на входы 6-1 и 6 -2 арифметического блока 6, где к нему добавляется новое событие, т.е. +1. Новое число записывается сигналами 2-5 в блок 1 по тему же адресу А. При поступлении новых импульсов процесс, описанный выше, по- вторяется в течение времени экспозиции, которое задается таймером 20 блока 3 микропрограммного управления. По окончании времени экспозиции блок 3 микропрограммного управления начинает вывод инфор- мэции, заключающийся в том, что на входы 4-2 второй группы задатчика адресов 4 поступают коды (адреса) от блока 3 микропрограммного управления и устанавливаются на входах первой группы блока 5. По сигналам 2-5, вырабатываемым блоком 2 формирования управляющих сигналов, происходит чтение накопленных в блоке 5 памяти чисел, которые через выходной формирующий блок 8 выдаются на входы 3-4 и 3-5 данных первой и второй групп блока 3 микропрограммного управления. После чтения блок 3 записывает по каждому адресу блока 5 число ноль.

Блок 3 микропрограммного управления сравнивает полученные в результате тестирования числа с заренее определенными значениями, которые хранятся в узле постоянной памяти 17 блока 3. Это можно осуществить с помощью операций сравнения.- Здесь возможны два варианта.

Первый вариант, все блоки исправны, тогда сравниваемые числа совпадают. Тестирование заканчивается, для чего блок 3 микропрограммного управления устанавливает управляющие сигналы на второй группе входов 4-2 задатчика адресов 4 и на третьей группе 7-3 адресных входов мультиплексора 7 При этом на выходы данных 4-4 задатчика адресов и на синхро-вход 2-1 блока 2 формирования управляющих сигналов поступают соответственно адреса (коды) и синхросиналы от кодировщика 1 амплитуды. Амппитудный анализатор готов к работе F основном режиме. На вход устройства подается анализируемая последовательность импульсов В кодировщике 1 амплитуды амплитуда входного импульса преобразуется в цифровой код сопровождаемый синхросигналом на синхровыходе кодировщика 1 амплитуды По этому коду (адресу) AI в блоке памяти 5 по сигналам 2-5 блока 2 формирования управляющих сигналов происходит накопление информации, как описано выше, в течение времени экспозиции. По окончании времени экспозиции блок 3 микропрограммного управления начинает вывод информации

Второй вариант: один из блоков устройства неисправен, тогда полученные в результате тестирования числа не совпадают с заранее определенными Блок 3 микропрограммного управления устанавливает на адресных входах 7-3 мультиплексора 7 сигналы, по которым сигнал 6-6 промежуточного переноса с выхода арифметического блока 6 подключается через мультиплексор 7 к входу 2-2 бпока 2 формирования управляющих сигналов Тестирование амплитудного анализатора продолжается. При этом запоминание накопление и вывод информации осуществляется в первой части блока 5 памяти арифметического блока 6 и выходного формирующего блока 8. Пусть число NI, накопленное в блоке памяти 5 по адресу AI, за время Т Тэ. будет 2S1 - 1. где Тэ - время экспозиции, Si - количество разрядов в первой группе выходов анализатора. При этом вторая часть (например, старшие разряды) блока памяти 5 арифметического блока 6 участия в накоплении информации еще не принимали

При генерировании задатчиком адресов 4 адреса AI число N, поступает на входы 6-1 арифметического блока 6, где к нему добавляется новое событие, т.е. +1. При этом «а выходах 6-5 первой группы арифметического блока б присутствует нулевая информация, которая запишется в блок 5 памяти по

адресу At, а на выходе 6-6 промежуточного переноса арифметического блока 6 появится сигнал промежуточного переноса, который через мельтиплексор 7 поступит на вход 2-2 управления смещением адреса блока 2 формирования управляющих сигналов. При этом блок 2 формирует сигнал 2-4 смещения адреса, так что адрес AJ, поступающий на входы адреса блока 5 памяти, равен AJ А АО, где АО - постоянное число, и сигналы 2-5, по которым произойдет накопление информации по адресу AJ в Si разрядах блока памяти 5.

При генерировании задатчиком адресов 4 вновь адреса AI сигнал смещения адреса снимается, информация накапливается в Si первых разрядах блока 5 до тех пор, пока накопленное число NI не станет вновь равно 2 - 1, после чего повторится процесс, описанный выше, и к числу NJ. содержащемуся в блоке 5 памяти по адресу А), добавится новое событие, т.е. +1.

Таким образом накопление информации происходит в первой части блока 5 памяти и арифметического блока 6. При этом число импульсов, соответствующих определенному коду At, содержится в младших разрядах двух слов блока 5 по адресам AI и AJ, причем старшие разряды числа содержатся в Si младших разрядах по адресу AJ, а младшие разряды - в Si младших разрядах по адресу AI.

По окончании времени экспозиции начинается вывод информации, на входы 4-2 второй группы задатчика адресов 4 поступают коды (адреса) от блока 3 микропрограммного управления,

По адресам AI и AJ, по сигналам 2-5 проихсодит чтение накопленных в блоке 5 чисел, которые через выходной формирующий блок 8 выдаются на входы блока 3 микропрограммного управления. Блок 3 микропрограммного управления формирует новое слово так, что Si старших разрядов его представляют собой Si младших разрядов числа, считанного по адресу А), а младшие разряды содержатся в Si младших разрядах числа, считанного по адресу AI (это можно осуществить, например, с помощью операций сдвига и логического умножения), При этом информация, содержащаяся на выходах второй группы выходного формирующего блока 8, не учитывается. Далее блок 3 микропрограммного управления сравнивает полученные в результате тестирования числа с заренее определенными значениями. Здесь также возможны два случая. Неисправность произошла во второй части блока 5 памяти, арифметического блока 6 или выходного блока 8, тогда полученные и

заранее определенные числа совпадают. Тестирование заканчивается, выходы данных кодировки кодировщика 1 амплитуды подключаются к входам данных задатчика

адресов 4. Амплитудный анализатор готов к работе в основном режиме, которая осуществляется так, как показано выше. При этом накопление и вывод информации осуществляется в первой части блока 5 памяти, ариф0 метического блока 6 и выходного формирующего блока 8. Если неисравность произошла в первой части блока 5 памяти, арифметического блока 6 или выходного формирующего блока 8, тогда получен5 ные и заранее определенные числа не совпадают.

Блок 3 микропрограммного управления устанавливает на входах 7 3 мультиплексора 7 сигналы, по которым сигнал 6 6 проме0 жуточного переноса отключается от входа 2-2 блока 2 формирования сигналов, а подключается сигнал 6-7 переноса со второй части арифметического блока 6, одновременно на его вход 6-4 подается уровень

5 лог.1. Тестирование продолжается, при этом накопление и вывод информации осуществляется во второй части блока 5 памяти, арифметического блока 6 и выходного формирующего блока 8, аналогично тому,

0 как это происходит в предыдущем случае.

По окончании времени экспозиции начинается вывод информации, по адресам AI и AJ происходит чтение накопленных в блоке 5 чисел, которые через выходной формиру5 ющий блок 8 выдаются на выход устройства и на входы блока 3 микропрограммного управления. Блок 3 микропрограммного управления формирует новое слово, так что S2 старших разрядов его представляют собой

0 S2 старших разрядов числа, считанного по адресу AJ; а младшие разряды содержатся в S2 старших разрядах числа, считанного по адресу А. При этом информация, содержащаяся на вы5 ходах первой группы выходного формирующего блока 8, не учитывается. Далее блок 3 микропрограммного управления сравнивает полученные в результате тестирования числа с заранее определенными

0 значениями. Здесь возможны два случая. Неисправность произошла в первой части блока 6 памяти, арифметического блока 6 или выходного формирующего блока 8, тогда полученные и заранее определенные чис5 ла совпадают. Тестировании заканчивается, выходы данных кодировщика 1 амплитуды подключаются к входам данных задатчика 4 адресов. Амплитудный анализатор готов к работе в основном режиме. При этом наю i- ление и вывод информации осуществляете

во второй части блока 5 памяти, арифметического блока 6 или выходного формирующего блока 8.

Если неисправность произошла в других блоках амплитудного анализатора, тогда полученные и заранее определенные числи совпадают. Блок 3 микропрограммного управления выдает на выход устройства сигнал отказа устройства.

В основном режиме работы блок 3 мик ропрограммного управления устанавливает на адресной группе входов 7-3 мультиплексора 7 сигналы, определенные в режиме тестирования. В зависимости от их состояния накопление и вывод информации в устройстве осуществляется либо в обеих частях блока 5 памяти, арифметического блока 6, выходного формирующего блока 8, когда все блоки устройства исправны, либо в одной из двух частей перечисленных блоков, когда неисправность произошла в другой части. По внешнему сигналу, поступающему на вход тестирования, блок 3 микропрограммного управления переводит амплитудный анализатор в режим тестирования для определения работоспособной конфигурации устройства, как это было показано ьы- ше.

Формула изобретения 1. Амплитудный анализатор, содержащий кодировщик амплитуды, блок пэмяти, задатчик адресов, арифметический блок, блок микропрограммного управления и выходной формирующий блок, вход кодировщика амплитуды является входом данных устройства, а выходы данных кодировщика амплитуды соединены с входами данных первой группы задатчика адресов, выходы данных которого соединены с адресными входами блока памяти, входы-выходы данных первой группы которого подключены к соответствующим входам первого операнда арифметического блока, выходы данных первой группы которого соединены с первой группой входов-выходов блоха памяти и с входами первой группы выходного формирующего блока, группа адресных выходов блока микропрограммого управления соединена с второй группой входов данных адресного блока, отличающийся тем, что, с целью повышения надежности анализатора, в него введены блок формирования управляющих сигналов и мультиплексор, синхровход и вход управления смещением адресов блока формирования управляющих сигналов соединены соответственно с пер вым и вторым выходами мультиплексора, первый и второй входы данных которого соединены с синхровыходами кодировщика

амплитуды и адресного блока соответствен- но, вход управления смещением адреса которого соединен с выходом управления смещением адреса блока формования уп- 5 равляющих сигналов, группа входов управления доступом к памяти которого соединена с одноименной группой выходов блока микропрограммного управления, выходы управления доступом к памяти блоке

0 формирования управляющих сигналов подключены к одноименным входам блока памяти, вторая группа выходов-данных которого соединена с второй группой вхо- дов-Ьыходов данных арифметического бло5 ка, выходы второй фуппы данных которого соединены с второй группой входов выходов данных блока памяти и с входами второй группы выходного формирующего блока, выходы первой и второй групп кото0 рого подключены соответственно к выходам устройства и к входам данных первой и второй групп блока микропрограммного управления, вход тестирования которого является одноименным входом устройства, а группа

5 выходов управления переключением подключена к группе адресных входов мультиплексора, третий выход которого подключен к входу логической единицы арифметического блока, выходы промежуточного пере0 носа которого соединены соответственно с третьими и четертыми входами данных мультиплексора, а стартовый выход блока формирования управляющих сигналов подключен к входу запуска арифметического блока.

52. Анализатор поп.1,отличающийс я тем, что блок формирования управляющих сигналов содержит первый и второй формирователи импульсов, триггер и с первого по четвертый элементы ИЛИ, входы

0 первого элемента ИЛИ соответственно подключен к R- и S-входам триггера и являются синхровходом и входом управления смещения адреса блока, а выход триггера соединен со входом первого формирователя

5 импульсов, выход которого подключен к первому входу второго элемента ИЛИ и к входу второго формирователя импульсов, выход которого подсоединен к второму входу второго элемента ИЛИ и к первому входу

0 третьего элемента ИЛИ. выход второго элемента ИЛИ подключен к первому входу четвертого элемента ИЛИ, вторые входы третьего и четвертого элементов ИЛИ являются группой входов управления доступом

5 к памяти блока, а выход триггера, выходы третьего и четвертого элементов ИЛИ, выход первого формирователя импульсов йв- ляются соответственно выходом управления доступом к памяти и стартовым выходом блока.

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления с самоконтролем | 1987 |

|

SU1427367A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для анализа распределений случайных процессов | 1986 |

|

SU1517040A1 |

Изобретение относится к вычислительной технике и может быть использовано в амплитудных анализаторах например в ядерных спектрометрических исследованиях на автоматических необслуживаемых измерительных комплексах, к которым предъявляются требования высокой надежности. Цель изобретения - повышение надежности анализатора Амплитудный анализатор содержит кодировщик 1 амплитуды блок 2 формирования управляющих сигналов, блок 3 микропро. раммного управления, задатчик адресов 4 бпок памяти 5 арифметический блок 6 и выходной формирующий блок 8, а также коммутатор 7 Анализатор обладает повышенной надежностью за счет того, что выход из строя части блока памяти 5 блоков 6 или 8 не ведет к отказу анализатора в целом, Это обеспечивается автоматическим измексни ем конфигурации анализатора, в результате которого отказавшие части указанных блоков исключаются из процесса накопления и выхода информации а вся прежняя информация накапливается и выводится из работоспособных частей этих блоков 1 з п ф-лы. 6 ил. Ё а сл о сл сл 00

n in in со in to

tb CM

10

cx5

41

Вкл.

Вход -А тестировании

Перейти 8режим тестирования Установить на 8ыходвхЗ-3 Установить на быходах Н А -А1 Запустить таймер 20 Тэ

По сигналу от таймера 20 останов таймера 20, чтение ЗУ5: по адресам А1В дести данные со Sxodo33-4,

Продолжить тестирование : Установить на выходах 5- 3 Запустить таймер 20

По сигналу от таймера 20 : останов.таймера 70, чтение ЗУ5: по адресам A L, А dSecmu данные сВхоооб 3-4

I

Вычислить Ni - S1(Aj}S1(Ai)

Продолжить тестирование: Устанодить надыходрх Я-10 Запустить таймер 20

Посигналу от таймера 20: ОСтанад таймера 20, чтение ЗУ5 по адресам A i Aj Ввести данные с входов 3-5

1

Вычислить Ni M(Aj)S2(Ai)

задам- Устройство неисправно гдп

Перейти 8 основной режим

измерение :

Установить набыходах Установить на выходах 3-1 А А2 Запустить таймер 20

ПО сигналу от таймера 20. останов, таймера WI чтение 5 У5.

по адресам A i., A j- Воести данные Свходов3-4-, 3-5

Устройстдо неиспрадно

| Устройство для контроля и коммутации резервных блоков | 1984 |

|

SU1252782A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ядерная электроника | |||

| М Энергоатомиздат, 1984, с 285 | |||

Авторы

Даты

1991-06-15—Публикация

1989-04-25—Подача