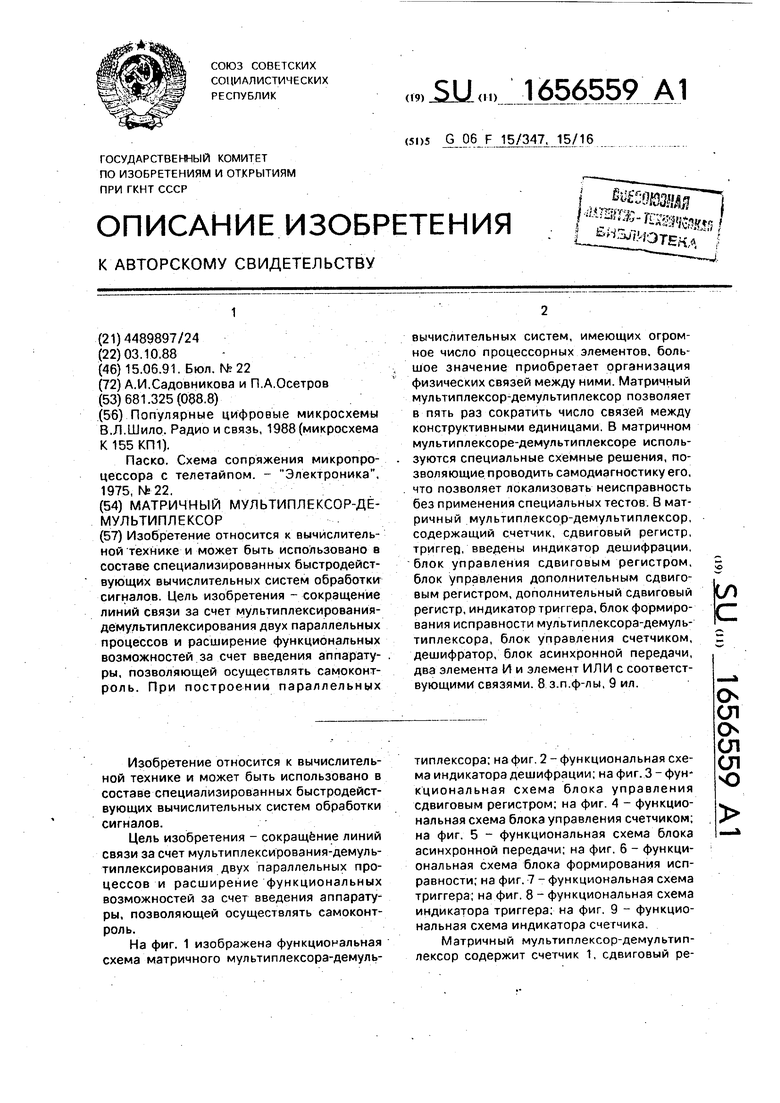

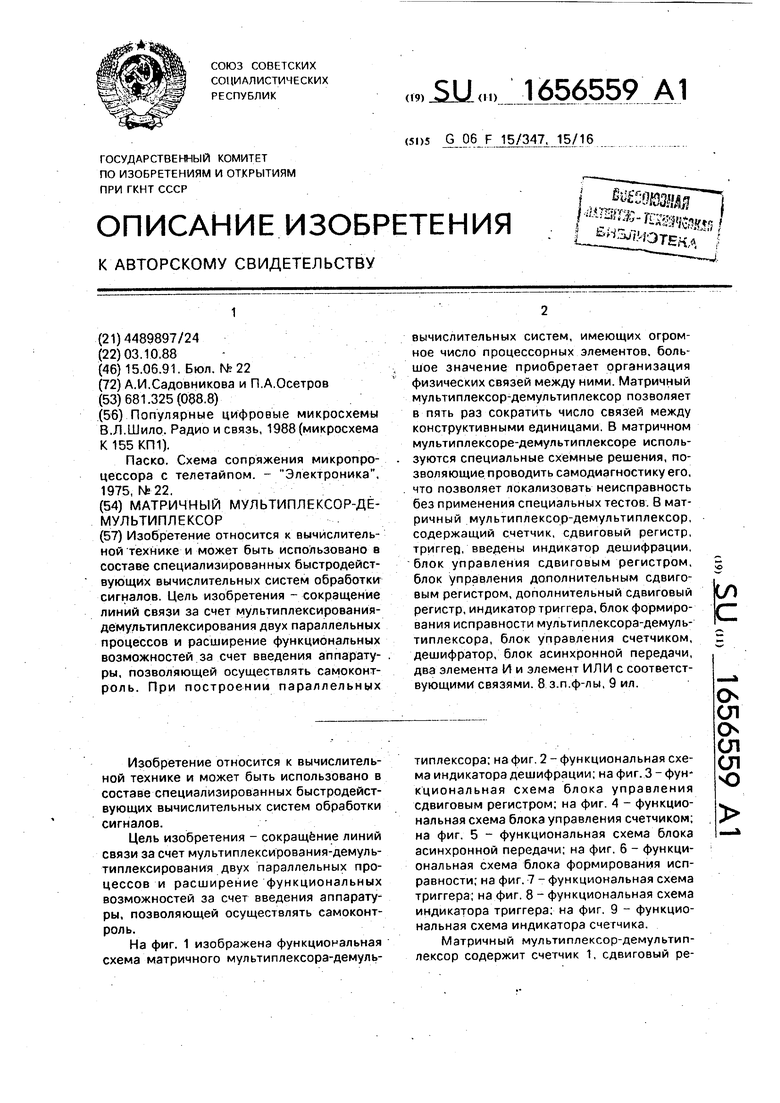

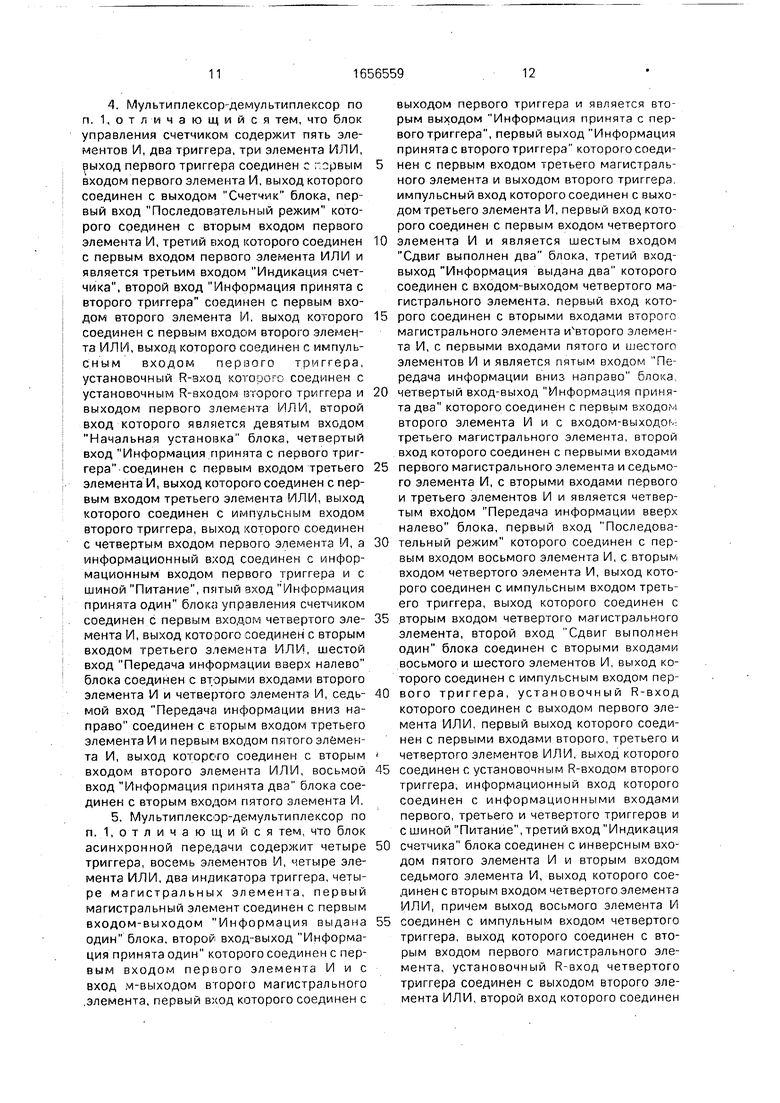

гистр 2, триггер 3, первую информационную группу 4 входов, индикатор 5 дешифрации, блок 6 управления сдвиговым регистром, блок 7 управления дополнительным сдвиговым регистром, дополнительный сдвиговый регистр 8, индикатор 9 триггера, олок 10 формирования исправности, блок 11 управления счетчиком, дешифратор 12, блок 13 асинхронной передачи, первый элемент И 14, второй элемент И 15, элемент ИЛИ 16, первый информационный выход 17, второй информационный выход 18, выход 19 Микрокоманда выполнена, вход 20 Микрокоманда выдана, вход 21 Прием информации закончен, вторую группу 22 информационных входов, первый вход-выход 23 Информация выдана один, второй вход-выход24 Информация принята один, третий вход-выход 25 Информ, ция выдана два, четвертый вход-выход 26 Информация принята два, группу 27 входов Дешифрация закончена, вход 28 Передача информации вверх налево, вход 29 Передача информации вниз направо, вход 30 Начальная установка.

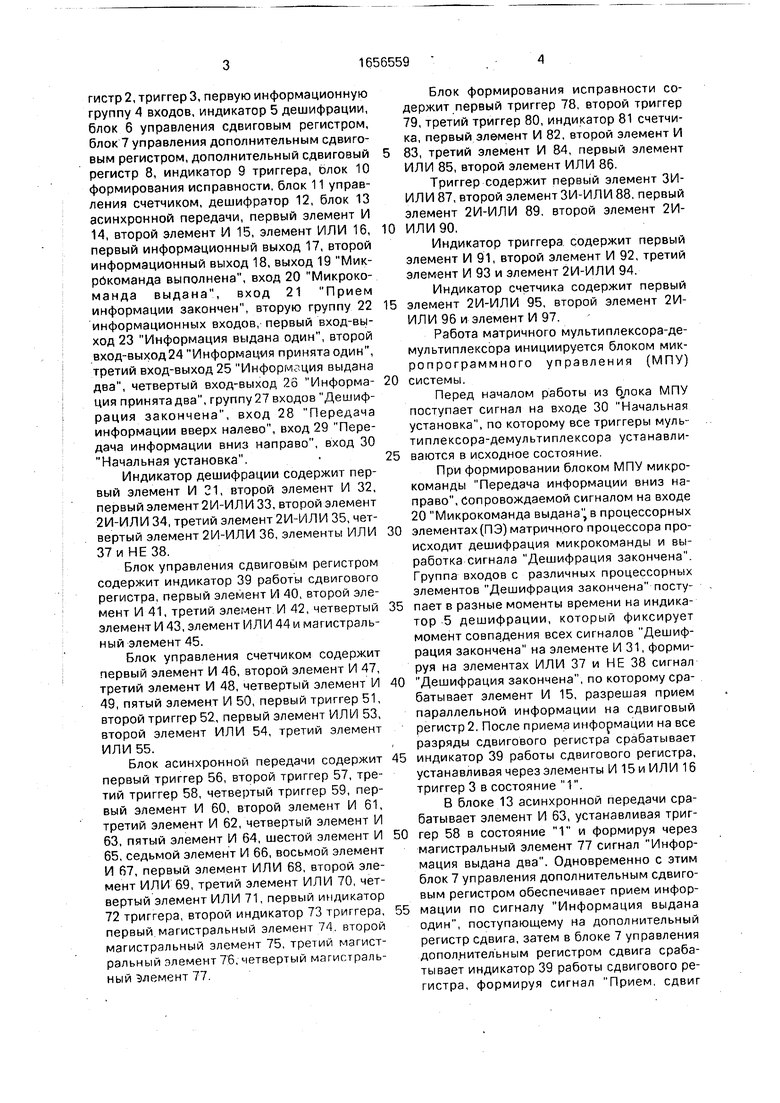

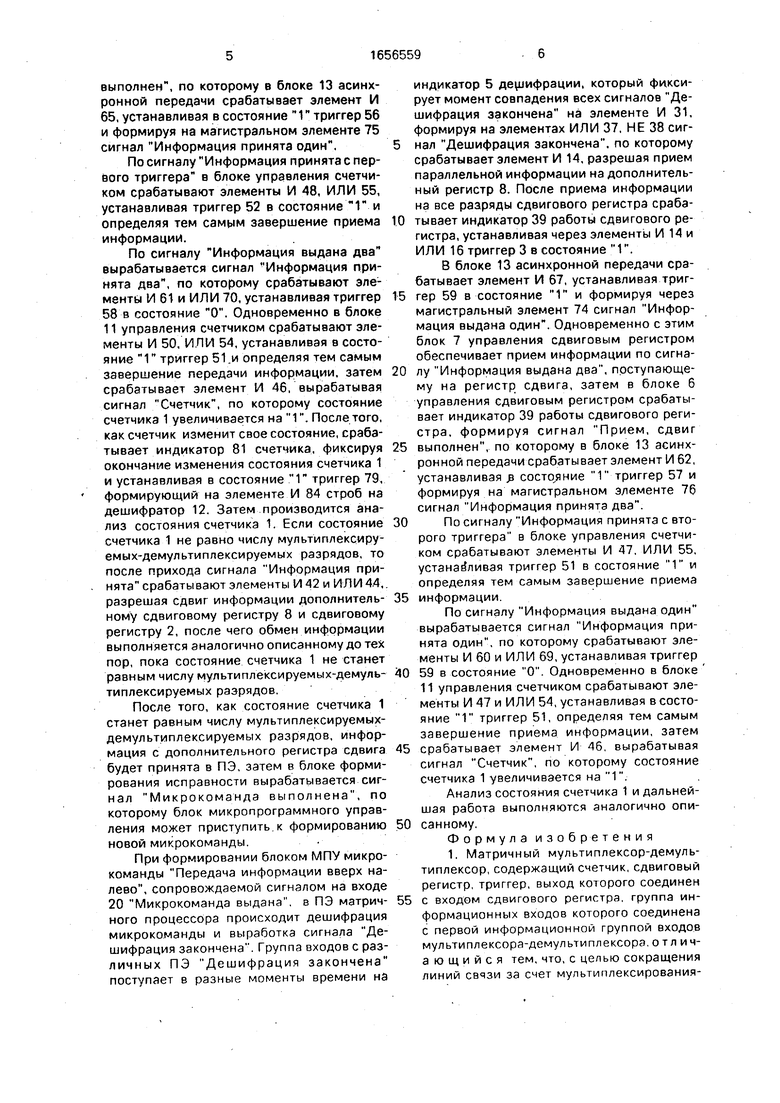

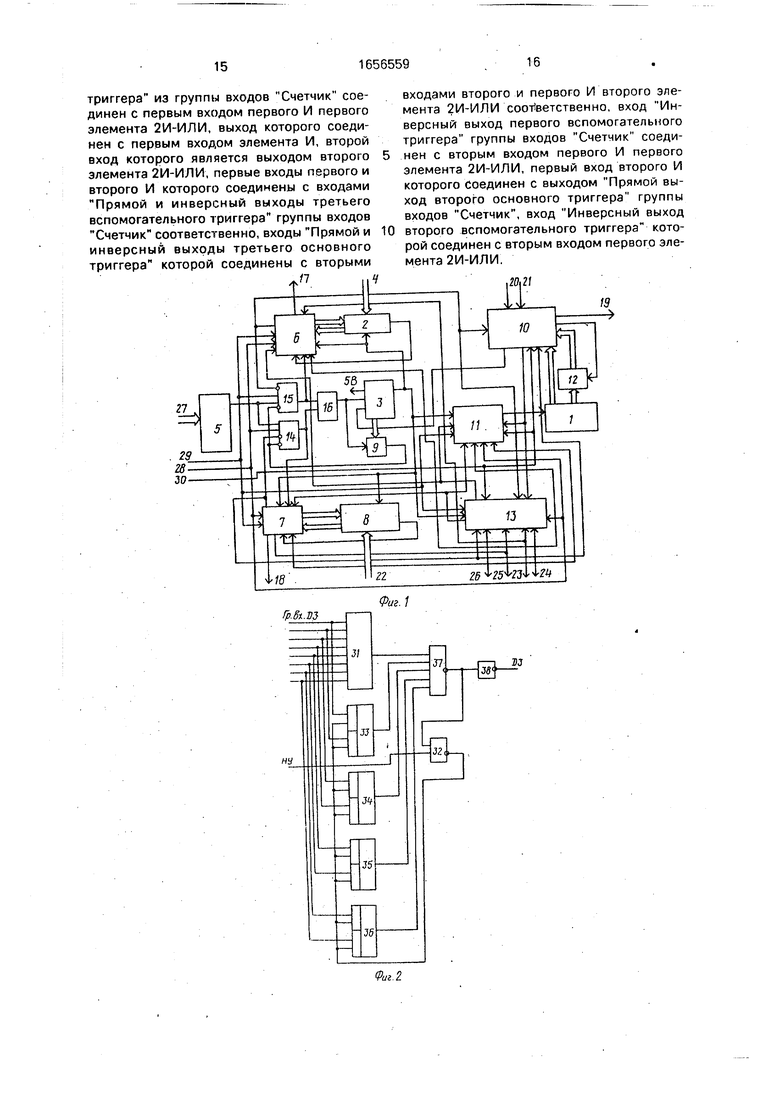

Индикатор дешифрации содержит первый элемент И 21, второй элемент И 32, первый элемент 2И-ИЛИ 33, второй элемент 2И-ИЛИ 34, третий элемент 2И-ИЛИ 35, четвертый элемент 2И-ИЛИ 36, элементы ИЛИ 37 и НЕ 38.

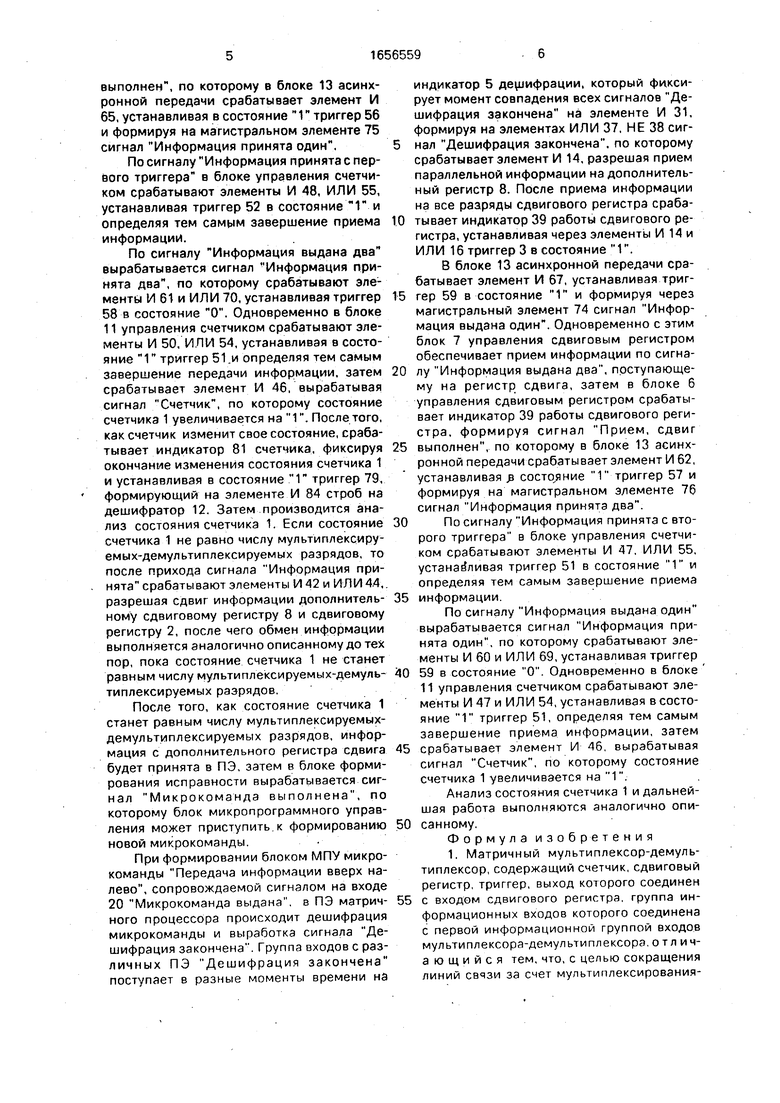

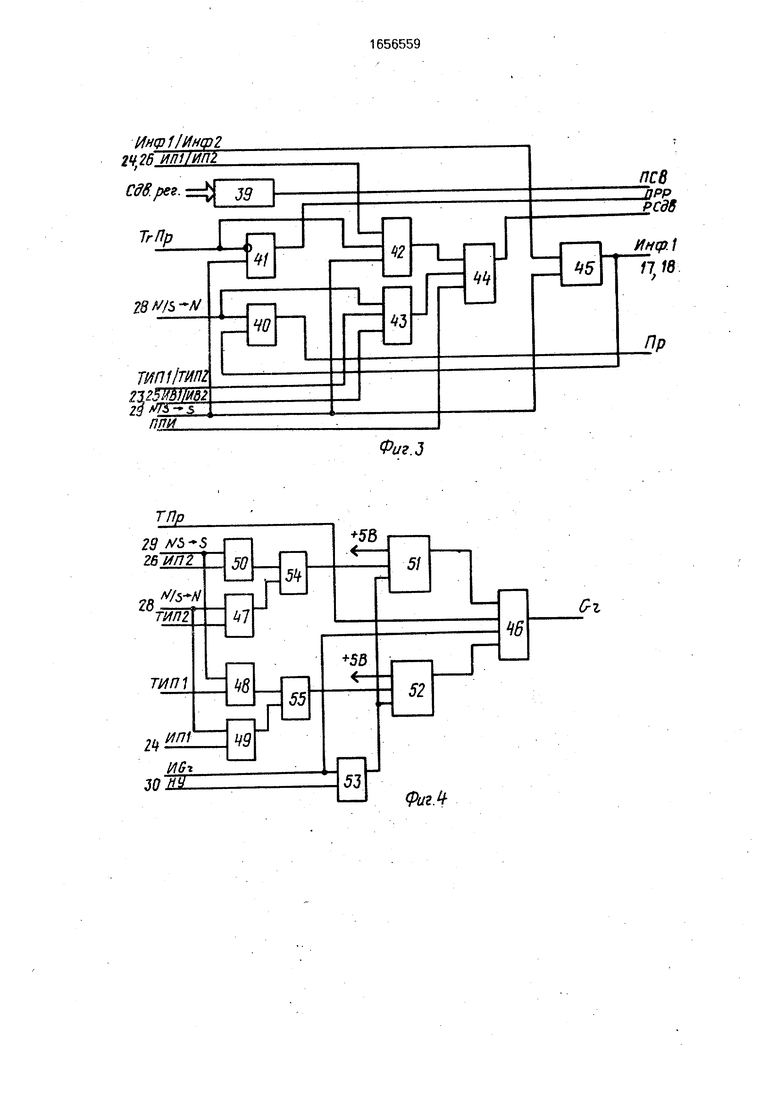

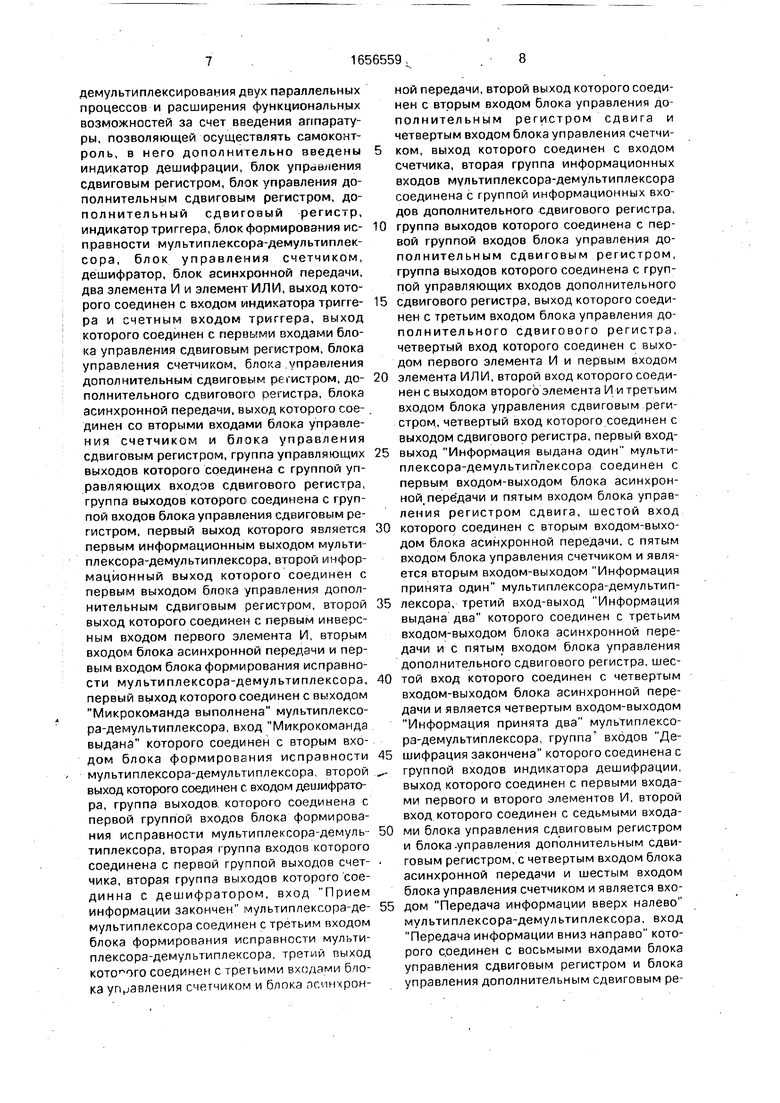

Блок управления сдвиговым регистром содержит индикатор 39 работы сдвигового регистра, первый элемент И 40, второй элемент И 41, третий элемент И 42, четвертый элемент И 43, элемент ИЛИ 44 и магистральный элемент 45.

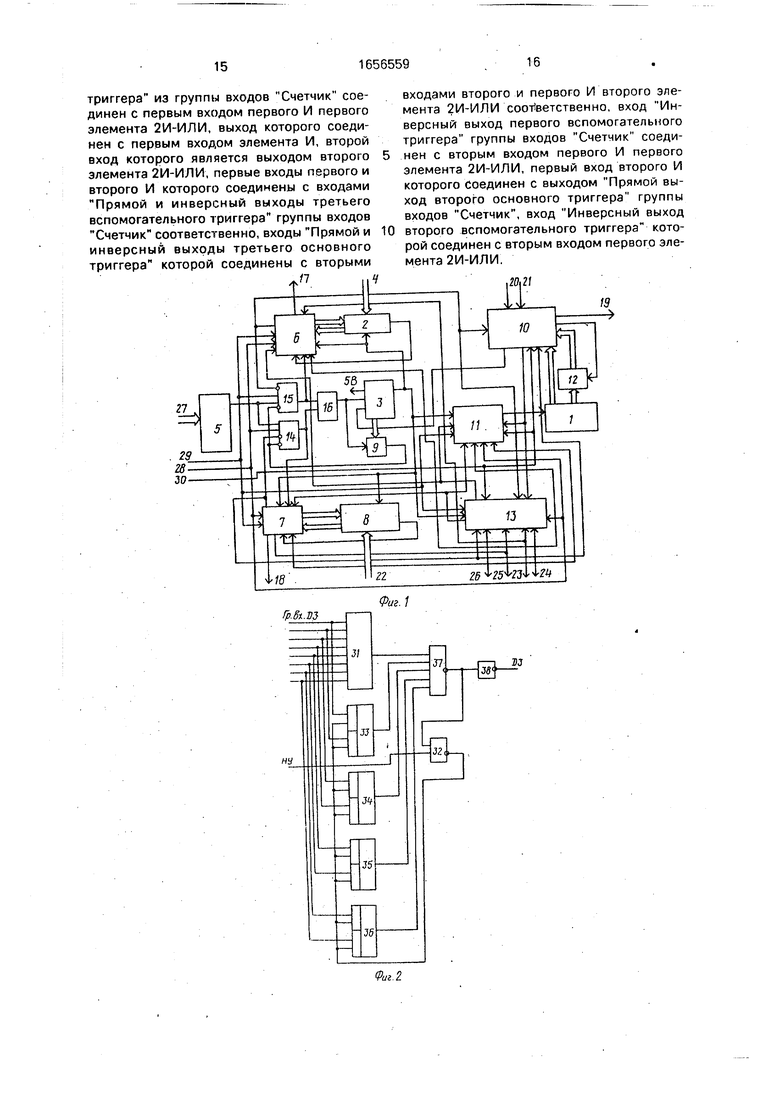

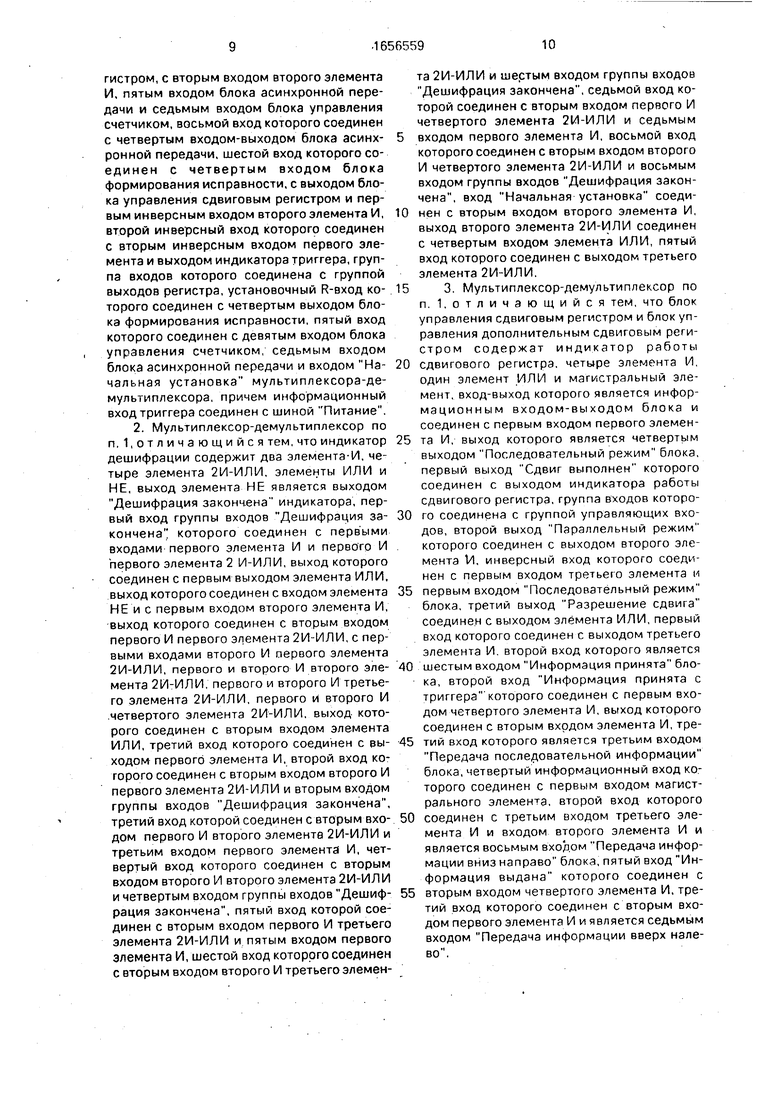

Блок управления счетчиком содержит первый элемент И 46, второй элемент И 47, третий элемент И 48, четвертый элемент И 49, пятый элемент И 50, первый триггер 51, второй триггер 52, первый элемент ИЛИ 53, второй элемент ИЛИ 54, третий элемент ИЛИ 55.

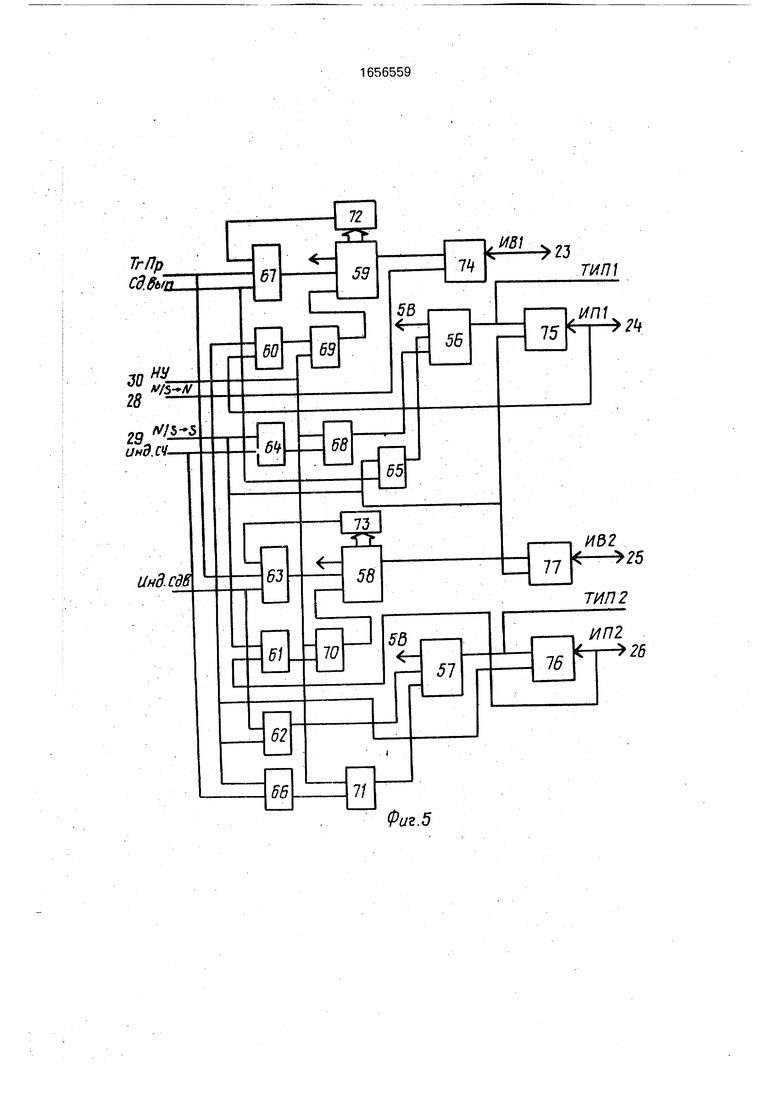

Блок асинхронной передачи содержит первый триггер 56, второй триггер 57, третий триггер 58, четвертый триггер 59, первый элемент И 60, второй элемент И 61, третий элемент И 62, четвертый элемент И 63, пятый элемент И 64, шестой элемент И 65, седьмой элемент И 66, восьмой элемент И 67, первый элемент ИЛИ 68, второй элемент ИЛИ 69, третий элемент ИЛИ 70, четвертый элемент ИЛИ 71. первый индикатор 72 триггера, второй индикатор 73 триггера, первый магистральный элемент 74 второй магистральный элемент 75. третий магистральный элемент 76, четвертый мпгис.тральный Элемент 77.

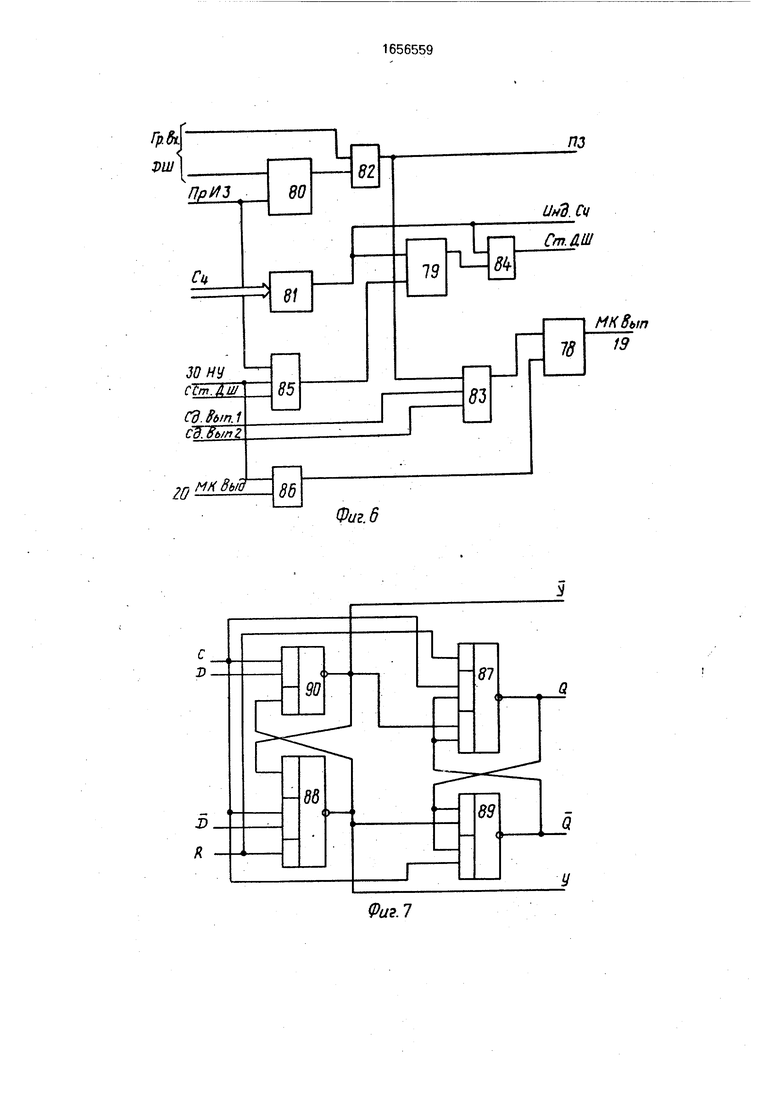

Блок формирования исправности содержит первый триггер 78, второй триггер 79, третий триггер 80, индикатор 81 счетчика, первый элемент И 82, второй элемент И

83, третий элемент И 84, первый элемент ИЛИ 85, второй элемент ИЛИ 86.

Триггер содержит первый элемент ЗИ- ИЛИ 87, второй элемент ЗИ-ИЛИ 88. первый элемент 2И-ИЛИ 89, второй элемент 2И0 ИЛИ 90.

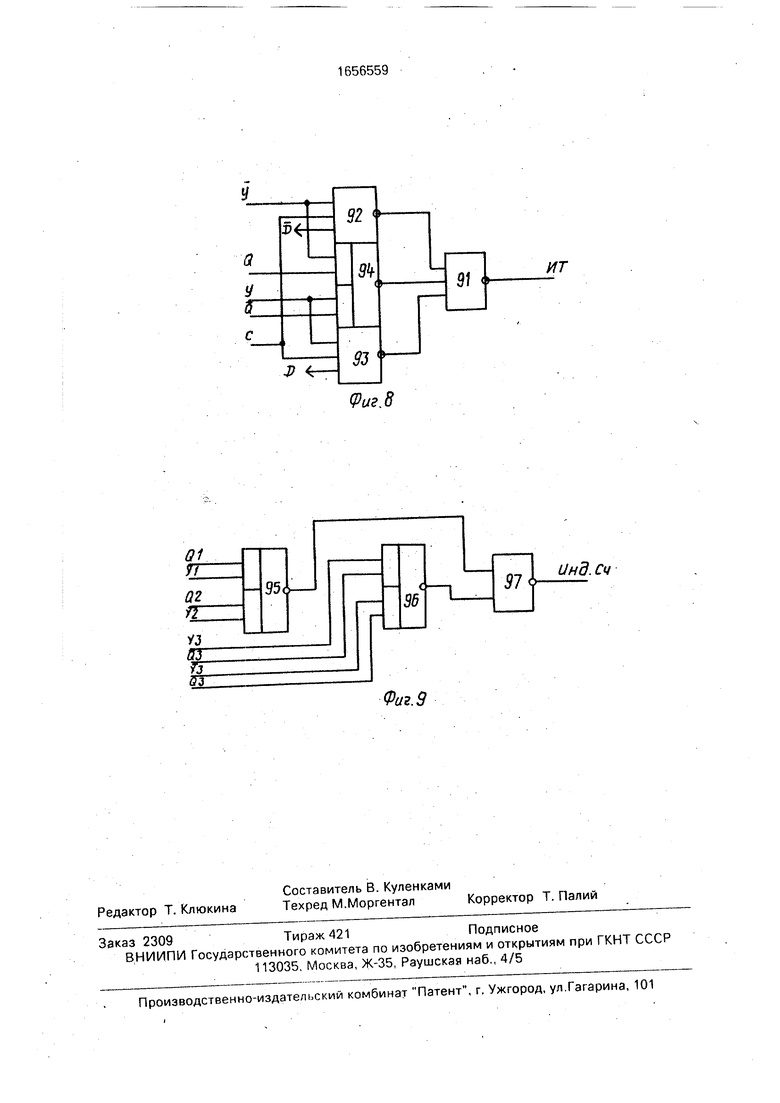

Индикатор триггера содержит первый элемент И 91, второй элемент И 92, третий элемент И 93 и элемент 2И-ИЛИ 94.

Индикатор счетчика содержит первый

5 элемент 2И-ИЛИ 95, второй элемент 2И- ИЛИ 96 и элемент И 97.

Работа матричного мультиплексора-де- мультиплексора инициируется блоком микропрограммного управления (МПУ)

0 системы.

Перед началом работы из МПУ поступает сигнал на входе 30 Начальная установка, по которому все триггеры муль типлексора-демультиплексора устанавли5 ваются в исходное состояние.

При формировании блоком МПУ микрокоманды Передача информации вниз направо, сопровождаемой сигналом на входе 20 Микрокоманда выдана в процессорных

0 элементах (ПЭ) матричного процессора происходит дешифрация микрокоманды и выработка сигнала Дешифрация закончена. Группа входов с различных процессорных элементов Дешифрация закончена посту5 пает в разные моменты времени на индикатор 5 дешифрации, который фиксирует момент совпадения всех сигналов Дешифрация закончена на элементе И 31, формируя на элементах ИЛИ 37 и НЕ 38 сигнал

0 Дешифрация закончена, по которому срабатывает элемент И 15, разрешая прием параллельной информации на сдвиговый регистр2. После приема информации на все разряды сдвигового регистра срабатывает

5 индикатор 39 работы сдвигового регистра, устанавливая через элементы И 15 и ИЛИ 16 триггер 3 в состояние 1.

В блоке 13 асинхронной передачи срабатывает элемент И 63, устанавливая триг0 гер 58 в состояние 1 и формируя через магистральный элемент 77 сигнал Информация выдана два, Одновременно с этим блок 7 управления дополнительным сдвиговым регистром обеспечивает прием инфор5 мации по сигналу Информация выдана один, поступающему на дополнительный регистр сдвига, затем в блоке 7 управления дополнительным регистром сдвига срабатывает индикатор 39 работы сдвигового регистра, формируя сигнал Прием, сдвиг

выполнен, по которому в блоке 13 асинхронной передачи срабатывает элемент И 65, устанавливая в состояние Г триггер 56 и формируя на магистральном элементе 75 сигнал Информация принята один.

По сигналу Информация принятас первого триггера в блоке управления счетчиком срабатывают элементы И 48, ИЛИ 55, устанавливая триггер 52 в состояние 1 и определяя тем самым завершение приема информации.

По сигналу Информация выдана два вырабатывается сигнал Информация принята два, по которому срабатывают элементы И 61 и ИЛИ 70, устанавливая триггер 58 в состояние О. Одновременно в блоке 11 управления счетчиком срабатывают элементы И 50, И ПИ 54,устанавливая в состояние 1 триггер 51 .и определяя тем самым завершение передачи информации, затем срабатывает элемент И 46. вырабатывая сигнал Счетчик, по которому состояние счетчика 1 увеличивается на 1. После того, как счетчик изменит свое состояние, срабатывает индикатор 81 счетчика, фиксируя окончание изменения состояния счетчика 1 и устанавливая в состояние 1 триггер 79, формирующий на элементе И 84 строб на дешифратор 12. Затем производится анализ состояния счетчика 1. Если состояние счетчика 1 не равно числу мультиплексируемых-демультиплексируемых разрядов, то после прихода сигнала Информация принята срабатывают элементы И 42 и ИЛИ 44, разрешая сдвиг информации дополнительному сдвиговому регистру 8 и сдвиговому регистру 2, после чего обмен информации выполняется аналогично описанному до тех пор, пока состояние счетчика 1 не станет равным числу мультиплексируемых-демультиплексируемых разрядов.

После того, как состояние счетчика 1 станет равным числу мультиплексируемых- демультиплексируемых разрядов, информация с дополнительного регистра сдвига будет принята в ПЭ. затем в блоке формирования исправности вырабатывается сигнал Микрокоманда выполнена, по которому блок микропрограммного управления может приступить к формированию новой микрокоманды.

При формировании блоком МПУ микрокоманды Передача информации вверх налево, сопровождаемой сигналом на входе 20 Микрокоманда выдана, в ПЭ матричного процессора происходит дешифрация микрокоманды и выработка сигнала Дешифрация закончена. Группа входов с различных ПЭ Дешифрация закончена поступает в разные моменты времени на

индикатор 5 дешифрации, который фиксирует момент совпадения всех сигналов Дешифрация закончена на элементе И 31, формируя на элементах ИЛИ 37, НЕ 38 сигнал Дешифрация закончена, по которому срабатывает элемент И 14, разрешая прием параллельной информации на дополнительный регистр 8. После приема информации на все разряды сдвигового регистра сраба0 тывает индикатор 39 работы сдвигового регистра, устанавливая через элементы И 14 и ИЛИ 16 триггер 3 в состояние 1.

В блоке 13 асинхронной передачи срабатывает элемент И 67, устанавливая триг5 rep 59 в состояние 1 и формируя через магистральный элемент 74 сигнал Информация выдана один. Одновременно с этим блок 7 управления сдвиговым регистром обеспечивает прием информации по сигна0 лу Информация выдана два, поступающему на регистр сдвига, затем в блоке 6 управления сдвиговым регистром срабатывает индикатор 39 работы сдвигового регистра, формируя сигнал Прием, сдвиг

5 выполнен, по которому в блоке 13 асинхронной передачи срабатывает элемент И 62. устанавливая ,в состояние 1 триггер 57 и формируя на магистральном элементе 76 сигнал Информация принята два.

0По сигналу Информация принята с второго триггера в блоке управления счетчиком срабатывают элементы И 47. ИЛИ 55. устанавливая триггер 51 в состояние 1 и определяя тем самым завершение приема

5 информации.

По сигналу Информация выдана один вырабатывается сигнал Информация принята один, по которому срабатывают элементы И 60 и ИЛИ 69, устанавливая триггер

0 59 в состояние О. Одновременно в блоке 11 управления счетчиком срабатывают элементы И 47 и ИЛИ 54, устанавливая в состояние 1 триггер 51, определяя тем самым завершение приема информации, затем

5 срабатывает элемент И 46, вырабатывая сигнал Счетчик, по которому состояние счетчика 1 увеличивается на 1.

Анализ состояния счетчика 1 и дальнейшая работа выполняются аналогично опи0 санному.

Формула изобретения 1. Матричный мультиплексор-демуль- типлексор, содержащий счетчик, сдвиговый регистр, триггер, выход которого соединен

5 с входом сдвигового регистра, группа информационных входов которого соединена с первой информационной группой входов мультиплексора-демультиплексора. отличающийся тем. что. с целью сокращения линий связи за счет мультиплексированиядемультиплексирования двух параллельных процессов и расширения функциональных возможностей за счет введения аппаратуры, позволяющей осуществлять самоконтроль, в него дополнительно введены индикатор дешифрации, блок управления сдвиговым регистром, блок управления дополнительным сдвиговым регистром, дополнительный сдвиговый регистр, индикатор триггера, блок формирования исправности мул ьтиплексора-демультип лек- сора, блок управления счетчиком, дешифратор, блок асинхронной передачи, два элемента И и элемент ИЛИ, выход которого соединен с входом индикатора триггера и счетным входом триггера, выход которого соединен с первыми входами блока управления сдвиговым регистром, блока управления счетчиком, блока управления дополнительным сдвиговым рпистром, дополнительного сдвигового регистра, блока асинхронной передачи, выход которого соединен со вторыми входами блока управления счетчиком и блока управления сдвиговым регистром, группа управляющих выходов которого соединена с группой управляющих входов сдвигового регистра, группа выходов которого соединена с группой входов блока управления сдвиговым регистром, первый выход которого является первым информационным выходом мульти- плексора-демультиплексора, второй информационный выход которого соединен с первым выходом блока управления дополнительным сдвиговым регистром второй выход которого соединен с первым инверсным входом первого элемента И вторым входом блока асинхронной передачи и первым входом блока формирования исправности мультиплексора-демультиплексора. первый выход которого соединен с выходом Микрокоманда выполнена мультиплексо- ра-демультиплексора, вход Микрокоманда выдана которого соединен с вторым входом блока формирования исправности мультиплексора-демультиплексора. второй выход которого соединен с входом дешифратора, группа выходов которого соединена с первой группой входов блока формирования исправности мультиплексора-демуль- типлексора, вторая группа входов которого соединена с первой группой выходов счетчика, вторая группа выходов которого сое- динна с дешифратором, вход Прием информации закончен мультиплекгора-де- мультиплексора соединен с третьим входом блока формирования исправности мульти- плексора-демультиплексора, третий выход которого соединен с третьими ЕГ-П/КИИИ бпо- ка управления счетчиком и блок,ч лсчнфонной передачи, второй выход которого соединен с вторым входом блока управления дополнительным регистром сдвига и четвертым входом блока управления счетчи- ком, выход которого соединен с входом счетчика, вторая группа информационных входов мультиплексора-демультиплексора соединена с группой информационных входов дополнительного сдвигового регистра,

группа выходов которого соединена с первой группой входов блока управления дополнительным сдвиговым регистром, группа выходов которого соединена с группой управляющих входов дополнительного

сдвигового регистра, выход которого соединен с третьим входом блока управления до- полнительного сдвигового регистра, четвертый вход которого соединен с выходом первого элемента И и первым входом

элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и третьим входом блока управления сдвиговым регистром, четвертый вход которого соединен с выходом сдвигового регистра, первый входвыход Информация выдана один мульти- плексора-демультиплексора соединен с первым входом-выходом блока асинхронной передачи и пятым входом блока управления регистром сдвига, шестой вход

которого соединен с вторым входом-выходом блока асинхронной передачи, с пятым входом блока управления счетчиком и является вторым входом-выходом Информация принята один мультиплексора-демультиплексора, третий вход-выход Информация выдана два которого соединен с третьим входом-выходом блока асинхронной передачи и с пятым входом блока управления дополнительного сдвигового регистра, шестой вход которого соединен с четвертым входом-выходом блока асинхронной передачи и является четвертым входом-выходом Информация принята два мультиплексо- ра-демультиплексора группа входов Дешифрация закончена которого соединена с

группой входов индикатора дешифрации выход которого соединен с первыми входами первого и второго элементов И. второй вход которого соединен с седьмыми входами блока управления сдвиговым регистром и блока управления дополнительным сдвиговым регистром, с четвертым входом блока асинхронной передачи и шестым входом блока управления счетчиком и является входом Передача информации вверх налево мультиплексора-демультиплексора. вход Передача информации вниз направо которого соединен с восьмыми входами блока управления сдвиговым регистром и блока управления дополнительным сдвиговым регистром, с вторым входом второго элемента И, пятым входом блока асинхронной передачи и седьмым входом блока управления счетчиком, восьмой вход которого соединен с четвертым входом-выходом блока асинхронной передачи, шестой вход которого соединен с четвертым входом блока формирования исправности, с выходом блока управления сдвиговым регистром и первым инверсным входом второго элемента И, второй инверсный вход которого соединен с вторым инверсным входом первого элемента и выходом индикатора триггера, группа входов которого соединена с группой выходов регистра, установочный R-вход которого соединен с четвертым выходом блока формирования исправности, пятый вход которого соединен с девятым входом блока управления счетчиком, седьмым входом блока асинхронной передачи и входом Начальная установка мультиплексора-де- мультиплексора, причем информационный вход триггера соединен с шиной Питание. 2. Мультиплексор-демультиплексор по п. 1,отличающийся тем, что индикатор дешифрации содержит два элемента И. четыре элемента 2И-ИЛИ. элементы ИЛИ и НЕ, выход элемента НЕ является выходом Дешифрация закончена индикатора, первый вход группы входов Дешифрация закончена которого соединен с первыми входами первого элемента И и первого И первого элемента 2 И-ИЛИ, выход которого соединен с первым выходом элемента ИЛИ. выход которогосоединен с входом элемента НЕ и с первым входом второго элемента И, выход которого соединен с вторым входом первого И первого элемента 2И-ИЛИ. с первыми входами второго И первого элемента 2И-ИЛИ, первого и второго И второго элемента 2И-ИЛИ первого и второго И третьего элемента 2И-ИЛИ, первого и второго И четвертого элемента 2И-ИЛИ, выход которого соединен с вторым входом элемента ИЛИ, третий вход которого соединен с выходом первого элемента И, второй вход которого соединен с вторым входом второго И первого элемента 2И-ИЛИ и вторым входом группы входов Дешифрация закончена, третий вход которой соединен с вторым входом первого И второго элементе 2И-ИЛИ и третьим входом первого элемента И, четвертый вход которого соединен с вторым входом второго И второго элемента 2И-ИЛИ и четвертым входом группы входов Дешифрация закончена, пятый вход которой соединен с вторым входом первого И третьего элемента 2И-ИЛИ и пятым входом первого элемента И, шестой вход которого соединен с вторым входом второго И третьего элемента 2И-ИЛИ и шестым входом группы входов Дешифрация закончена, седьмой вход которой соединен с вторым входом первого И четвертого элемента 2И-ИЛИ и седьмым

входом первого элемента И. восьмой вход которого соединен с вторым входом второго И четвертого элемента 2И-ИЛИ и восьмым входом группы входов Дешифрация закончена, вход Начальная установка соединен с вторым входом второго элемента И. выход второго элемента 2И-ИЛИ соединен с четвертым входом элемента ИЛИ. пятый вход которого соединен с выходом третьего элемента 2И-ИЛИ.

3. Мультиплексор демультиплексор по

п 1, отличающийся тем, что блок управления сдвиговым регистром и блок управления дополнительным сдвиговым регистром содержат индикатор работы

сдвигового регистра, четыре элемента И. один элемент ИЛИ и магистральный элемент, вход-выход которого является информационным входом-выходом блока и соединен с первым входом первого элемента И. выход которого является четвертым выходом Последовательный режим блока, первый выход Сдвиг выполнен которого соединен с выходом индикатора работы сдвигового регистра, группа входов которого соединена с группой управляющих вхо дов, второй выход Параллельный режим которого соединен с выходом второго эле мента VI, инверсный вход которого соединен с первым входом третьего элемента и

первым входом Последовательный режим блока, третий выход Разрешение сдвига соединен с выходом элемента ИЛИ. первый вход которого соединен с выходом третьего элемента И второй вход которого является

шестым входом Информация принята блока, второй вход Информация принята с триггера которого соединен с первым входом четвертого элемента И, выход которого соединен с вторым входом элемента И, третий вход которого является третьим входом Передача последовательной информации блока, четвертый информационный вход которого соединен с первым входом магистрального элемента, второй вход которого

соединен с третьим ьходом третьего элемента И и входом второго элемента И и является восьмым входом Передача информации вниз направо блока, пятый вход Информация выдана которого соединен с

вторым входом четвертого эпемента И, третий вход которого соединен с вторым входом первого элемента И и является седьмым входом Передача информации вверх налево,

4 Мультиплексор-демультиплексор по п. 1, отличающийся тем, что блок управления счетчиком содержит пять элементов И, два триггера, три элемента ИЛИ. выход первого триггера соединен с рвым входом первого элемента И, выход которого соединен с выходом Счетчик блока, первый вход Последовательный режим которого соединен с вторым входом первого элемента И, третий вход которого соединен с первым входом первого элемента ИЛИ и является третьим входом Индикация счетчика, второй вход Информация принята с второго триггера соединен с первым входом второго элемента И, выход которого соединен с первым входом второю элемента ИЛИ, выход которого соединен г импульсным входом первого трипера установочный «:ото соединен с установочным R входом вюрого гритера и выходом первого элемента ИЛИ, второй вход которого явпяется девятым входом Начальная установка блока, четвертый вход Информация принята с первого триггера соединен с первым входом третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с импульсным входом второго триггера, выход которого соединен с четвертым входом первого элемента И, а информационный вход соединен с информационным входом первого триггера и с шиной Питание, пятый вход Информация принята один блока управления счетчиком соединен с первым входом четвертого элемента И, выход которою соединен г вторым входом третье о элемента ИЛИ шестой вход Передача информации вверх налево блока соединен с вторыми входами второго элемента И и четвертого элемента И седьмой вход Передача информации вниз на право соединен с вторым входом третьего элемента И и первым входом пятого элёмен та И, выход которого соединен с вторым входом второго элемента ИЛИ восьмой вход Информация принята два блока соединен с вторым входом пятого элемента И

5. Мультиплексор-демультиплексор по п. 1, отличающийся тем что блок асинхронной передачи содержит четыре триггера, восемь элементов И, четыре элемента ИЛИ, два индикатора триггера четыре магистральных элемента первый магистральный элемент соединен с первым входом-выходом Информация выдана один блока, второй вход-выход Информация принята один которого соединен с первым входом первого элементе И и с вход м-выходом второго магистрального элемента первый вход которого соединен с

выходом первого триггера и является вто рым выходом Информация принята с первого триггера, первый выход Информация принята с второго триггера которогосоеди

нен с первым входом третьего магистрального элемента и выходом второго триггера импульсный вход которого соединен с выходом третьего элемента И первый вход которого соединен с первым входом четвертого

0 элемента И и является шестым входом Сдвиг выполнен два блока, третий вход- выход Информация выдана два которого соединен с входом-выходом четвертого ма гистрального элемента, первый вход кото5 рого соединен с вторыми входами вторг1г- магистрального элемента ичвторого тлемен та И, с первыми входами пятого и шестого элементов И и является пятым входом Пс редача информации вниз направо блока

0 четвертый вход-выход Информация та два которого соединен с первым входов, второго элемента И и с входом-выхо/ю третьего магистрального элемента второй вход которого соединен с первыми входами

5 первого магистрального элемента и седьмого элемента И, с вторыми входами первого и третьего элементов И и является четвер тым входом Передача информации ввер налево блока, первый вход Последова

0 тельный режим которого соединен с пер вым входом восьмого элемента И, с вторым входом четвертого элемента И, выход кото рого соединен с импульсным входом треть его триггера, выход которого соединен с

5 вторым входом четвертого магистрального элемента, второй вход Сдвиг выполнен один блока соединен с вторыми входами восьмого и шестого элементов И выход которого соединен с импульсным входом пео

0 вого триггера, установочный R вход которого соединен с выходом первого элемента ИЛИ первый выход которого соединен с первыми входами второго третьего и

четвертого элементов ИЛ И выход которого

j соединен г. установочным R-входом второго триггера, информационный вход которого соединен с информационными входами первого, третьего и четвертого триггеров и с шиной Питание, третий вход Индикация

0 счетчика блока соединен с инверсным входом пятого элемента И и вторым входом седьмого элемента И выход которого соединен с вторым входом четвертого элемента ИЛИ, причем выход восьмого элемента И

5 соединен с импульным входом четвертого триггера, выход которого соединен с вторым входом первого магистрального элемента, установочный R-вход четвертого триггера соединен с выходом второго элемента ИЛИ второй вход которого соединен

j выходом первого элемента И. группа выходов четвертого триггера соединена с группой входов первого индикатора триггера, выход которого соединен с третьим входом восьмого элемента И. группа выходов третьего триггера соединена с группсй входов второго индикатора триггера, выход которого соединен с третьим входом четвертого элемента И, установочный R-вход третьего триггера соединен с выходом третьего эле -.снта ИЛИ, второй вход которого соединен с выходом второго элемента И.

6 Мультиплексор-демультиплексор по f1.. I . с,- л и ч а ю щ и и с я тем, чго блек .а-. н исправности содержит три . ..; (,-- I- , ,:,гор счетчика, три чл монт; /: -л дг-.) :г 0- пн ИЛИ. четвор ь:й в и ход -6/V 1 .- 2с . ин-:эна Vi. (хдипеи вы- - Д)м пг- )Ј .:. v;- мемтг: 11 ; п:-- ЫР,- входом

rST -.: .-j. l Га И. гЫ ОЛ КОТОРОГО ССГ ДИ -и t. уст -лт- очным 3 (ходом песиого триг- i рэ. ьЫхсд которого явлжчсй первым i ibr. ; ло:л Микрокоманда выполнена блока, L.Tjprv выход которого ТлроГ; дешифратор:1 ягмяегся выходом трмьм о элемента И I .ej. -fihii i нход которого 1-оляется третьим выходом нликащ. ч сч.мчика блока ч сое

ДМИ; .|- С yCTdHOBO-IHb HI S-ЗХОДОМ ВТОрОГО

триггро,-, и г, выходом индикатора гчетчикэ, rr. V inb вход, в которого ж-. второй груг;|Г ;й охГ Доа блока, первый пход Первый импуль;: из гр-. П :.-.| входов с дешифратора с . i/I Hf-i: с У гяноьочным Я-вхо.ом тре(ьс- гс) триггера, выход котгрг-госседц.-ен г первым входом первого элеме:г;а И, второ 1 гь:о;.: которого является втором пходом Седьмой имг ульс из группы ;,одов с де- и 1/1фр -т1ор8, третий вход Сброс с.гроба де- пифоигора которой соединен с первым входом первого элемента ИЛИ, выход которого соединен с установочным R-входом второго триггера, выход которого соединен с вторым входом третьего элемента И. первый вход Сдвиг выполнен два блока соединен с вторым входом второго элемента И, третий вход которого является четвертым входом Сдвиг выполнен один блока формирования исправности, второй вход Микрокоманда выдана которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с установочным R- входом первого триггера, третий вход Прием информации закончен блока соединен с установочным R-входом третьего триггера и с вторым входом первого элемента ИЛИ, третий вход которого соединен с вторым входом второго элемента ИЛИ и является пятым входом Начальная установка блока.

1. Мультиплексор-демультиплексор по п. 1, отличающийся тем, что триггер содержит два элемента ЗИ-ИЛИ и два эле ментэ 2И-ИЛИ, выход первого элемента ЗИ- ИЛИ является прямым выходом основного триггера и соединен с первыми входами первого и второго И первого элемента 2И- ИЛИ, выход которого является инверсным выходом основного триггера и соединен с

0 первыми входами второго и третьего И первого элемента ЗИ-ИЛИ, второй вход третьего И которого соединен с выходом второго элемента 2И-ИЛИ, с входом первого И второго элемента ЗИ-ИЛИ и является инверс5 ным выходом вспомогательного триггера, прямой выход которого соединен с выходом второго элемента ЗИ-ИЛИ, с вторым входом первого И первого элемента 2И-ИЛИ и с входом второго И второго элемента 2И0 ИЛИ, первый вход первого И которого соединен с вторыми входами вторых И первого элемента 2И-ИЛИ и первого элемента ЗИ- ИЛИ, является импульсным входом триггера и соединен с первым входом второго И

5 второго элемента ЗИ-ИЛИ, второй вход которого соединен с инверсным информационным входом триггера, прямой информационный вход которого соединен с вторым входом второго элемента 2И-ИЛИ.

0 установочный R-вход триггера соединен с входами первого И и третьего И первого и второго элементов ЗИ-ИЛИ.

8. Мультиплексор-демультиплексор по п, 1.отличающийся тем, что индикатор

5 триггера содержит три элемента И и один элемент 2И-ИЛИ выход которого соединен с первым входом первого элемента И. выход которого является выходом Идикатор триггера индикатора, импульсный вход которо0 го соединен с первыми входами второго и третьего элементов И. выход которого соединен с вторым входом первого элемента И, третий вход которого соединен с выходом второго элемента И, второй вход которого

5 соединен с первым входом первого И элемента 2И-ИЛИ и является входом Инверсный выход вспомогательного триггера, прямой выход которого соединен с первым входом второго И элемента 2И-ИЛИ и с вто0 рым входом третьего элемента И, третий вход которого соединен с шиной Питание, вторые входы первого и второго И элемента 2И-ИЛИ соединены с входами Прямой и инЕиэрсный выходы основного триггера.

59. Мультиплексор-демультиплексор по

п. 6, отличающийся тем, что индикатор счетчика содержит два элемента 2И-ИЛИ и один элемент И, выход которого является выходом Индикация счетчика индикатора, вход Прямой выход основного первого

триггера из группы входов Счетчик соединен с первым входом первого И первого элемента 2И-ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого является выходом второго элемента 2И-ИЛИ, первые входы первого и второго И которого соединены с входами Прямой и инверсный выходы третьего вспомогательного триггера группы входов Счетчик соответственно, входы Прямой и инверсный выходы третьего основного триггера которой соединены с вторыми

./7

входами второго и первого И второго элемента 2И-ИЛИ соответственно, вход Инверсный выход первого вспомогательного триггера группы входов Счетчик соединен с вторым входом первого И первого элемента 2И-ИЛИ, первый вход второго И которого соединен с выходом Прямой выход второго основного триггера группы входов Счетчик, вход Инверсный выход

второго вспомогательного триггера которой соединен с вторым входом первого элемента 2И-ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИСКРЕТНЫЙ СОГЛАСОВАННЫЙ ФИЛЬТР | 2014 |

|

RU2589404C2 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| Устройство для передачи и приема данных | 1982 |

|

SU1098104A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Интерполятор | 1985 |

|

SU1413600A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для контроля многоканальной цифровой аппаратуры | 1986 |

|

SU1397860A1 |

| Устройство для вывода информации | 1983 |

|

SU1124278A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Микропрограммное вычислительное устройство | 1984 |

|

SU1229761A1 |

Изобретение относится к вычислительной технике и может быть использовано в составе специализированных быстродействующих вычислительных систем обработки сигналов. Цель изобретения - сокращение линий связи за счет мультиплексирования- демультиплексирования двух параллельных процессов и расширение функциональных возможностей за счет введения аппаратуры, позволяющей осуществлять самоконтроль. При построении параллельных Изобретение относится к вычислительной технике и может быть использовано в составе специализированных быстродействующих вычислительных систем обработки сигналов. Цель изобретения - сокращение линий связи за счет мультиплексирования-демультиплексирования двух параллельных процессов и расширение функциональных возможностей за счет введения аппаратуры, позволяющей осуществлять самоконтроль. На фиг. 1 изображена функциональная схема матричного мультиплексора-демульвычислительных систем, имеющих огромное число процессорных элементов, большое значение приобретает организация физических связей между ними. Матричный мультиплексор-демультиплексор позволяет в пять раз сократить число связей между конструктивными единицами. В матричном мультиплексоре-демультиплексоре используются специальные схемные решения, позволяющие проводить самодиагностику его, что позволяет локализовать неисправность без применения специальных тестов. В матричный мультиплексор-демультиплексор, содержащий счетчик, сдвиговый регистр, триггер, введены индикатор дешифрации, блок управления сдвиговым регистром, блок управления дополнительным сдвиговым регистром, дополнительный сдвиговый регистр, индикатор триггера, блок формирования исправности мультиплексора-демуль- типлексора, блок управления счетчиком, дешифратор, блок асинхронной передачи, два элемента И и элемент ИЛИ с соответствующими связями. 8 з.п.ф-лы, 9 ил. типлексора; на фиг. 2 - функциональная схема индикатора дешифрации; на фиг. 3 - фун кциональная схема блока управления сдвиговым регистром: на фиг. 4 - функциональная схема блока управления счетчиком; на фиг. 5 - функциональная схема блока асинхронной передачи; на фиг. 6 - функциональная схема блока формирования исправности; на фиг. 7 - функциональная схема триггера; на фиг. 8 - функциональная схема индикатора триггера; на фиг. 9 - функциональная схема индикатора счегчика. Матричный мультиплексор-демультиплексор содержит счетчик 1, сдвиговый реЁ О ел о ел ел ю

fpBi CJ

Фиг /

Инф11Инш2

2В

Фиг.З

Gz

Фиг.5

ФигЛ

VJ

Ё: TJ

ST

Фиг.8

инд. Сч

Фаг. 9

| Популярные цифровые микросхемы В.Л.Шило | |||

| Радио и связь, 1988 (микросхема К 155 КП1) | |||

| Паско | |||

| Схема сопряжения микропроцессора с телетайпом | |||

| - Электроника | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

Авторы

Даты

1991-06-15—Публикация

1988-10-03—Подача