Изобретение относится к вычислительной технике, может быть использовано для ввода цифровой информации в систему обработки данных в реальном масштабе времени и является усовершенствованием изобретения по авт. св. № 1571601.

Цель изобретения - повышение надежности за счет исключения потерь информации при полной загрузке блока памяти устройства.

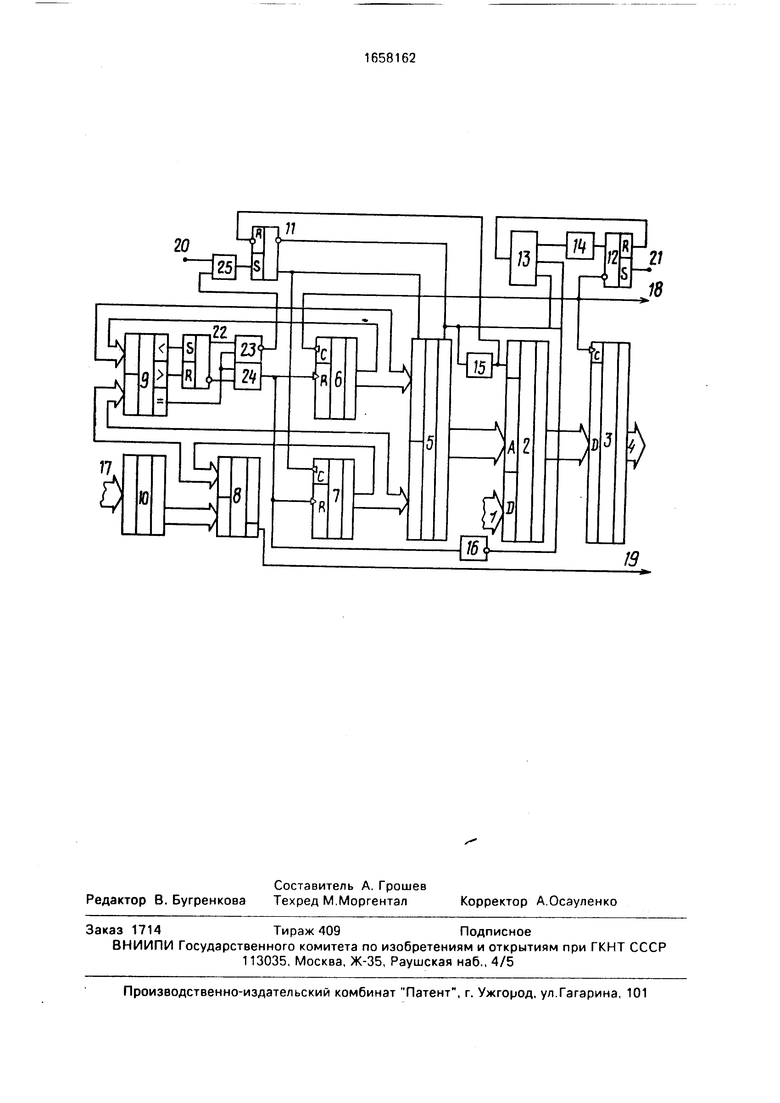

На чертеже изображена функциональная схема устройства.

Устройство ввода информации содержит информационные входы устройства 1, блок 2 памяти, буферный регистр 3, выходные шины 4, мультиплекстор 5, счетчик 6 чтения, счетчик 7 записи, сумматор 8, схему 9 сравнения, регистр 10 уставки, триггер 11 записи, триггер 12 чтения, элемент И 13, элементы 14 и 15 задержки, элемент НЕ 16, входную шину 17, шины 18 и 19 готовности, шину 20 чтения, шину 21 записи, триггер слежения 22, элемент И-НЕ 23, элемент И 24 и элемент И 25.

Устройство работает следующим образом.

В исходном состоянии счетчики 6 и 7, триггеры 11 и 22 находятся в состоянии 0м, триггер 12 - в состоянии 1. Элемент И 13 заперт логическим нулем с выхода элемента НЕ 16. Мультиплексор 5 подключен на направлении счетчика 6 чтения. В регистр 10 уставки занесен из процессора дополнительный код глубины заполнения блока 2 памяти. На шинах 18 и 19 готовности - логический нуль. Вторая шина 19 готовности включена в систему прерываний процессора.

При поступлении на вход устройства первого информационного слова, синхроимпульс его сопровождения поступает на шину 20 записи и через открытый элемент И 25 устанавливает триггер 11 записи в состояние 1. Последний переключает мультиплексор 5 на направление счетчика 7 записи и через второй элемент 15 задержки подает команду записи на управляющий вход блока 2 памяти, а затем сбрасывается в исходное

fe

сл

00

а

М

N3

состояние О. Элемент И 13, находящийся в цепи чтения, на время операции записи блокируется сигналом с инверсного выхода триггера 11 записи. Задний фронт сигнала с прямого выхода триггера 11 поступает на счетный вход счетчика 7 записи и наращивает его состояние на единицу, подготавливая тем самым следующий адрес для блока 2 памяти. Вследствие увеличения кода счетчика 7 записи на выходе Больше появляется логическая 1. а на выходе Равно логический О, который заблокирует элементы И-НЕ 23 и И 24. Сигнал логического нуля с выхода последнего, поступив на вход элемента НЕ 16 логической единицы с его выхода, открывает элемент И 13 и сигнал с выхода последнего устанавливает триггер 12 чтения в ноль. Передний фронт с инверсного выхода триггера 12 поступает па вход занесения буферного регистра 3 и информация из блока 2 памяти переписывается в буферный регистр, при этом на первой шине 18 готовности появляется логическая единица, сообщая процессору о наличии информации в устройстве. Второе и последующие информационные слова, поступившие на вход устройства числом не более, чем задано в регистре 10 уставки, будут обработаны аналогичным образом. В этот период процессор, если он освоПодил- ся от решения других задач, анализирует состояние первой шины 18 гоговносш. и в случае наличия логической едницы на последней, снимает информацию с выходных шич 4 буферного регистра 3. Строб приема информации в процессор поступает по шине 21 чтения на S - вход триггера 12 чтения и устанавливает его в состояние 1. При этом сигнал с инверсного выхода триггера 12 поступает на счетный вход счетчика 6 чтения и наращивает его состояние на единицу, Прямой выход триггера чтения через первый элемент 14 задержки выставляет запрос на вывод очередного слоьа из блока 2 памяти в буферный регистр 3. Если в блоке памяти есть хоть одно слово и в этот момент не идет операция записи, то сигна с выхода элемента И 13 сбрасывает в ноль триггер 12 чтения, который тем самым заноси: очередное слово в буферный регистр и выставляет сигнал на первой шине 18 готовности. Процессор может принять всю информацию, накопившуюся в блоке памяти устройства или только часть ее, если в этот момент для процессора появилась более важная задача. В последнем случае при заполнении блока 2 памяти до уровня, заданного в регистре 10 уставки, на выходе переноса сумматора 8, который вычитает из кода счетчика 7 записи код, занесенный в регистр, возникает логическая единица. Последняя по второй шине 19 готовности поступает в систему прерываний процессора и вызывает на выполнение программу приема из устройства, которая как было выше описано считывает всю информацию из устройства до конца.

При съеме последнего слова с буферного регистра 3 код счетчика 6 чтения догонит

код счетчика 7 записи и сравняется с ним, в результате на выходе Больше схемы 9 сравнения появится логический ноль, а на выходе Равно логическая единица, которая откроет элементы И-НЕ 23, И 24. Логическая единица с инверсного выхода триггера 22 слежения появляется на выходе члемантз И 24 и устанавливает устройство в исходное состояние. При полном заполнении блока 2 памяти :сод счетчика 7 записи

догонит код счетчика б чтения и сравняется с ним, однако а этом случае сброса устройства не произойдет, так как триггер 22 слежения, установленный до равенства, ситном с выхода схемы 9 сравнения

Меньше в состояние 1, включит элемент И-НЕ 23. Логический ноль с выхода последнего заблокирует элемент И 25 и запись в устройство прекратиться.

Устройство позволит предотвратить

сОоос устройства в исходное состояние при полном заполнении блока памяти устройст- зэ и тем самым исключить потери информации.

Формула изобретения

Устройство для сопряжения источника

информации с процессором по авт. св. № 1571601, отличающееся тем, что, с целью повышения надежности за счет исключения потерь информации, в него введены триггер слежения, второй и третий элементы И, элемент И-НЕ, причем установочный вход триггера слежения соединен с выходом Меньше схемы сравнения, вход сброса триггера слежения соединен с выходом Больше схемы сравнения, прямой выход триггера слежения соединен с первым входом элемента И-НЕ, второй вход которого и первый вход второго элемента И соединены с выходом Равно схемы сравнения,

агорой вход второго элемента И соединен с инверсным выходом триггера слежения, выход второго элемента И соединен с входами с/)роса счетчиков записи и чтения и входом элемента НЕ, выход элемента И-НЕ соедине-1 с первым входом третьего элемента И, второй вход которого соединен с входной шиной записи устройства, выход третьего элемента И соединен с установочным входом триггера записи

Р

18

Изобретение относится к вычислительной технике и может быть использовано для ввода информации в систему обработки в реальном масштабе времени. Цель изобретения - повышение надежности за счет исключения потерь информации при полной загрузке блока памяти устройства. Устройство содержит блок памяти, буферный регистр, мультиплексор, счетчики записи и чтения, сумматор, схему сравнения, триггеры записи и чтения, три элемента И, два элемента задержки, элемент НЕ, два элемента И-НЕ. 1 ил.

| Устройство для сопряжения источника информации с процессором | 1988 |

|

SU1571601A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1991-06-23—Публикация

1989-04-24—Подача