Изобретение относится к вычислительной технике, предназначено для ввода цифровой информации в процессор системы реального времени и является усовершенствованием изобретения по авт. св. №1571601.

Цель изобретения - повышение быстродействия.

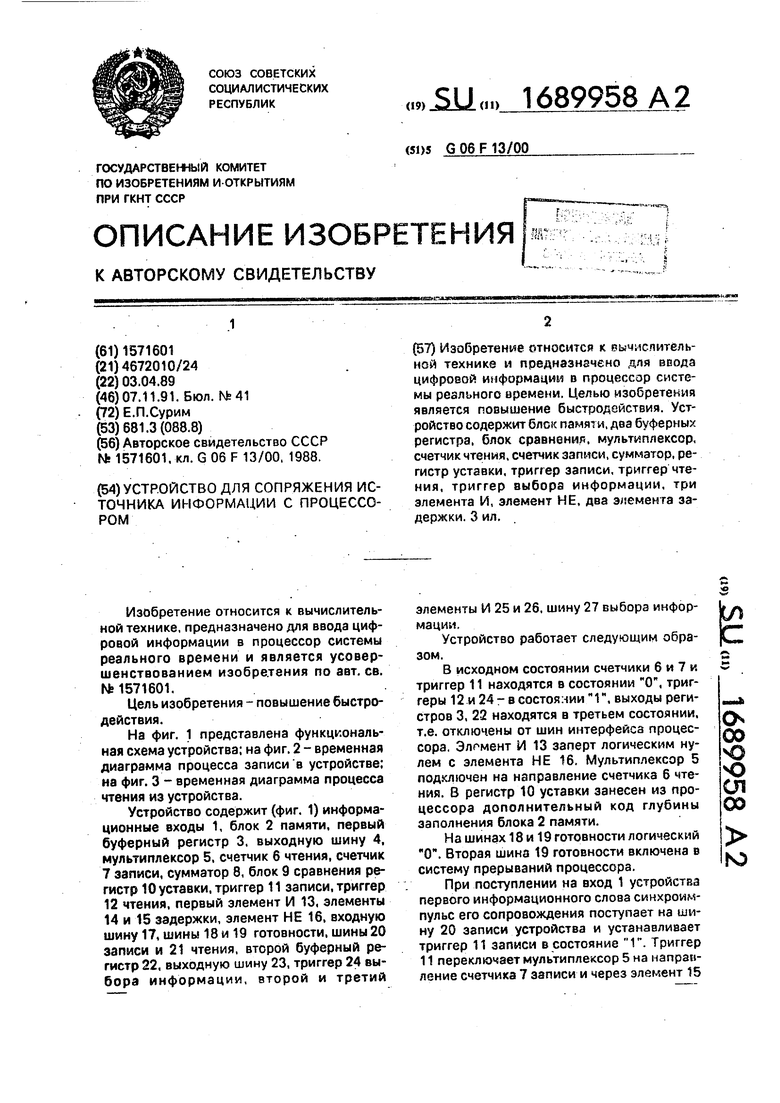

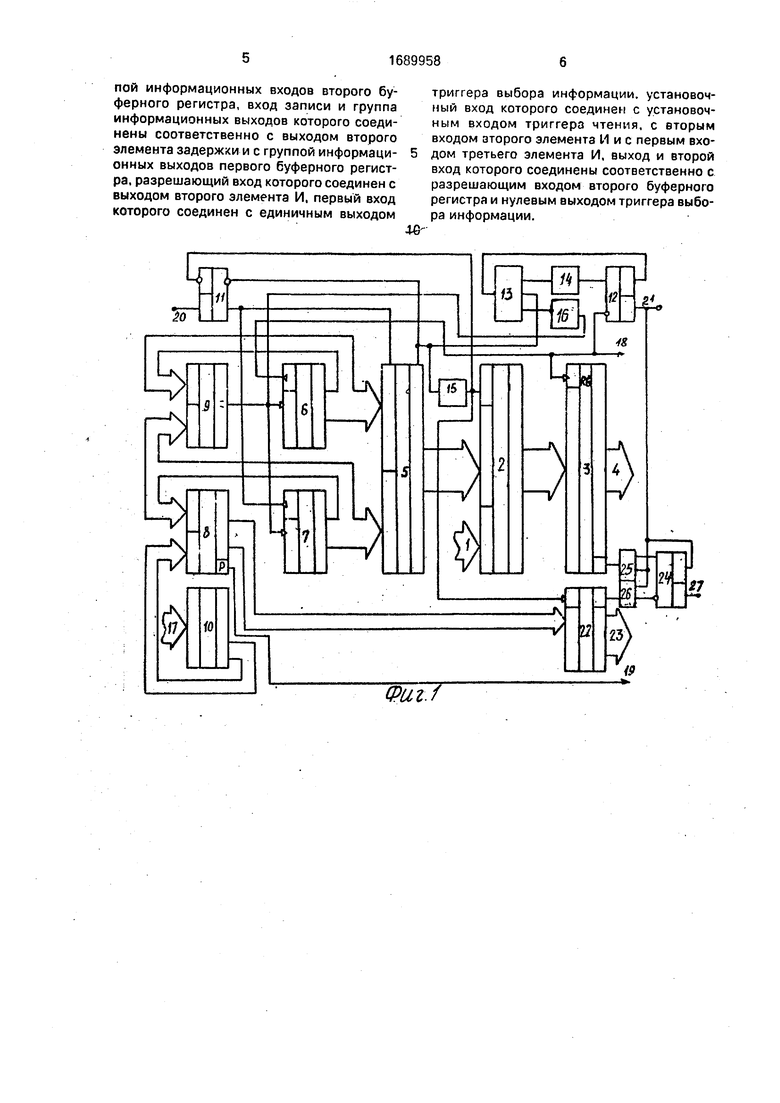

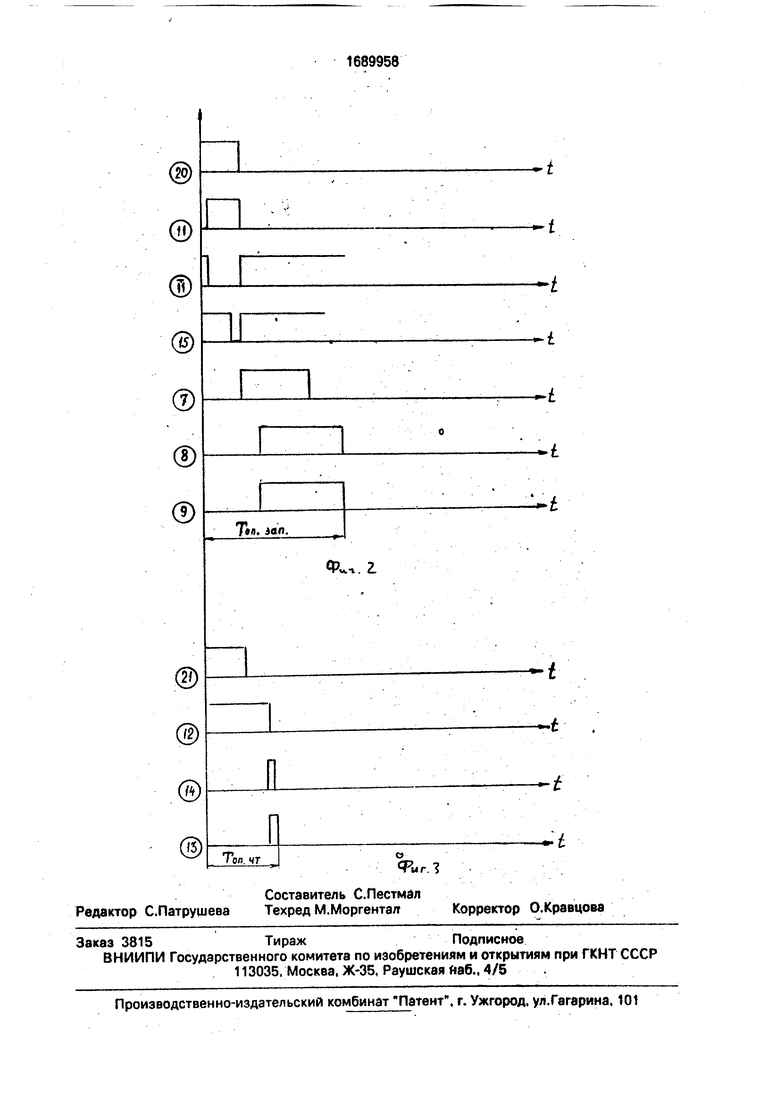

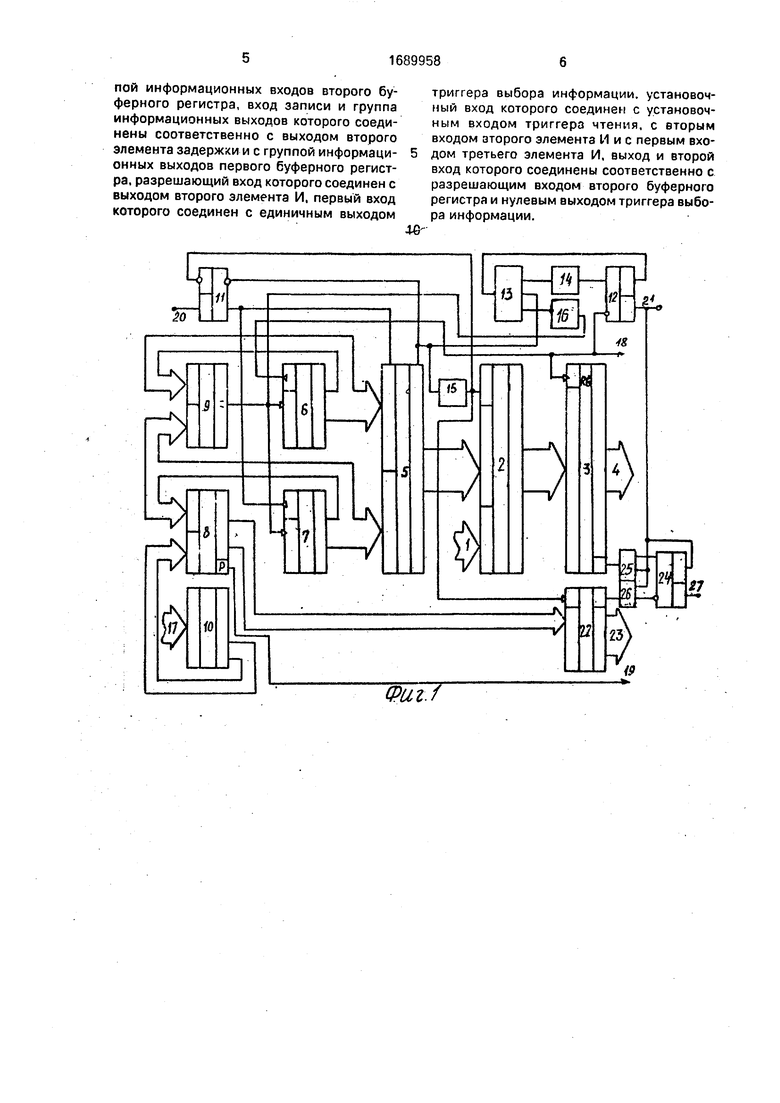

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - временная диаграмма процесса записи в устройстве; на фиг. 3 - временная диаграмма процесса чтения из устройства.

Устройство содержит (фиг. 1) информационные входы 1, блок 2 памяти, первый буферный регистр 3, выходную шину 4, мультиплексор 5, счетчик 6 чтения, счетчик 7 записи, сумматор 8, блок 9 сравнения регистр 10 уставки, триггер 11 записи, триггер 12 чтения, первый элемент И 13, элементы 14 и 15 задержки, элемент НЕ 16, входную шину 17, шины 18 и 19 готовности, шины 20 записи и 21 чтения, второй буферный регистр 22, выходную шину 23, триггер 24 выбора информации, второй и третий

элементы И 25 и 26, шину 27 выбора информации.

Устройство работает следующим образом.

В исходном состоянии счетчики 6 и 7 и триггер 11 находятся в состоянии О, триггеры 12 и 24 - в состоянии Г, выходы регистров 3, 22 находятся в третьем состоянии, т.е. отключены от шин интерфейса процессора. Элемент И 13 заперт логическим нулем с элемента НЕ 16. Мультиплексор 5 подключен на направление счетчика 6 чтения. В регистр 10 уставки занесен из процессора дополнительный код глубины заполнения блока 2 памяти.

На шинах 18 и 19 готовности логический 0м. Вторая шина 19 готовности включена в систему прерываний процессора.

При поступлении на вход 1 устройства первого информационного слова синхроимпульс его сопровождения поступает на шину 20 записи устройства и устанавливает триггер 11 записи в состояние Г. Триггер 11 переключает мультиплексор 5 на напран- ление счетчика 7 записи и через элемент 15

О 00

ч ю ел

00

ю

задержки подает команду записи на вход блока 2 памяти, а затем устанавливает себя (триггер 11} в исходное состояние О. Элемент И 13, находящийся в цепи чтения, на время операции записи блокируется сигналом с нулевого выхода триггера 11 записи. Задний фронт сигнала с единичного выхода триггера 11 поступает на счетный вход счетчика 7 записи, наращивает его состояние на единицу, подготавливая тем самым следующий адрес, Передний фронт сигнала с нулевого выхода триггера 11 через элемент 15 задержки поступает на вход записи регистра 22 и тем самым в регистр с выхода сумматора 8 переписывается код числа свободных ячеек в блоке 2 памяти. Вследствие наличия разных кодов на входах блока 9 сравнения на его выходе появится логический О, который через элемент НЕ 16 откроет элемент И 13, сигнал с выхода последнего установит в О триггер 12 чтения.

Передний фронт сигнала с нулевого выхода триггера 12 чтения поступит на вход записи буферного регистра 3, и информация из блока 2 памяти перепишется в регистр 3, при этом на первой шине 18 готовности появится логическая 1, сообщая процессору о наличии информации в устройстве. Второе и последующие информационные слова, поступающие на вход устройства, числом не более, чем задано в регистре 10 уставки, обрабатываются устройством аналогичным образом. В этот период процессор, если он освободился от решения других задач, анализирует состояние первой шины 18 готовности и, в случае наличия логической 1 на последней, процессор выдает по шине 21 чтения импульс приема, который устанавливает триггер 12 чтения о состояние 1, а состояние 1 триггера 24 подтверждает, при этом импульс проходит через открытый логической 1 с единичного выхода триггера 24 элемент И 25 на разрешающий вход регистра 3, подключая последний на время действия импульса к входным шинам интерфейса процессора, который считывает с них информацию. Единичный выход триггера 12 чтения через элемент 14 задержки выставляет запрос на выход очередного слова из блока 2 памяти в буферный регистр 3, а нулевой выход триггера 12 передним фронтом сигнала модифицирует счетчик 6. Если в блоке 2 памяти есть хоть одно слово и в этот момент не идет операция записи, т.е. триггер 11 записи находится з состоянии О, то сигнал с выхода элемента И 13 сбрасывает в ноль.триггер 12 чтения, который

тем самым заносит очередное слово из блока 2 памяти в буферный регистр 3.

При сьеме последнего слова с буферного регистра 3 код счетчика 6 чтения совпадает с кодом счетчика 7 записи и на выходе блока 9 сравнения появится сигнал равенства, который своим передним фронтом установит в О счетчики б и 7 и через элемент НЕ 16 заблокирует элемент И 13. Триггер 12

0 чтения останется в состоянии 1й, а первая шина 18 готовности - в состоянии О.

Если процессор занят решением других задач и не анализирует состояние первой шины 18 готовности, то при заполнении бло5 ка 2 памяти до уровня, заданного в регистре 10 уставки, на выходе переноса сумматора 8, который вычитает из кода счетчика 7 записи код, хранящийся в регистре 10 уставки, возникает логическая 1, которая по второй

0 шине 19 готовности поступает в систему прерываний процессора и вызывает на выполнение программу приема из устройства. Последняя считывает информацию из устройства до конца. Если процессору необхо5 димо знать через какой интервал времени заполнится блок 2 памяти устройства и появится сигнал прерывания, что необходимо перед запуском программы, прерывание которой запрещено, то процессор выдает им0 пульс по шине 27 выбора и устанавливает триггер 24 в состояние О. Логическая 1 с нулевого выхода триггера 24 открывает элемент И 26, а логический О с единичного выхода триггера 24 блокирует элемент И 25.

5 Таким образом, при поступлении на шину 21 импульса приема к выходным шинам интерфейса процессора подключается второй буферный регистр 22 и в процессор поступает код числа свободных ячеек блока

0 2 памяти устройства, зная скорость поступления информации, процессор вычисляет время, оставшееся до появления сигнала прерывания устройства ввода, и использует йту информацию для принятия решения о

5 даль-нешем ведении вычислительного процесса. Приведение триггера 24 выбора в исходное состояние осуществляется по заднему фронту импульса приема. Формула изобретения

0 Устройство для сопряжения источника информации с процессором по авт. св. № 1571601, отличающееся тем, что, с целью повышения быстродействия, в устройство введены второй буферный регистр,

5 триггер выбора информации, два элемента И, причем вход сброса триггера выбора информации является входом устройства для подключения к выходу выбора информации процессора, при этом группа информационных выходов сумматора соединена с труппой информационных входов второго буферного регистра, вход записи и группа информационных выходов которого соединены соответственно с выходом второго элемента задержки и с группой информационных выходов первого буферного регистра, разрешающий вход которого соединен с выходом второго элемента И, первый вход которого соединен с единичным выходом

€триггера выбора информации, установочный вход которого соединен с установочным входом триггера чтения, с вторым входом второго элемента И и с первым входом третьего элемента И, выход и второй вход которого соединены соответственно с разрешающим входом второго буферного регистра и нулевым выходом триггера выбора информации.

Изобретение относится к вычислительной технике и предназначено для ввода цифровой информации в процессор системы реального времени. Целью изобретения является повышение быстродействия. Устройство содержит блек памя и, два буферных регистра, блок сравнения, мультиплексор, счетчик чтения, счетчик записи, сумматор, регистр уставки, трип ер записи, триггер чтения, триггер выбора информации, три элемента И, элемент НЕ, два элемента задержки. 3 ил.

Фиг-f

| Устройство для сопряжения источника информации с процессором | 1988 |

|

SU1571601A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-07—Публикация

1989-04-03—Подача