Изобретение относится к вычислительной технике и предназначено для ввода цифровой информации в процессоры информационных систем реального времени,

Целью изобретения является повышение быстродействия устройства.

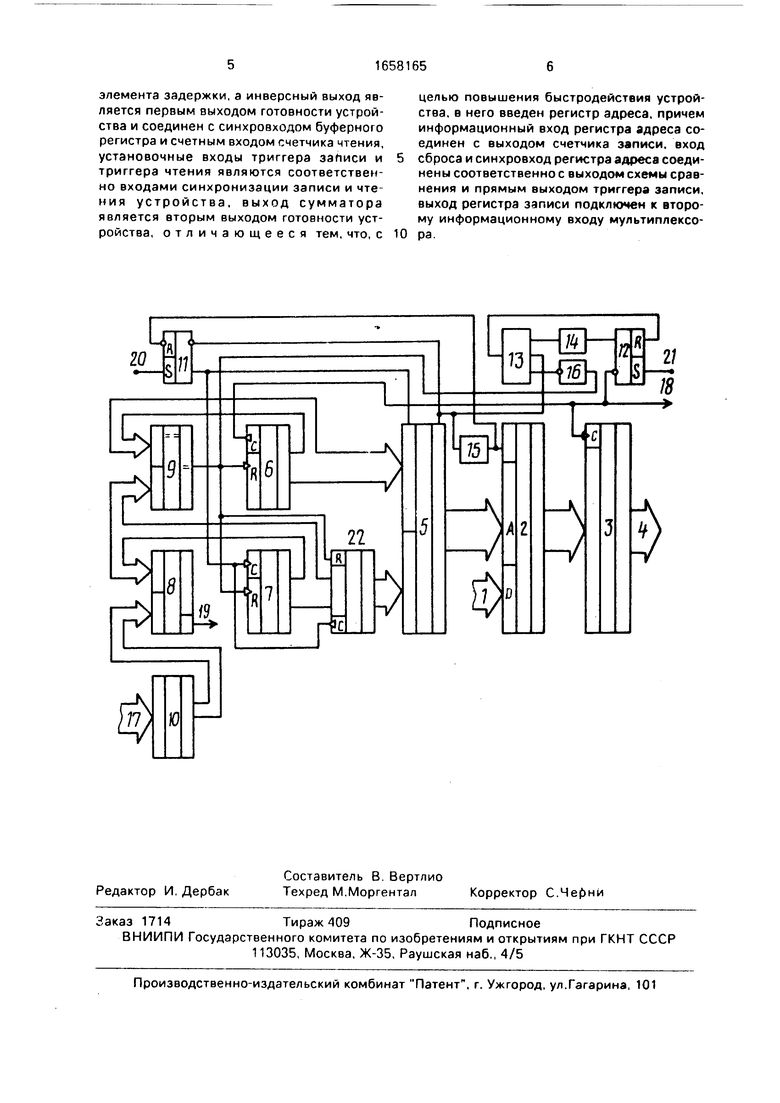

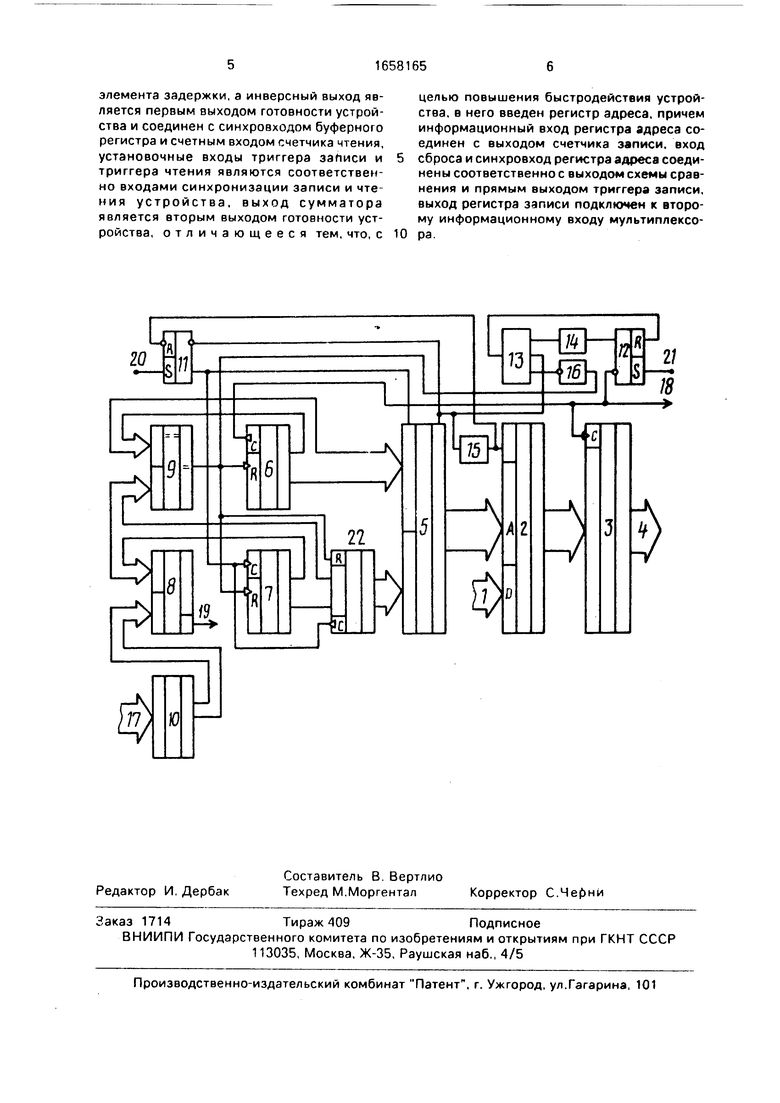

На чертеже представлена функциональная схема устройства, содержащего информационный вход 1 устройства, блок 2 памяти, буферный регистр 3, информационный выход 4, мультиплексор 5, счетчики чтения 6 и записи 7, сумматор 8, схему 9 сравнения, регистр 10 уставки, триггеры записи 11 и чтения 12, элемент И 13, второй 14 и первый 15 элементы (линии) задержки, элемент НЕ 16, вход 17 задания глубины заполнения памяти, выходы (шины) 18 и 19 готовности, входы (шины) 20 и 21 синхронизации записи и чтения и регистр 22 адреса.

Устройство работает следующим образом.

В исходном состоянии счетчики 6 и 7, триггер 11 и регистр 22 находятся в состоянии О, триггер 12 - в состоянии 1. Элемент И 13 заперт логическим нулем с выхода элемента НЕ 16. Мультиплексор 5 подключен на направление счетчика 6 чтения. В регистр 10 уставки занесен из процессора дополнительный код глубины заполнения блока 2 памяти. На шинах 18 и 19 готовности присутствует логический О.

Шина 19 готовности включена в систему прерываний процессора. При поступлении на вход 1 устройства первого информационного слова синхроимпульс его сопровождения поступает на шину 20 и устанавливает триггер 11 записи в состояние 1. Последний переключает мультиплексор 5 на направление счетчика 7 записи и через линию 15 задержки подает команду записи на управляющий вход блока 2 памяти, а затем сбрасывается в исходное состояние О. Одновременно передний фронт сигнала с пря4V

Ј

о

CJ

а

а а

мого выхода триггера 11 поступает на счетный вход счетчика 7 записи и наращивает его состояние на 1. Задний фронт того же сигнала заносит новое состояние счетчика 7 записи в регистр 22. К моменту занесения нового состояния счетчика 7 записи в регистр 22 адреса заканчивается и переходный процесс в сумматоре 8. Таким образом, время операции ззлиси состоит из времени установки триггера 11 в состояние 1, времени переключения MV/H типле: сора 5, времени записи ь 2 памяти куда входит и время установки триггера 11 записи в сос О- оние О. Одновременно с переходным процессом в сумматоре 8 заканчивается и переходный процесс в схеме 9 сравнения -i на ее выхода вследствие того, что код счетчика 7 записи стал больше кода счетчика 6 чтения, появляется логический С и поступая на вход элемента Н Е 16. Сигнал с выхода последнего открывает элемент И 13, з сигнал с инверсного выхода триггера 11, одновременно или чуть позже, разблокирует элемент И 13.

В результате логическая единица с выхода элемента И 13 поступает на вход сброса триггера 1 чтения и устанавливает эго я О, при JTOM передний фронт сигнал с инверсного выхода триггера 12 поступает на вход занесения буферного ре(истра 3 и информация из блока 2 памяти переписывается в буферный регистр. На шине 18 готовности, которая связана с инверсным выходом триггера 12 чтений, появля-мся логическая 1, сообщая процессору о наличии информации в устройстве.

Второе и последующие информационные слова, поступившие на вход устройства числом не более, чем задано в регистре 10 уставки, записываются в блок 2 памяти анч- логично.

В этот период процессор, если он свободен от решения других задач, анализирует состояние первой шины 18 готовности и в случае наличия логической I на последней снимает информацию с выхода 4. Строб приема информации в процессор поступает по шине 21 на вход триггера 12 чтения и устанавливает его в состояние 1 . Спад сигнала с инверсного выхода триггера 12 поступает на счетный вход счетчика 6 чтения и наращивает его состояние на 1. Прямой выход триггера 12 чтения через линию 14 задержки выставляет запрос на выход очередного слова из блока 2 памяти в буферный регистр 3. Если в блоке 2 памяти есть информация и в этот момент не идет операция записи, то сигнал с выхода элемента И 13 сбрасывает в О триггер 12, который тем самым заноси г очередное слово о буферный

регистр 3 и выставляет сигнал на шине 18 готовности. Процессор может принять всю информацию, накопившуюся в блоке 2 памяти, или только ее часть. В последнем случае при заполнении блока 2 памяти до уровня, заданного в регистре 10 уставки, на нылодг- переноса сумматора 8 возникает ло- гическая 1 которая по второй шине 19 готовности поступает в систему прерыва0 ний процессора и вызывает на выполнение программу приема. Последняя считывает всю информацию из устройства до конца.

При сьеме последнего слова с выхода 4 устройства код счетчика 6 чтения СОВПЯЛЯРТ

5 с кодом счетчика 7 запаси и на выходе схемы 0 срнрн ния появляется сигнал равенства, который своим передним фронтом устэнавличает оба счетчика и регистр 22 в О1 и через элемент НЕ 16 блокирует эле0 мент И 11 Триггер 12 чтения остается при и состоянии 1, а первая шина 18 готовности в состоянии О.

Формула изобретения Устройство для сопряжения источника

5 информации с процессором, содержащее блок памяти, выход которого соединен с информационным яходом буферного регистра выход которого является информационным выходом устройства,

0 с чтения, выход которого подключен первым информационным входам схемы сравнения и мультиплексора, счетчик записи, еыход которою соединен с вторым информационным входом схемы сравнения и

5 .шрвым информационным входом сумматора, вторым информационным входом соединенного с выходом регистра уставки, вход которого является входом задания глубины заполнения памяти устройства, триггер чте0 ния триггер записи, элемент И, элемент НЕ и два элемента задержки, причем инверсной РЫХОД триггера записи соединен с первом входом элемента И, первым управляющим входом мультиплексора и че5 поз первый элемент задержки - с входом сброса триггера записи и управляющим входом блока памяти, информационный вход которого является информационным входом устройства, а вход адреса - соединен с

0 выходом мультиплексора, вторым управляющим входом подключенного к прямому выходу триггера записи и счетному входу счетчика записи вход сброса которого соединен с выходом схемы сравнения, входом

5 сброса счетчика чтения и через элемент НЕ с вторым входом элемента И, третьим входом и выходом подключенного соответст венно к выходу второго элемента задержки и рхсду сброс 1 тричера чтения, прямой вы ход которого соединен с входом второго

элемента задержки, а инверсный выход является первым выходом готовности устройства и соединен с синхровходом буферного регистра и счетным входом счетчика чтения, установочные входы триггера записи и триггера чтения являются соответственно входами синхронизации записи и чтения устройства, выход сумматора является вторым выходом готовности устройства, отличающееся тем, что, с

целью повышения быстродействия устройства, в него введен регистр адреса, причем информационный вход регистра адреса соединен с выходом счетчика записи, вход сброса и синхровход регистра адреса соединены соответственно с выходом схемы сравнения и прямым выходом триггера записи, выход регистра записи подключен к второму информационному входу мультиплексора.

Изобретение относится к вычислительной технике и предназначено для сопряжения процессора с различными источниками информации, например телеметрическими станциями, цифровыми датчиками и т. п., в основном для работы в реальном режиме времени. Цель изобретения - повышение быстродействия устройства путем параллельного выполнения микроопераций при записи. Цель достигается тем, что в устройство, содержащее блок памяти, мультиплексор, счетчики и триггеры записи и чтения, буферный регистр, сумматор, регистр уставки, схему сравнения, два элемента задержки, элемент И и элемент НЕ, введен регистр адреса. 1 ил.

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1383375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источника информации с процессором | 1988 |

|

SU1571601A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-23—Публикация

1989-05-22—Подача