Изобретение относится к вычислительной технике и может быть использовано для ввода цифровой информации в процессор в реальном или квазиреальном масштабе времени.

Целью изобретения является повышение быстродействия устройства.

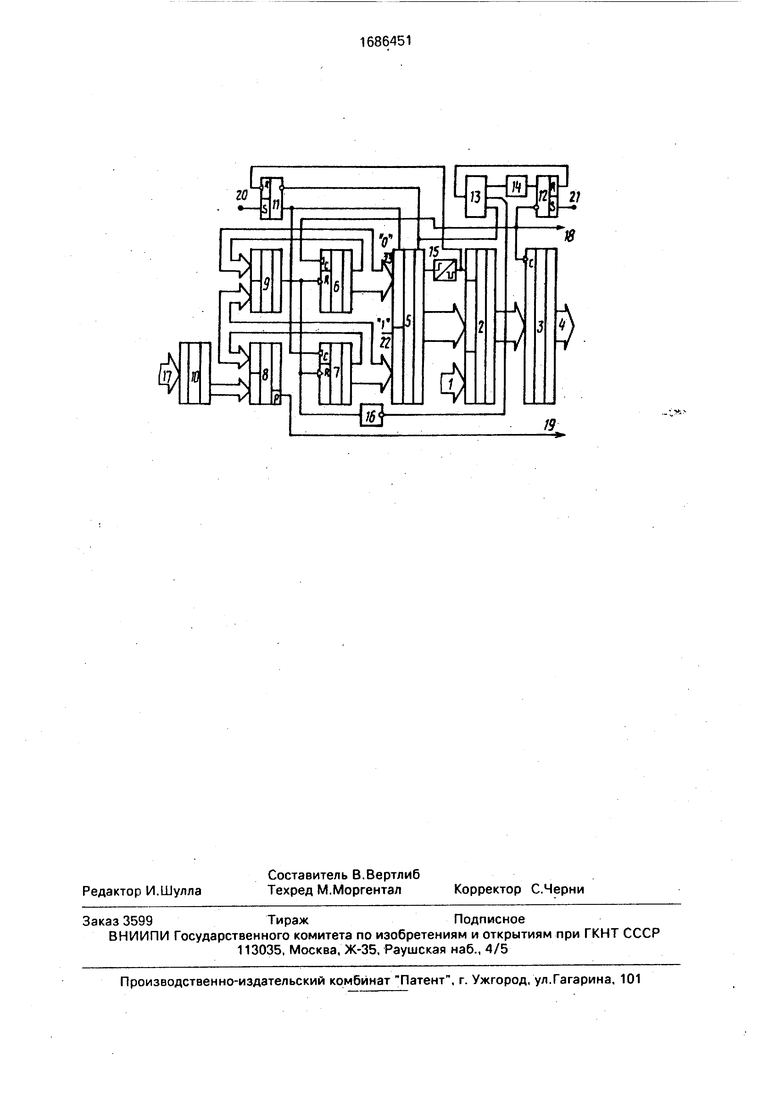

На чертеже представлена схема устройства.

Устройство содержит входную информационную шину 1 устройства, блок 2 памяти, буферный регистр 3, группу выходных информационных шин 4 устройства, мультиплексор 5, счетчики чтения 6 и записи 7, сумматор 8. схему 9 сравнения, регистр 10 уставки, триггеры записи 11 и чтения 12, элемент И 13, элемент 14 задержки, формирователь 15 импульса записи, элемент НЕ 16, входные шины 17 уставки устройства, первую 18 и вторую 19 выходные шины готовности устройства, входные шины записи 20 и чтения 21 устройства, входы 22 и 23 дополнительных разрядов первой и второй

групп информационных входов мультиплексора 5.

Устройство работает следующим образом.

В исходном состоянии счетчики 6 и 7 и триггер 11 находятся всостоянии О, а триггер 12 - в состоянии 1. Элемент И 13 заперт логическим О с выхода элемента НЕ 16. Мультиплексор 5 подключен на направление счетчика 6 чтения. В регистр 10 уставки занесен дополнительный код глубины заполнения блока 2 памяти. На шинах 18 и 19 готовности - логический О.

При поступлении на шину 1 первого информационного слова синхроимпульс его сопровождения поступает по шине 20 записи на вход триггера 11 записи и устанавливает его в состояние 1. Последний переключает мультиплексор 5 на направление счетчика 7 записи, при этом на вход формирователя 15 поступает логическая 1 с входа 22 мультиплексора.

По переднему фронту поступившего на вход сигнала формирователь 15 выдает имс/

с

о

00 О СП

пульс на управляющий вход блока 2 памяти и вход установки в О триггера 11 записи, последний сбрасывается по заднему фронту импульса. Элемент И 13 на время операции записи блокируется сигналом с инверсного выхода триггера 11 записи. По заднему фронту сигнала с прямого выхода триггера 11 счетчик 7 наращивает адрес записи, вследствие этого на выходе схемы сравнения появляется логический О, который через элемент НЕ 16 открывает элемент И 13 и сигнал с выхода последнего устанавливает в О триггер 12.

Передний фронт сигнала с инверсного выхода триггера 12 чтения поступает на вход буферного регистра 3 и информация из блока 2 памяти переписывается в регистр 3, при этом на шине 18 готовности появляется логическая 1. При записи в блок 2 памяти до уровня, заданного в регистре 10 уставки, на выходе переноса сумматора 8 возникает логическая единица, которая по шине 19 готовности поступает в систему прерываний процессора.

Процессор может начать считывать информацию из устройства по сигналу на шине 18 готовности и обязан считать всю информацию по сигналу на шине 19 готовности. Строб приема информации и процессор поступает по шине 21 чтения на вход триггера 12 чтения и устанавливает его в состояние 1. Сигнал с инверсного выхода триггера 12 поступает на счетный вход счетчика 6 чтения и наращивает его состояние. Прямой выход триггера 12 через элемент 14 задержки выставляет запрос на вывод очередного слова из блока 2 памяти в буферный регистр 3. Если в эгот момент не идет операция записи и в блоке 2 есть хотя бы одно слово, то сигнал с выхода элемента И 13 сбрасывает в 0й триггер 12 чтения, тем самым в регистр 3 заносится очередное слово. После приема последнего слова вследствие равенства кодов счетчиков 6 и 7 с выхода схемы 9 сравнения устанавливает устройство в исходное состояние.

Формула изобретения Устройство для сопряжения источника информации с процессором, содержащее триггер записи и триггер чтения, установочные входы которых являются соответственно входными шинами записи и чтения уст ройства, буферный регистр, группа выходов которого является группой выходных информационных шин устройства, а группа

информационных входов соединена с группой выходов блока памяти, счетчик чтения, счетным входом соединенный с синхровхо- дом буферного регистра, первой выходной шиной готовности устройства и инверсным

выходом триггера чтения, элемент И, выходом соединенный с входом сброса триггера чтения, а первым входом через элемент задержки - с прямым выходом триггера чтения, схему сравнения, выход которой

соединен с входами сброса счетчика записи и счетчика чтения и через элемент НЕ - с вторым входом элемента И, третьим входом подключенного к инверсному выходу триггера записи, мультиплексор, сумматор и регистр уставки, причем прямой выход триггера записи соединен со счетным входом счетчика записи, группа выходов которого соединена с первыми группами информационных входов схемы сравнения,

мультиплексора и сумматора, выход переноса которого является второй выходной шиной готовности устройства, а вторая группа информационных входов соединена с группой выходов регистра уставки, группа

информационных входов которого является шиной уставки устройства, группа выходов счетчика чтения соединена с вторыми группами информационных входов схемы сравнения и мультиплексора, группа

управляющих входов которого соединена с прямым и инверсным выходами триггера записи, а группа выходов - с группой адресных входов блока памяти, группа информационных входов которого является

входной информационной шиной устройства, отличающееся тем, что, с целью повышения быстродействия, в него введен формирователь импульса записи, причем дополнительный выход мультиплексора соединен через формирователь импульса записи с входом сброса триггера записи и управляющим входом блока памяти, дополнительные разряды первой и второй групп информационных входов мультиплексора

соединены соответственно с шинами единичного и нулевого потенциалов устройства.

Изобретение относится к вычислительной технике и может быть использовано для ввода в процессор цифровой информации в реальном масштабе времени или предварительно записанной на магнитный носитель. Цель изобретения -- повышение быстродействия устройства при сохранении надежности записи. Цель достигается тем, что в устройство, содержащее блок памяти, мультиплексор, элемент НЕ, элемент И, счетчики и триггеры записи и чтения, схему сравне ния, сумматор, буферный регистр и ретстр уставки, введен формирователь импульса записи. 1 ил.

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1383375A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функции @ | 1988 |

|

SU1541601A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1991-10-23—Публикация

1989-11-27—Подача