4

4;

со

1U

Изобретение относится к вычислительной технике и может быть ис пользовано для построения запоминающих устройств в виде интегральных схем.

Цель изобретения - упрощение устройства за счет сокращения количества шин программирования.

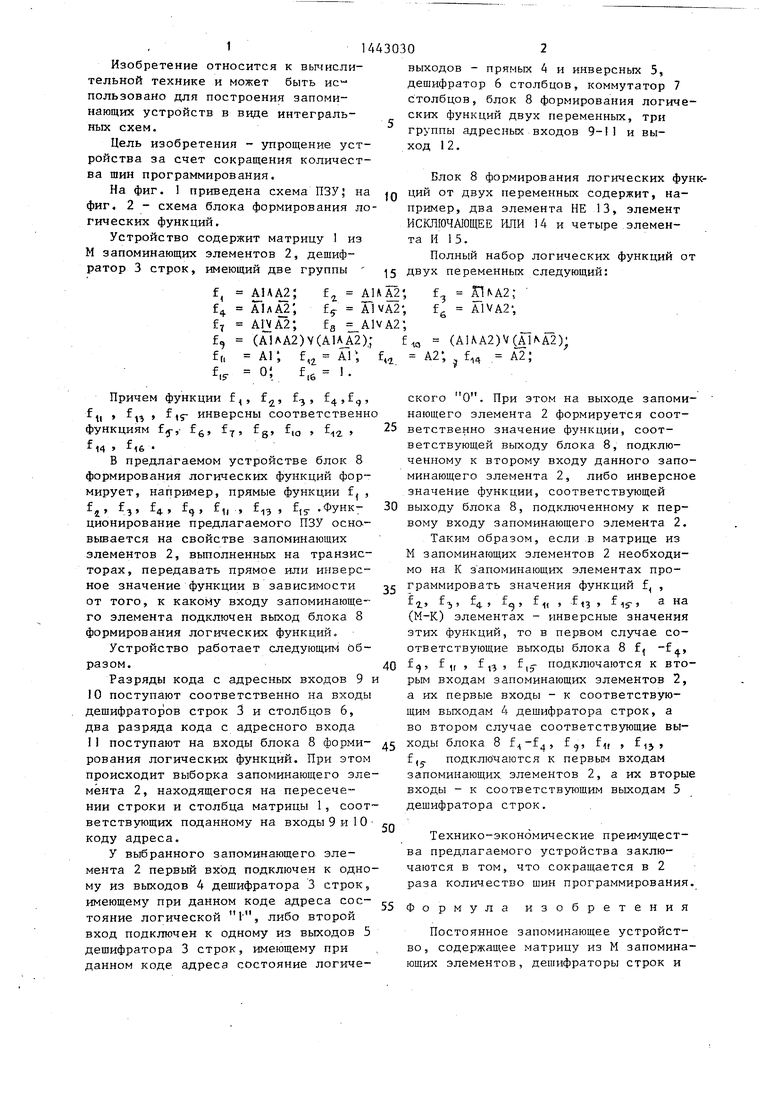

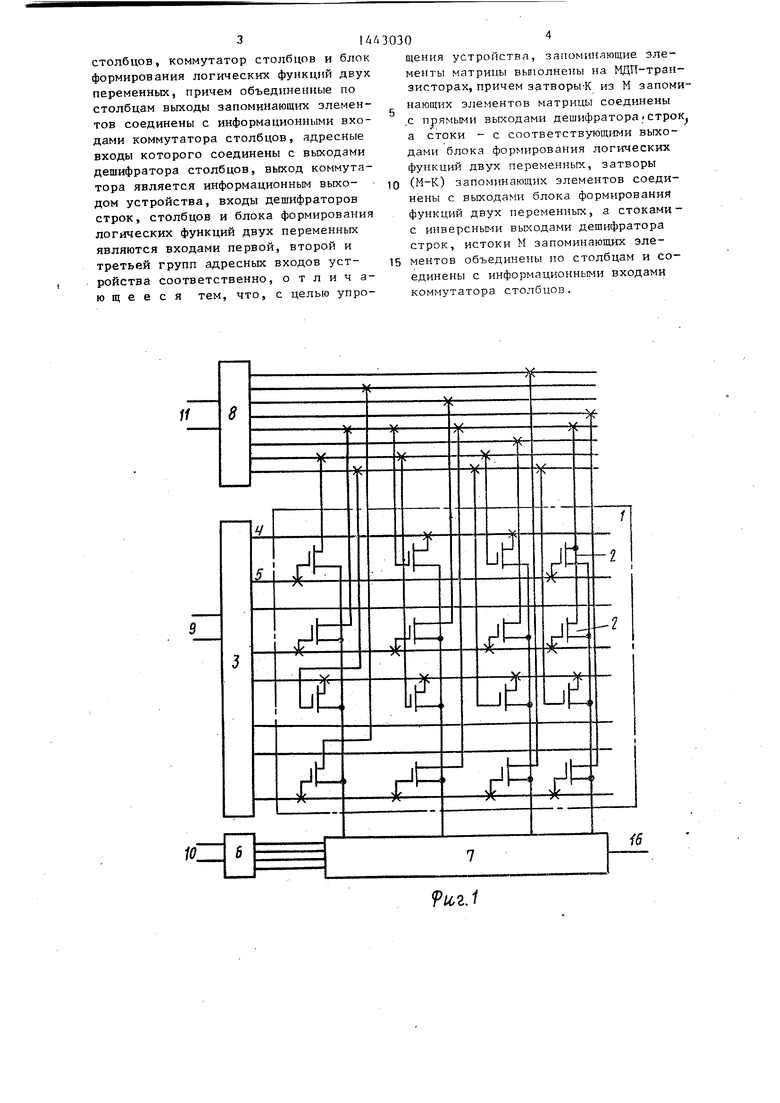

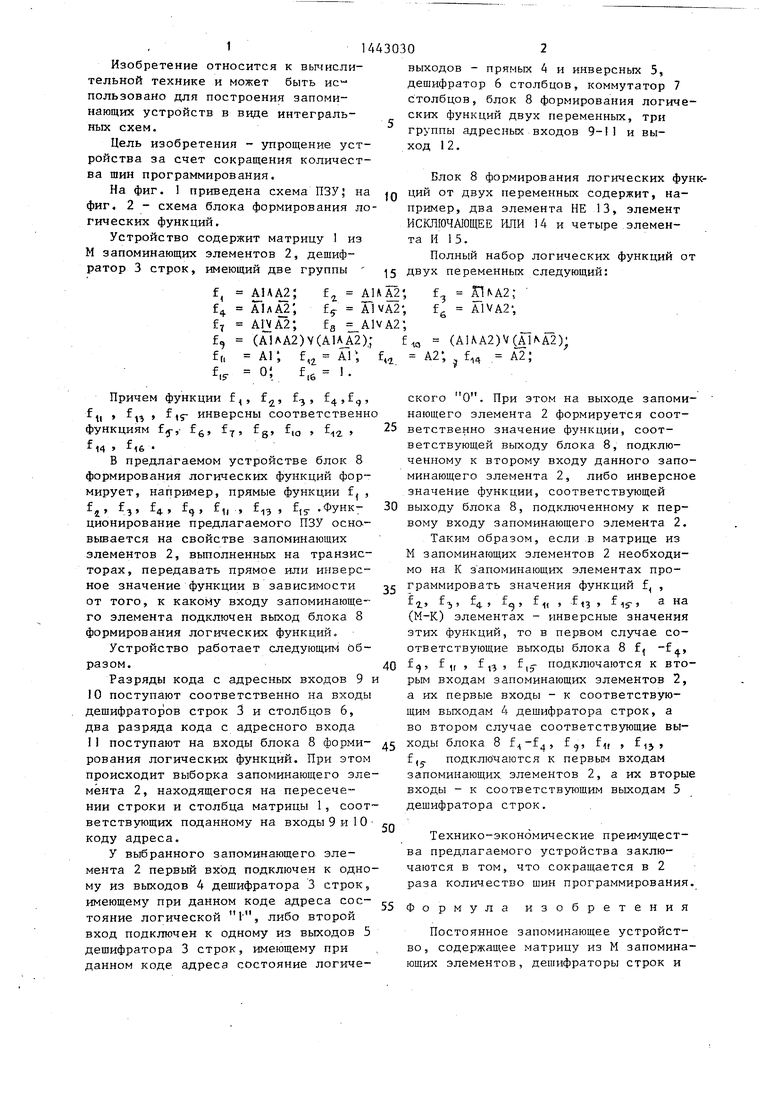

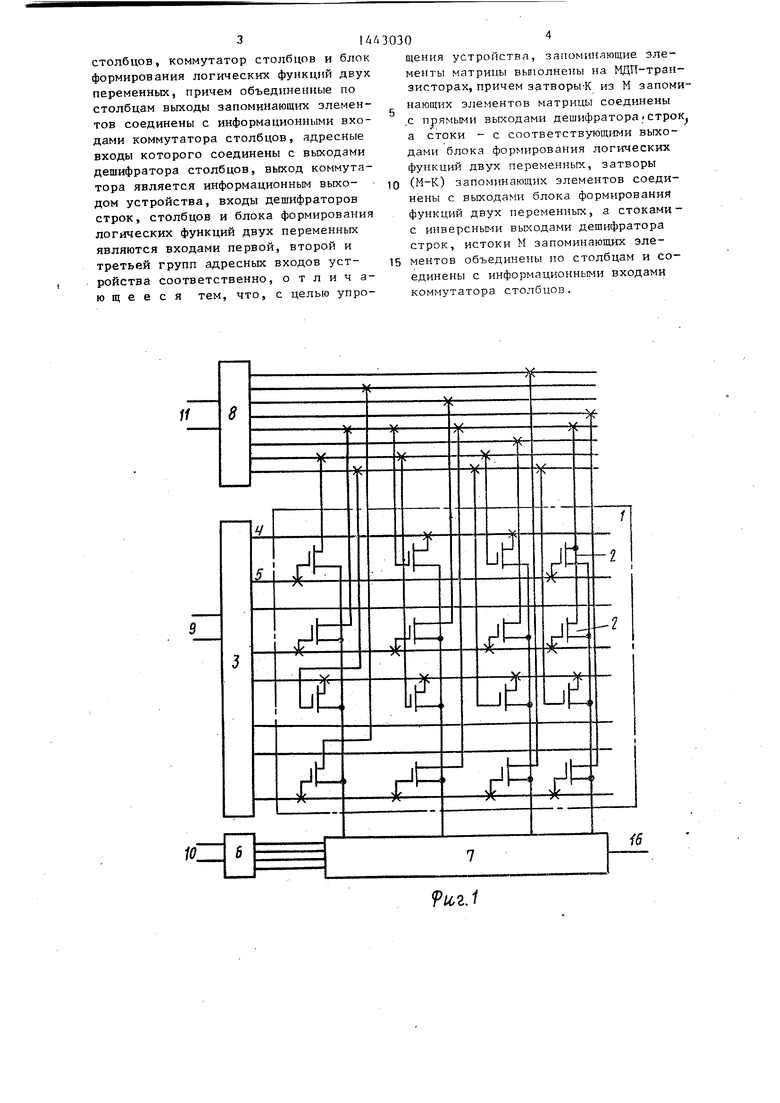

На фиг. 1 приведена схема ПЗУJ на фиг. 2 - схема блока формирования логических функций.

Устройство содержит матрицу 1 из М запоминающих элементов 2, дешифратор 3 строк, имеющий две группы

2

выходов - пряных 4 и инверсных 5, дешифратор 6 столбцов, коммутатор 7 столбцов, блок 8 формирования логических функций двух переменных, три группы адресньк входов и выход 12.

Блок 8 формирования логических функций от двух переменных содержит, например, два элемента НЕ 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и четыре.элемента И 15.

Полный набор логических функций от двух переменных следующий:

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1982 |

|

SU1096694A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для вычисления булевых функций | 1988 |

|

SU1501033A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Многоканальный счетчик импульсов | 1987 |

|

SU1508342A1 |

| Ассоциативная запоминающая матрица | 1982 |

|

SU1112410A1 |

Постоянное запоминающее устройство предназначено для использования в области вычислительной техники для создания БИС ЗУ. Целью изобретения является упрощение устройства за счет уменьшения количества шин программирования. Поставленная задача решается тем, что в качестве запоминающего элемента (ЗЭ) используется НДП-транзистор, и дешифратор строк имеет,прямые и инверсные вьосоды, что обеспечивает использование ЗЭ как передающего или инвертирующего в зависимости от программируемой информации, , следствием чего является уменьшение количества шин, подводимых к каждому ЗЭ, приблизительно на 40%. 2 ил.

Причем функции f, f, f , f,f, f,5- инверсны соответственн

-, функциям

Мб

Eg,

-т

f 14

-8

- (1

В предлагаемом устройстве блок 8 формирования логических функций формирует, например, прямые функции f ,

fj, з f 11 13 15- .Функционирование предлагаемого ПЗУ основывается на свойстве запоминающих элементов 2, выполненных на транзисторах, передавать прямое или инверсное значение функции в зависимости от того, к какому входу запоминающего элемента подключен выход блока 8 формирования логических функций.

Устройство работает следующим образом.

Разряды кода с адресных входов 9

10поступают соответственно на входы дешифраторов строк 3 и столбцов 6, два разряда кода с адресного входа

11поступают на входы блока В форми- рования логических функций. При этом происходит выборка запоминающего элемента 2, находящегося на пересечении строки и столбца матрицы 1, соответствующих поданному на входы 9 и 1 О коду адреса.

У выбранного запоминающего элемента 2 первый вход подключен к одному из выходов 4 дешифратора 3 строк, имеющему при данном коде адреса сое- тояние логической I, либо второй вход подключен к одному из выходов 5 дешифратора 3 строк, имеющему при данном коде адреса состояние логиче

ского О. При этом на выходе запоминающего элемента 2 формируется соответственно значение функции, соответствующей выходу блока 8, подключенному к второму входу данного запоминающего элемента 2, либо инверсное значение функции, соответствующей

выходу блока 8, подключенному к первому входу запоминающего элемента 2.

Таким образом, если ,в матрице из М запоминающих элементов 2 необходимо на К з апоминающих элементах программировать значения функций f ,

fi f j 4. g -f 15 5

(M-K) элементах - инверсные значения этих функций, то в первом случае соответствующие выходы блока 8 f, 4 fa, f ,, , f , , f,- подключаются к вторым входам запоминающих элементов 2, а их первые входы - к соответствующим выходам 4 дешифратора строк, а во втором случае соответствующие выходы блока В f -f , fg, f, , f 13 f,,. подклю чаются к первым входам запоминающих, элементов 2, а их вторые входы - к соответствующим выходам 5 дешифратора строк.

Технико-экономические преимущества предлагаемого устройства заключаются в том, что сокращается в 2 раза количество шин программирования.

Формула изобретения

Постоянное запоминающее устройство, содержащее матрицу из М запоминающих элементов, дешифраторы строк и

31/4

столбцов, коммутатор столбцов и блок формирования логических функций двух переменных, причем объединенные по столбцам выходы запоминающих элементов соединены с информационньми входами коммутатора столбцов, адресные входы которого соединены с выходами дешифратора столбцов, выход коммутатора является информационным выходом устройства, входы дешифраторов строк, столбцов и блока формирования логических функций двух переменных являются входами первой, второй и третьей групп адресных входов устройства соответственно, отличающееся тем, что, с целью упро30304

щения устройства, запоминающие элементы матрицы выюлнены на МДП-тран- зисторах, причем затворы К из М запоминающих элементов матрицы соединены .с прямыми выходами дешифратора строк а стоки - с соответствующими выходами блока формирования логических функций двух переменных, затворы

10 (М-К) запоминающих элементов соединены с выходами блока формирования функций двух переменных, а стоками- с инверсньми выходами дeш iфpaтopa строк, истоки М запоминающих эле15 ментов объединены по столбцам и соединены с информационными входами коммутатора столбцов.

11

h

/

9ц.г.2

| Постоянное запоминающее устройство | 1980 |

|

SU881862A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1096694A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| I | |||

Авторы

Даты

1988-12-07—Публикация

1987-04-02—Подача