Изобретение относится к цифровой вычислительной технике и может быть использовано в системах тестового диагностирования цифровых устройств.

Целью изобретения является увеличение быстродействия и достоверности контроля анализатора.

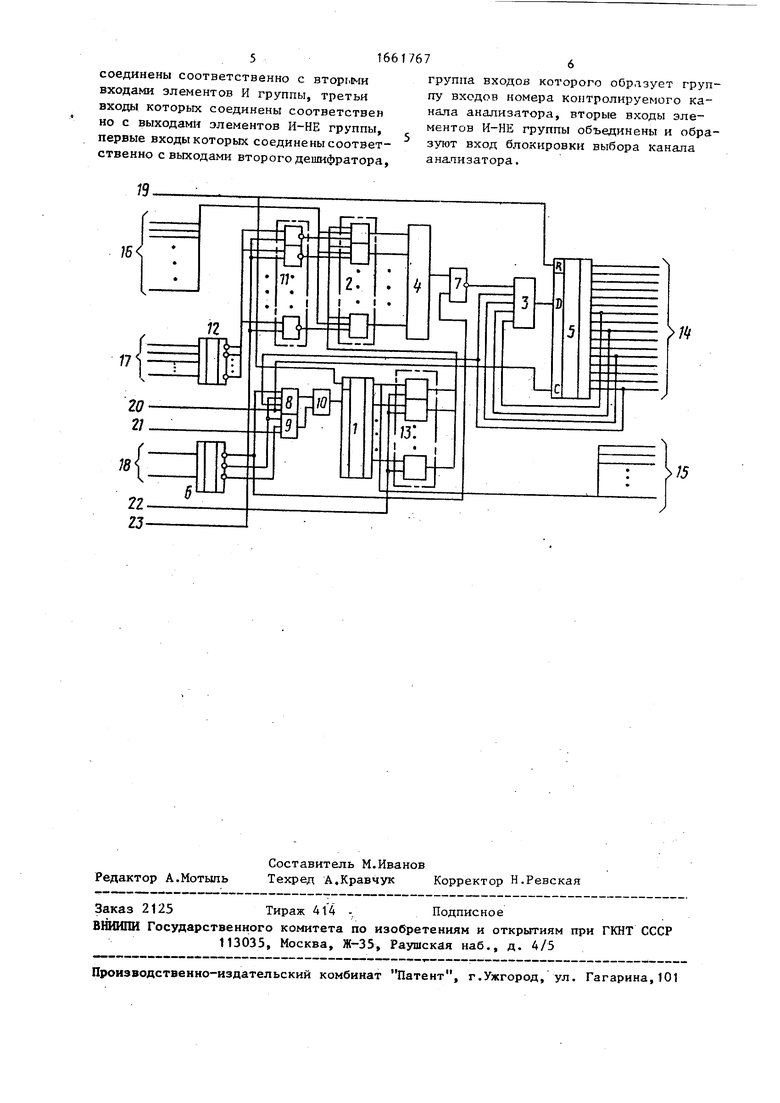

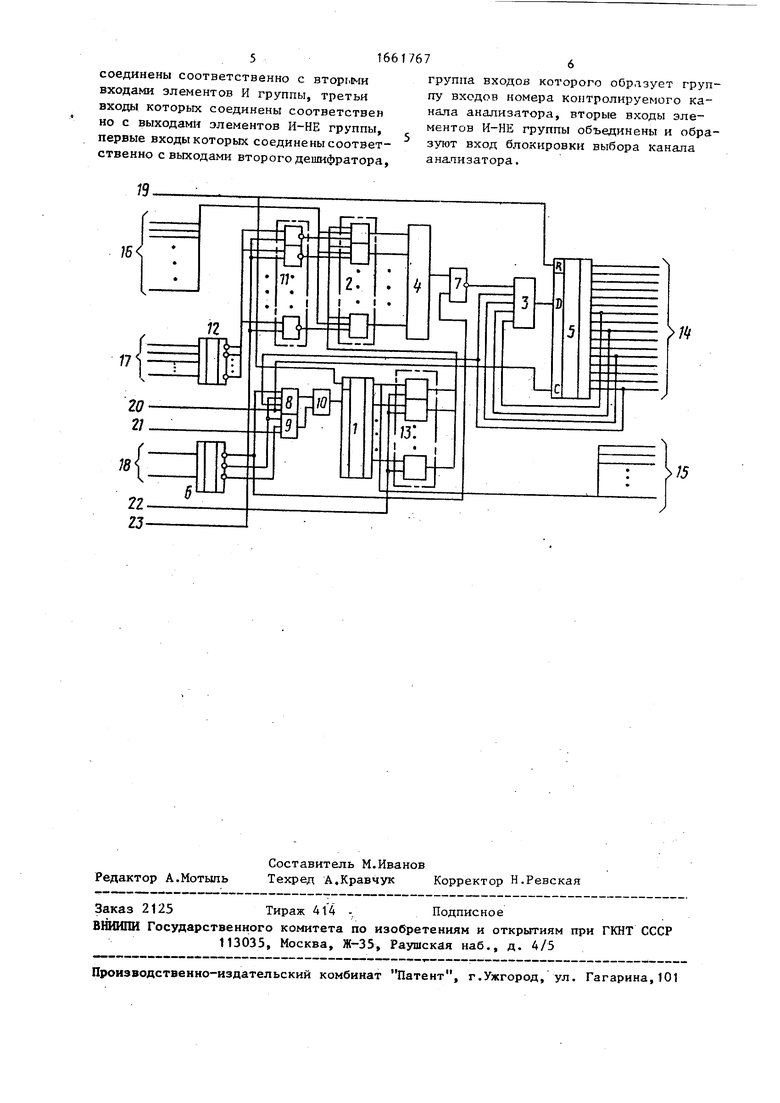

На чертеже представлена схема сигнатурного анализатора.

Сигнатурный анализатор содержит счетчик 1, группу 2 элементов И, первый 3 и второй 4 сумматоры по модулю два, сдвиговый регистр 5, дешифратор 6, элемент И-НЕ 7, первый 8 я второй 9 элементы И, элемент ИЛИ 10, группу 11 элементов И-НЕ, дешифратор 12, группы 13 элементов ИЛИ, первую группу информационных выходов 14, вторую группу информационных выходов 15, группу информационных входов 16, группу входов 17 номера контролируемого канала, группу входов ,

18 задания режима, вход 19 сброса, ,вход 20 синхронизации, установленный вход 21, вход 22 разрешения непрерывного контроля и вход 23 блокировки выбора канала 23.

Сигнатурный анализатор работает следующим образом.

Вход 20 синхронизации подключается к цепи синхронизации, а информационные входы 16 подключены к контрольным точкам исследуемого объекта. Группы выходов 14 и 15 подключены к цепям обработки результатов контроля или выводятся на индикацию. Входы 17 - 19, 21 - 23 подключаются к цепям управления сигнатурным анализатором. Перед началом работы по входу 19 сброс осуществляется установка в нуль счетчика 1 и регистра 5 сдвига. Затем в режиме установки исходного состояния сигнатурного анализатора (при состоянии входов 18 выбора режима

&

О

а

сигнатурного анализатора) ос, шесгвля- етсяустановка одного из 2 исходных состояний счетчика 1 и одного из -1 исходных состояний регистра 5 сдвига путем подачи соответствуюшего числа импульсов на входы 20 и Л, где п - число разрядов счетчика 1. Далее сигнатурный анализатор приводится в один из возможных режимов работы.

В первом режиме работы состояние входов 18 выбора режима сигнатурного анализатора - 1, О, входа 22 разрешения непрерывного контроля - О, входа 23 блокировки номера канала - О и контроль информации в каналах осуществляется непрерывно по установленной в счетчик комбинации каналов без изменения его состояния, т.е. без изменения комбинации контролируемых каналов.

Во втором режиме работы состояние входов 18 выбора режима сигнатурного анализатора - О, 1, входа 22 разрешения непрерывного контроля - О, входа 23 блокировки номера канала О и контроль информации в каналах осуществляется прерывисто, с изменением текущего состояния счетчика 1 в зависимости от состояния шестнадцатого разряда регистра сдвига 5, т.е. с изменением комбинации контролируемых каналов.

В указанных режимах работы при установке 1 на входе 22 разрешения непрерывного контроля контроль информа- ции происходит непрерывно во всех каналах одновременно.

При установке 1 на входе 23 блокировки номера канала во втором режиме работы (входы 18 - О, 1) контроль осуществляется только по одному из каналов, номер которого подается на входы номера контролируемого канала 17 сигнатурного анализатора.

Таким образом, предлагаемый анализатор осуществляет дополнительные режимы работы: непрерывный и прерывистый контроль информации только по одному выбранному каналу, а также непрерывный контроль информации по всем каналам одновременно, что обеспечивает уменьшение времени контроля за счет упрощения процедуры изменения режимов и увеличение достоверности контроля анализатора.-

Формула изобретения Сигнатурный анализатор, содержащий счетчик, группу элементов И,

o

0

,

5

5

55

0

40

45

50

первый и второй сумматоры по модулю два, первый дешифратор, два элемен та И, элемент ИЛИ, элемент И-НЕ, регистр сдвига, группа разрядных выходов которого образует первую группу информационных выходов анализатора, выходы разрядов регистра сдвига, номера которых соответствуют ненулевым коэффициентам образующего многочлена, соединены с входами первого сумматора по модулю два, выход которого соединен с информационным входом регистра сдвига, вход сброса которого объединен с входом сброса счетчика и образует вход сброса анализатора, тактовый вход регистра сдвига объединен с первым входом первого элемента И и образует тактовый вход анализатора, группа входов первого дешифратора образует группу входов задания режима анализатора, первые входы элементов И группы образуют группу информационных входов анализатора, выходы элементов И группы соединены с входами второго сумматора по модулю два, выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с (К+1)-м (К - число ненулевых коэффициентов образующего многочлена) входом первого сумматора по модулю два, второй вход элемента И-НЕ соединен с первым выходом первого дешифратора и вторым входом первого элемента И, третий вход которого соединен с первым входом второго элемента И и вторым выходом первого дешифратора, третий выход которого соединен с вторым входом второго элемента И, третий вход которого образует уста новочный вход анализатора, выходы первого и второго элементов И соединены с входами элемента ИЛИ, выход которого соединен со счетньМ входом счетчика, четвертый вход первого элемента И соединен с выходом последнего разряда регистра сдвига, отличающийся .тем, что, с целью увеличения быстродействия и достоверности контроля, в анализатор введены второй дешифратор, группа элементов И-НЕ, группа элементов ИЛИ, разрядные выходы счетчика соединены с первыми входами элементов ИЛИ группы и образуют вторую группу информационных выходов анализатора, вторые входы элементов ИЛИ группы объединены и образуют вход разрешения непрерывного контроля анализатора, выходы элементов ИЛИ группы

соединены соответственно с вторыми входами элементов И группы, третьи входы которых соединены соответствен но с выходами элементов И-НЕ группы, первые входы которых соединены соответн, т1661767б

группа входов которого образует группу входов номера контролируемого канала анализатора, вторые входы элементов И-НЕ группы объединены и обра- зуют вход блокировки выбора канала

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1987 |

|

SU1499346A1 |

| Сигнатурный анализатор | 1981 |

|

SU1048475A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1191911A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Сигнатурный анализатор | 1984 |

|

SU1262501A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

Изобретение относится к вычислительной технике и может использоваться в системах тестового диагностирования цифровых устройств. Цель изобретения - повышение быстродействия и достоверности контроля анализатора. Сигнатурный анализатор содержит счетчик, группу элементов И, два сумматора по модулю два, сдвиговый регистр, два дешифратора, элемент И - НЕ, два элемента И, элемент ИЛИ, группу элементов И - НЕ, группу элементов ИЛИ. Цель изобретения достигается за счет обеспечения непрерывного контроля как по всем каналам одновременно, так и только по одному выбранному каналу. 1 ил.

ственно с выходами второго дешифратора,

анализатора.

| Сигнатурный анализатор | 1981 |

|

SU1048475A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сигнатурный анализатор | 1987 |

|

SU1499346A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , (54) СИГНАТУРНЫЙ АНАЛИЗАТОР | |||

Авторы

Даты

1991-07-07—Публикация

1989-07-17—Подача