Изобретение относится к автоматизированным системам контроля и измерения параметров сигналов и может быть использовано для контроля больших и сверхбольших интегральных схем, а также на их основе цифровых устройств.

Целью изобретения является расширение функциональных возможностей за счет оценки и измерения длительности фронта, спада и импульса, периода, амплитуды и уровней сигнала, а также за счет автоматического изменения уровней и программного изменения частоты воздействия на объект.

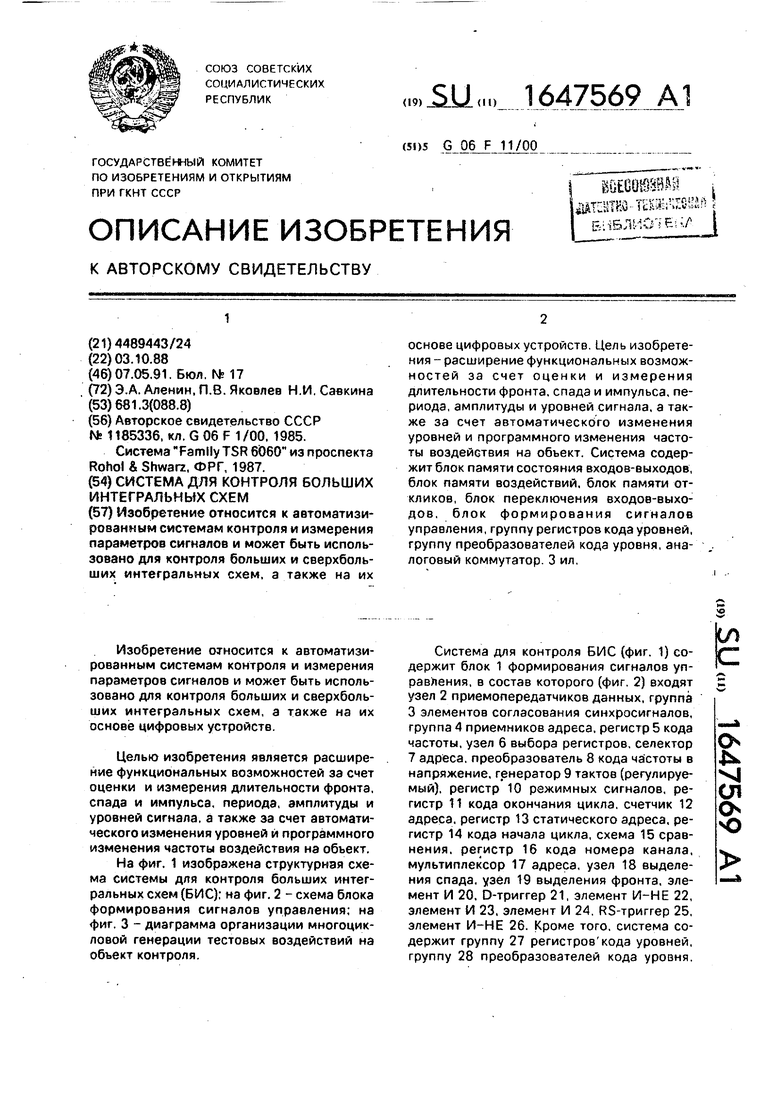

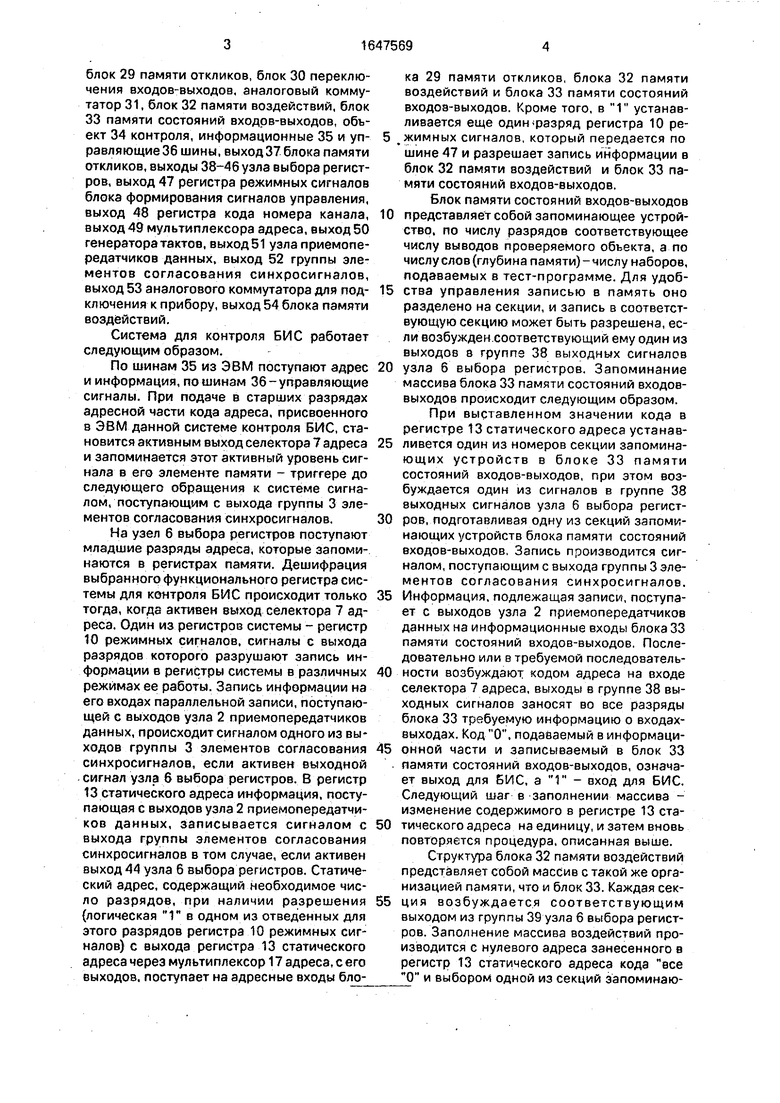

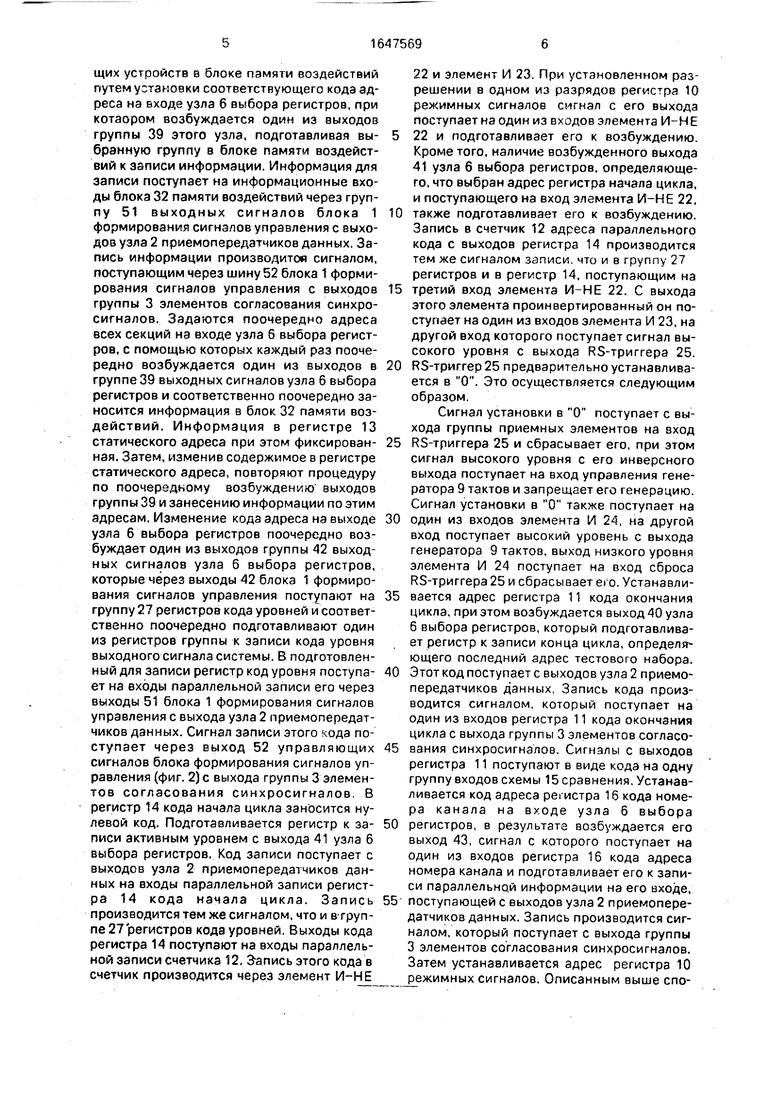

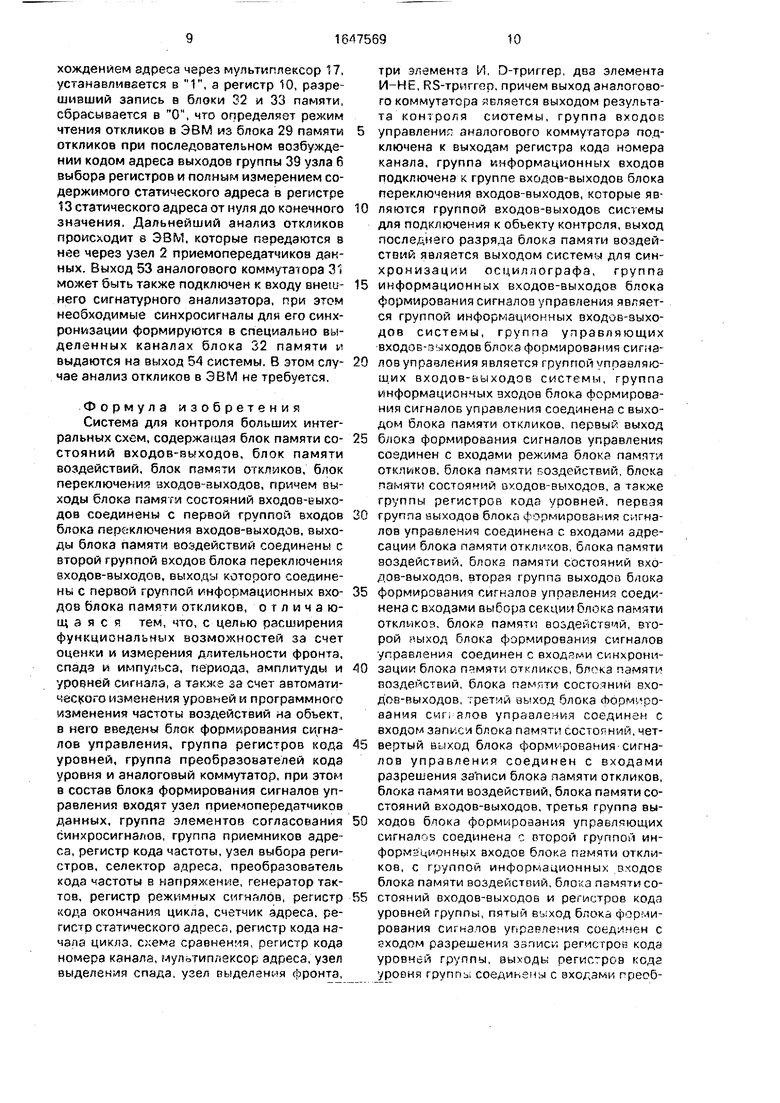

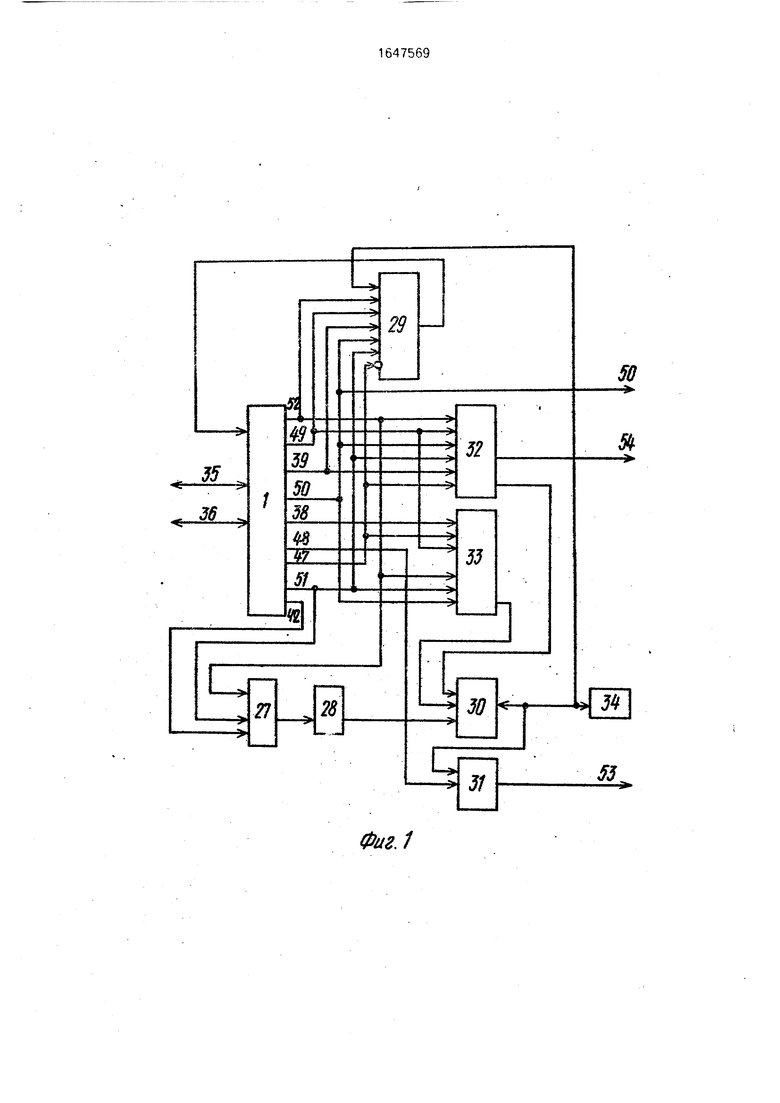

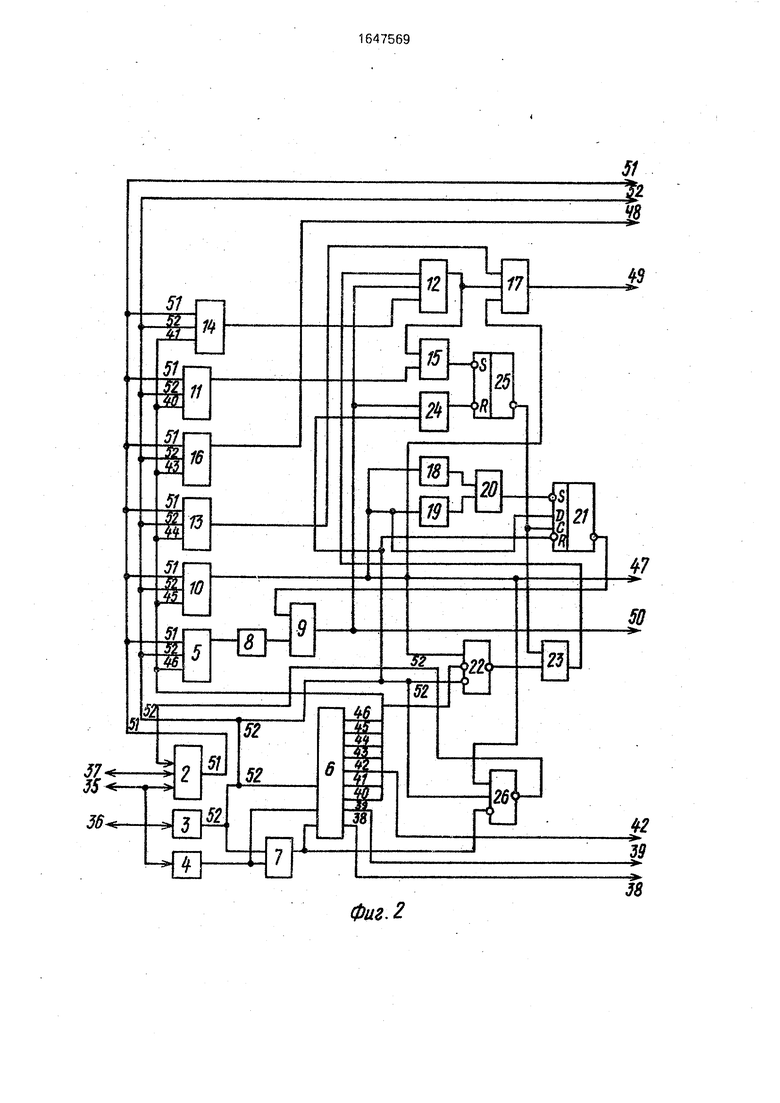

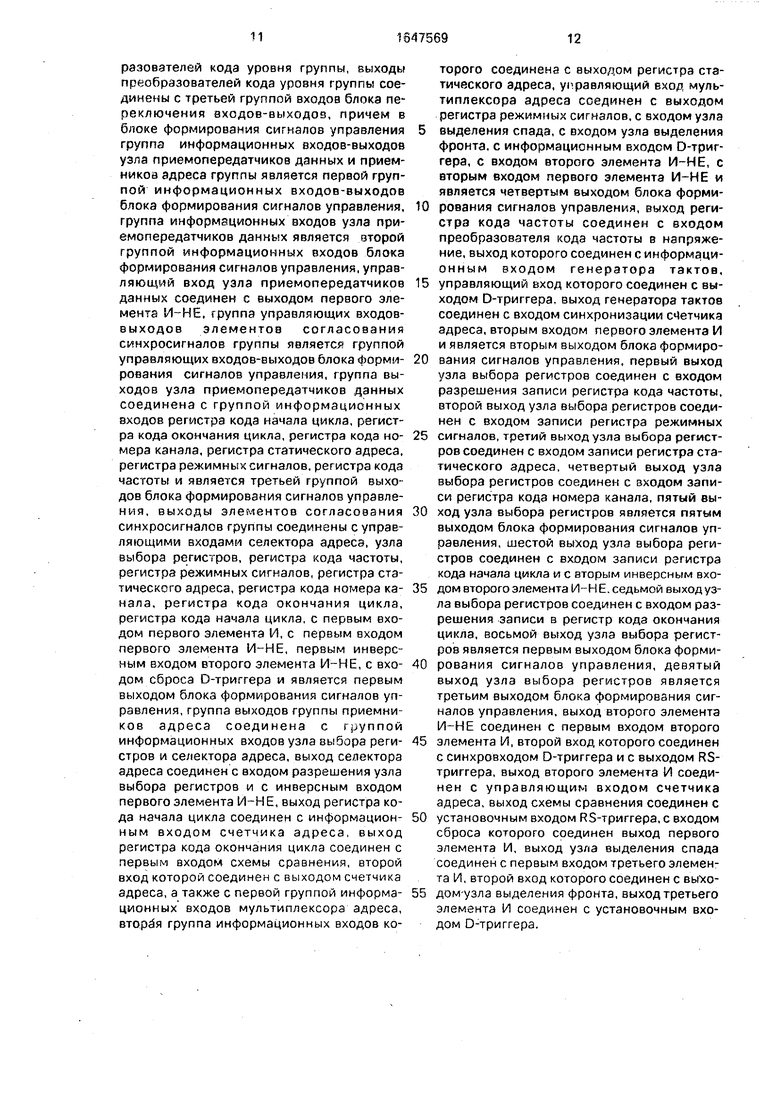

На фиг. 1 изображена структурная схема системы для контроля больших интегральных схем (БИС); на фиг. 2 - схема блока формирования сигналов управления; на фиг. 3 - диаграмма организации многоцик- ловой генерации тестовых воздействий на объект контроля.

Система для контроля БИС (фиг. 1) содержит блок 1 формирования сигналов управления, в состав которого (фиг. 2) входят узел 2 приемопередатчиков данных, группа 3 элементов согласования синхросигналов, группа 4 приемников адреса, регистр 5 кода частоты, узел 6 выбора регистров, селектор 7 адреса, преобразователь 8 кода частоты в напряжение, генератор 9 тактов (регулируемый), регистр 10 режимных сигналов, регистр 11 кода окончания цикла, счетчик 12 адреса, регистр 13 статического адреса, регистр 14 кода начала цикла, схема 15 сравнения, регистр 16 кода номера канала, мультиплексор 17 адреса, узел 18 выделения спада, узел 19 выделения фронта, элемент И 20, D-триггер 21, элемент И-НЕ 22, элемент И 23, элемент И 24. RS-триггер 25, элемент И-НЕ 26. Кроме того, система содержит группу 27 регистров кода уровней, группу 28 преобразователей кода уровня.

сл

с

о

4

а

а ч

блок 29 памяти откликов, блок 30 переключения входов-выходов, аналоговый коммутатор 31, блок 32 памяти воздействий, блок 33 памяти состояний входов-выходов, объект 34 контроля, информационные 35 и управляющие 36 шины, выход 37 блока памяти откликов, выходы 38-46 узла выбора регистров, выход 47 регистра режимных сигналов блока формирования сигналов управления, выход 48 регистра кода номера канала, выход 49 мультиплексора адреса, выход 50 генератора тактов, выход51 узла приемопередатчиков данных, выход 52 группы элементов согласования синхросигналов, выход 53 аналогового коммутатора для подключения к прибору, выход 54 блока памяти воздействий.

Система для контроля БИС работает следующим образом.

По шинам 35 из ЭВМ поступают адрес и информация, по шинам 36-управляющие сигналы. При подаче в старших разрядах адресной части кода адреса, присвоенного в ЭВМ данной системе контроля БИС, становится активным выход селектора 7 адреса и запоминается этот активный уровень сигнала в его элементе памяти - триггере до следующего обращения к системе сигналом, поступающим с выхода группы 3 элементов согласования синхросигналов.

На узел 6 выбора регистров поступают младшие разряды адреса, которые запоминаются в регистрах памяти. Дешифрация выбранного функционального регистра системы для контроля БИС происходит только тогда, когда активен выход селектора 7 адреса. Один из регистров системы - регистр 10 режимных сигналов, сигналы с выхода разрядов которого разрушают запись информации в регистры системы в различных режимах ее работы. Запись информации на его входах параллельной записи, поступающей с выходов узла 2 приемопередатчиков данных, происходит сигналом одного из выходов группы 3 элементов согласования синхросигналов, если активен выходной сигнал узла 6 выбора регистров. В регистр 13 статического адреса информация, поступающая с выходов узла 2 приемопередатчиков данных, записывается сигналом с выхода группы элементов согласования синхросигналов в том случае, если активен выход 44 узла 6 выбора регистров. Статический адрес, содержащий необходимое число разрядов, при наличии разрешения {логическая 1 в одном из отведенных для этого разрядов регистра 10 режимных сигналов) с выхода регистра 13 статического адреса через мультиплексор 17 адреса, с его выходов, поступает на адресные входы блока 29 памяти откликов, блока 32 памяти воздействий и блока 33 памяти состояний входов-выходов. Кроме того, в 1 устанавливается еще один-разряд регистра 10 ре жимных сигналов, который передается по шине 47 и разрешает запись информации в блок 32 памяти воздействий и блок 33 памяти состояний входов-выходов.

Блок памяти состояний входов-выходов

0 представляет собой запоминающее устройство, по числу разрядов соответствующее числу выводов проверяемого объекта, а по числу слов (глубина памяти) - числу наборов, подаваемых в тест-программе. Для удоб5 ства управления записью в память оно разделено на секции, и запись в соответствующую секцию может быть разрешена, если возбужден соответствующий ему один из выходов в группе 38 выходных сигналов

0 узла 6 выбора регистров. Запоминание массива блока 33 памяти состояний входов- выходов происходит следующим образом.

При выставленном значении кода в регистре 13 статического адреса устанав5 ливется один из номеров секции запоминающих устройств в блоке 33 памяти состояний входов-выходов, при этом возбуждается один из сигналов в группе 38 выходных сигналов узла 6 выбора регист0 ров, подготавливая одну из секций запоминающих устройств блока памяти состояний входов-выходов. Запись производится сигналом, поступающим с выхода группы 3 элементов согласования синхросигналов.

5 Информация, подлежащая записи, поступает с выходов узла 2 приемопередатчиков данных на информационные входы блока 33 памяти состояний входов-выходов. Последовательно или в требуемой последователь0 ности возбуждают кодом адреса на входе селектора 7 адреса, выходы в группе 38 выходных сигналов заносят во все разряды блока 33 требуемую информацию о входах- выходах. Код О, подаваемый в информаци5 онной части и записываемый в блок 33 памяти состояний входов-выходов, означает выход для БИС, а 1 - вход для БИС. Следующий шаг в заполнении массива - изменение содержимого в регистре 13 ста0 тического адреса на единицу, и затем вновь повторяется процедура, описанная выше.

Структура блока 32 памяти воздействий представляет собой массив с такой же организацией памяти, что и блок 33. Каждая сек5 ция возбуждается соответствующим выходом из группы 39 узла 6 выбора регистров. Заполнение массива воздействий производится с нулевого адреса занесенного в регистр 13 статического адреса кода все О и выбором одной из секций запоминающих устройств в блоке памяти воздействий путем установки соответствующего кода адреса на входе узла 6 выбора регистров, при котаором возбуждается один из выходов группы 39 этого узла, подготавливая вы- бранную группу в блоке памяти воздействий к записи информации. Информация для записи поступает на информационные входы блока 32 памяти воздействий через группу 51 выходных сигналов блока 1 формирования сигналов управления с выходов узла 2 приемопередатчиков данных. Запись информации производится сигналом, поступающим через шину 52 блока 1 формирования сигналов управления с выходов группы 3 элементов согласования синхросигналов. Задаются поочередно адреса всех секций на входе узла б выбора регистров, с помощью которых каждый раз поочередно возбуждается один из выходов в группе 39 выходных сигналов узла 6 выбора регистров и соответственно поочередно заносится информация в блок 32 памяти воздействий. Информация в регистре 13 статического адреса при этом фиксирован- ная. Затем, изменив содержимое в регистре статического адреса, повторяют процедуру по поочередному возбуждению выходов группы 39 и занесению информации по этим адресам. Изменение кода адреса на выходе узла 6 выбора регистров поочередно возбуждает один из выходов группы 42 выходных сигналов узла 6 выбора регистров, которые через выходы 42 блока 1 формирования сигналов управления поступают на группу 27 регистров кода уровней и соответственно поочередно подготавливают один из регистров группы к записи кода уровня выходного сигнала системы. В подготовленный для записи регистр код уровня поступа- ет на входы параллельной записи его через выходы 51 блока 1 формирования сигналов управления с выхода узла 2 приемопередатчиков данных. Сигнал записи этого кода поступает через выход 52 управляющих сигналов блока формирования сигналов управления (фиг. 2) с выхода группы 3 элементов согласования синхросигналов. В регистр 14 кода начала цикла заносится нулевой код. Подготавливается регистр к за- писи активным уровнем с выхода 41 узла 6 выбора регистров. Код записи поступает с выходов узла 2 приемопередатчиков данных на входы параллельной записи регистра 14 кода начала цикла. Запись производится тем же сигналом, что и втруп- пе 27 регистров кода уровней. Выходы кода регистра 14 поступают на входы параллельной записи счетчика 12. Запись этого кода в счетчик производится через элемент И-НЕ

22 и элемент И 23. При установленном разрешении в одном из разрядов регистра 10 режимных сигналов сигнал с его выхода поступает на один из входов элемента И-НЕ 22 и подготавливает его к возбуждению. Кроме того, наличие возбужденного выхода 41 узла б выбора регистров, определяющего, что выбран адрес регистра начала цикла, и поступающего на вход элемента И-НЕ 22, также подготавливает его к возбуждению. Запись в счетчик 12 адреса параллельного кода с выходов регистра 14 производится тем же сигналом записи, что и в группу 27 регистров и в регистр 14, поступающим на третий вход элемента И-НЕ 22. С выхода этого элемента проинвертированный он поступает на один из входов элемента И 23, на другой вход которого поступает сигнал высокого уровня с выхода RS-триггера 25. RS-триггер 25 предварительно устанавливается в О. Это осуществляется следующим образом.

Сигнал установки в О поступает с выхода группы приемных элементов на вход RS-триггера 25 и сбрасывает его, при этом сигнал высокого уровня с его инверсного выхода поступает на вход управления генератора 9 тактов и запрещает его генерацию. Сигнал установки в О также поступает на один из входов элемента И 24, на другой вход поступает высокий уровень с выхода генератора 9 тактов, выход низкого уровня элемента И 24 поступает на вход сброса RS-триггера 25 и сбрасывает его. Устанавливается адрес регистра 11 кода окончания цикла, при этом возбуждается выход 40 узла 6 выбора регистров, который подготавливает регистр к записи конца цикла, определяющего последний адрес тестового набора. Этот код поступает с выходов узла 2 приемопередатчиков данных. Запись кода производится сигналом, который поступает на один из входов регистра 11 кода окончания цикла с выхода группы 3 элементов согласования синхросигналов. Сигналы с выходов регистра 11 поступают в виде кода на одну группу входов схемы 15 сравнения. Устанавливается код адреса регистра 16 кода номера канала на входе узла 6 выбора регистров, в результате возбуждается его выход 43, сигнал с которого поступает на один из входов регистра 16 кода адреса номера канала и подготавливает его к записи параллельной информации на его входе, поступающей с выходов узла 2 приемопередатчиков данных. Запись производится сигналом, который поступает с выхода группы 3 элементов согласования синхросигналов. Затем устанавливается адрес регистра 10 режимных сигналов. Описанным выше способом в него записывается О, в упомянутый выше разряд, который управляет прохождением адреса на блоки 29, 32, 33 памяти через мультиплексор 17 и подтверждается 1 в разряде регистра 10, который разрешает запись информации в блоки 32 и 33 памяти. Дополнительно в 1 устанавливается разряд регистра 10, который поступает через узел 19 выделения фронта «А далее через элемент И 20 на вход О-тригге- ра 21 и сбрасывает его в ноль. При этом сигнал с инверсного выхода D-тршгера 21} разрешает работу генератора 9 тактов. 3 остальные разряды регистра 0 записываются нули. Временная диаграмма для этого случая представлена на фиг. 3. Выход генератора 9 подается на счетчик 12 адреса. Установленное нулевое значение упомянутого разряда регистра 10 режимных сигналов поступает на вход мультиплексора 17 адреса и разрешает прохождение теперь через него выходов счетчика 12 адреса на выходы 49 блока 1 и далее на адресные входы блока 29 памяти откликов, блока 32 памяти воздействий и блока 33 памяти состояний входов-выходов. При этом в каждом из блоков памяти разрешены к обращению все разряды, причем блок 32 памяти воздействий и блок 33 памяти состояний входов- йыходов становятся в режим чтения, а бяок 29 памяти откликов - в режим записи.. Темп передачи воздействия и значений функций входов-выходов на контролируемую БИС и запись откликов в блок памяти откш/.- ков соответствуют частоте генератора 9 тактов. Если БVIС не имеет входов-выходов и нет необходимости производить перекоммутацию входов-выходов в темпе проверки, то необходимо в начале работы установить в О соответствующий разряд регистра 10 режимных сигналов, а если требуется перекоммутация, то этот разряд регистра режимных сигналов устанавливается в 1. Связь по этому разряду управления между регистром 10 (фиг. 2) и блоком 33 (фиг. 1) осуществляется по шине 47. В случае, если упомянутый разряд регистра 10 режимных сигналов, управляющий генератором 9, установлен в 1, генерация теста и запись откликов производятся по бесконечному кольцу и соответственно на выходе аналогового коммутатора 31 с установленного в регистре 16 кода номера канала на выход 53 системы поступает временная диаграмма с выбранного канала.

Программным путем внешним осциллографом (например, С7-17) производится обмер всех параметров сигналов: длительность импульса, длительность фронта, длительное гь спада, период, амплитуда,

уровень логического О, выброс на переднем фронте, выброс на спаде. Для выходных воздействий измеряется уровень О, уровень 1 и в случае необходимости изменения этих уровней меняются значения кода в соответствующих регистрах блока регистров уровней, номер которых выбирается кодом адреса на входе узла б выбора регистров. Изменение кода может произво0 диться в процессе генерации динамического теста в системе либо в статическом режиме. Требуемая частота генерации устанавливав гея путем изменения содержимого регистра 5 кода частоты при установке соот5 ветствующего кода адреса, при котором возбуждается выход 46 узпа б выбора регистров. К выходу 54 системы подключается осциллограф и измеренное значение частоты вводится в ЭВМ из осциллографа как

0 параметр, при совпадении параметров, измеренных осциллографом и заданных в тест-программе, изменение кеда прекращается. Вход осциллографа после этого подключается к основному выходу 53 системы 5 к выходу аналогового коммутатора 31. В процессе работы частота также может изме- нягьсй, при этом изменения частоты генератора оцениваются косвенно по частотным параметрам тестовых воздействий и от0 кликов. Изменение частоты производится, в частности, для оценки предельных возможностей контролируемой БИС по частоте. Последний разряд блока 32 памяти отведен для записи синхросигнала под кон5 кретно заданный тест для БИС. Синхросигнал может подключаться к входу синхронизации олсциллографа для получения устойчивых результатов и определения всех временных параметров с привязкой к

0 единому синхросигналу для всех контролируемых каналов.

После обмера параметров на одном канале программным путем осуществляется переход к следующему коду адреса, кото5 рый определяет новую контрольную точку (канал). И на этом канале вновь производится измерение характеристик сигнала. Для прекращения генерации динамического теста упомянутый разряд регистра 10 режим0 ных сигналов, управляющий работой генератора 9, устанавливается в О, тем самым пооизводится остановка работы тактового генератора и, собственно, генерация теста. Повторный запуск теста происходит

5 только после того, как закончится очередной его полный цикл, т.е. когда будут равны два кода: код в счетчике 12 адреса и код, записанный в регистр 11 кода окончания цикла. После этого разряд регистра 10 режимных сигналов, который управляет прохождением адреса через мультиплексор 17, устанавливается в 1, а регистр 10, разрешивший запись в блоки 32 и 33 памяти, сбрасывается в О, что определяет режим чтения откликов в ЭВМ из блока 29 памяти откликов при последовательном возбуждении кодом адреса выходов группы 39 узла 6 выбора регистров и полным измерением содержимого статического адреса в регистре 13 статического адреса от нуля до конечного значения. Дальнейший анализ откликов происходит в ЭВМ, которые передаются в нее через узел 2 приемопередатчиков данных. Выход 53 аналогового коммутатора 3 t может быть также подключен к входу внешнего сигнатурного анализатора, при этом необходимые синхросигналы для его синхронизации формируются в специально выделенных каналах блока 32 памяти и выдаются на выход 54 системы. В этом случае анализ откликов в ЭВМ не требуется.

Формула изобретения Система для контроля больших интегральных схем, содержащая блок памяти состояний входов-выходов, блок памяти воздействий, блок памяти откликов, блок переключения входов-выходов, причем выходы блока памяти состояний входов-выходов соединены с первой группой входов блока переключения входов-выходов, выходы блока памяти воздействий соединены с второй группой входов блока переключений входов-выходов, выходы которого соединены с первой группой информационных входов блока памяти откликов, отличающаяся тем, что, с целью расширения функциональных возможностей за счет оценки и измерения длительности фронта, спада и импульса, периода, амплитуды и уровней сигнала, а также за счет автоматического изменения уровней и программного изменения частоты воздействий на объект, в него введены блок формирования сигналов управления, группа регистров кода уровней, группа преобразователей кода уровня и аналоговый коммутатор, при этой в состав блока формирования сигналов управления входят узел приемопередатчиков данных, группа элементов согласования синхросигналов, группа приемников адреса, регистр кода частоты, узел выбора регистров, селектор адреса, преобразователь кода частоты в напряжение, генератор тактов, регистр режимных сигналов, регистр кода окончания цикла, счетчик адреса, регистр статического адреса, регистр кода начала цикла, схема сравнения, регистр кода номера канала, мупотиплексор адреса, узел выделения спада, узел выделения фронта,

три элемента И. D-триггер, два элемента И-НЕ, RS-трпггор, причем выход аналогового коммутатора является выходом результата контроля системы, группа входов

управлени аналогового коммутатора подключена к выходам регистра кода номера канала, группа информационных входов подключена к группе входов-выходов блока переключения входов-выходов, которые яв0 ляются группой входов-выходов системы для подключения к объекту контроля, выход последнего разряда блока памяти воздействий является выходом системы для синхронизации осциллографа, группа

5 информационных входов-выходов блока формирования сигналов управления является группой информационных входов-выходов системы, группа управляющих ВХОДОЕ-ЗЧХОДОВ блока формирования сигна0 лов управления является группой управляющих входов-выходов системы, группа информационных входов блока формирования сигналов управления соединена с выходом блока памяти откликов, первый выход

5 блока формирования сигналов управления соединен с входами режима блока пампт-и откликов, блока памяти поздействий, блока памяти состояний входов-выходов, а также группы регистров кода уровней, первая

0 группа выходов блока формирования сигналов управления соединена с. входами адресации блока памяти откликов, блока памяти воздействий, блока памяти состояний входов-выходов, вторая группа выходов блока

5 формирования сигналов управления соединена с входами выбора секции блока памяти откликов, блока памяти воздействий, второй ыход блока формирования сигналов управления соединен с входами синхрони0 зации блока откликов, памяти воздействий, блока памяти состоянии входов-выходов, третий выход блока Формирования сиг, апов управления соединен с входом записи блока памяти состояний, чет5 вертый выход блока формирования сигналов управления соединен с входами разрешения за писи блока памяти откликов, блока памяти воздействий, блока памяти состояний входов-выходов, третья группа вы0 ходов блока формирования управляющих сигналов соединена с оторой группой информационных входов блока памяти откликов, с группой информационных входое блока памяти воздействий, блока памяти со5 стояний оходов-выходов и регистров кода уровней группы, пятый вь:ход блока формирования сигиз-юв управления соединен с еходом разрешения записи регистров кода уровней группы, выходы регистров кода уровня группь. соединены с входами преобразовзтелей кода уровня группы, выходы преобразователей кода уровня группы соединены с третьей группой входов блока переключения входов-выходов, причем в блоке формирования сигналов управления группа информационных входов-выходов узла приемопередатчиков данных и приемников адреса группы является первой группой информационных входов-выходов блока формирования сигналов управления, группа информационных входов узла приемопередатчиков данных является второй группой информационных входов блока формирования сигналов управления, управляющий вход узла приемопередатчиков данных соединен с выходом первого элемента И-НЕ, группа управляющих входов- выходов элементов согласования синхросигналов группы является группой управляющих входов-выходов блока Формирования сигналов управления, группа выходов узла приемопередатчиков данных соединена с группой информационных входов регистра кода начала цикла, регистра кода окончания цикла, регистра кода номера канала, регистра статического адреса, регистра режимных сигналов, регистра кода частоты и является третьей группой выходов блока формирования сигналов управления, выходы элементов согласования синхросигналов группы соединены с управляющими входами селектора адреса, узла выбора регистров, регистра кода частоты, регистра режимных сигналов, регистра статического адреса, регистра кода номера канала, регистра кода окончания цикла, регистра кода начала цикла, с первым входом первого элемента И, с первым входом первого элемента И-НЕ, первым инверсным входом второго элемента И-НЕ, с входом сброса D-триггера и является первым выходом блока формирования сигналов управления, группа выходов группы приемников адреса соединена с группой информационных входов узла выбора регистров и селектора адреса, выход селектора адреса соединен с входом разрешения узла выбора регистров и с инверсным входом первого элемента И-НЕ, выход регистра кода начала цикла соединен с информационным входом счетчика адреса, выход регистра кода окончания цикла соединен с первым входом схемы сравнения, второй вход которой соединен с выходом счетчика адреса, а также с первой группой информационных входов мультиплексора адреса, вторая группа информационных входов которого соединена с выходом регистра статического адреса, управляющий еход мультиплексора адреса соединен с выходом регистра режимных сигналов, с входом узла

выделения спада, с входом узла выделения фронта, с информационным входом D-триггера, с входом второго элемента И-НЕ, с вторым входом первого элемента И-НЕ и является четвертым выходом блока формирования сигналов управления, выход регистра кода частоты соединен с входом преобразователя кода частоты в напряжение, выход которого соединен с информаци- онным входом генератора тактов,

управляющий вход которого соединен с выходом D-триггера, выход генератора тактов соединен с входом синхронизации счетчика адреса, вторым входом первого элемента И и является вторым выходом блока формирования сигналов управления, первый выход узла выбора регистров соединен с входом разрешения записи регистра кода частоты, второй выход узла выбора регистров соединен с входом записи регистра режимных

сигналов, третий выход узла выбора регистров соединен с входом записи регистра статического адреса, четвертый выход узла выбора регистров соединен с входом записи регистра кода номера канала, пятый выход узла выбора регистров является пятым выходом блока формирования сигналов управления, шестой выход узла выбора регистров соединен с входом записи регистра кода начала цикла и с вторым инверсным входом второго элемента И-НЕ. седьмой выход узла выбора регистров соединен с входом разрешения записи в регистр кода окончания цикла, восьмой выход узла выбора регистров является первым выходом блока формирования сигналов управления, девятый выход узла выбора регистров является третьим выходом блока формирования сигналов управления, выход второго элемента И-НЕ соединен с первым входом второго

элемента И, второй вход которого соединен с синхровходом D-триггера и с выходом RS- триггера, выход второго элемента И соединен с управляющим входом счетчика адреса, выход схемы сравнения соединен с

установочным входом RS-триггера, с входом сброса которого соединен выход первого элемента И, выход узла выделения спада соединен с первым входом третьего элемента И, второй вход которого соединен с выходом узла выделения фронта, выход третьего элемента И соединен с установочным входом D-триггера.

Фиг.1

Фиг. 2

38

Сброс

Выход регистра 10$

Выход узя и 18

регистра Ш

Выход узла 13

Выход элемента 23

Выход триггера 21

Выход генератора 9

Выход „ схемы 15

Вшод ЛС триггера 25

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

| Устройство для диагностики неисправностей цифровых узлов | 1987 |

|

SU1481773A1 |

| Устройство для сопряжения вычислительного комплекса накопителей на магнитной ленте | 1983 |

|

SU1142839A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

Изобретение относится к автоматизированным системам контроля и измерения параметров сигналов и может быть использовано для контроля больших и сверхбольших интегральных схем, а также на их основе цифровых устройств. Цель изобретения - расширение функциональных возмож- ностей за счет оценки и измерения длительности фронта, спада и импульса, периода, амплитуды и уровней сигнала, а также за счет автоматического изменения уровней и программного изменения частоты воздействия на объект. Система содержит блок памяти состояния входов-выходов, блок памяти воздействий, блок памяти откликов, блок переключения входов-выходов, блок формирования сигналов управления, группу регистров кода уровней, группу преобразователей кода уровня, аналоговый коммутатор. 3 ил,

Фие.З

| Авторское свидетельство СССР № 1185336, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Система Family TSR 6060 из проспекта Rohol & Shwarz, ФРГ, 1987 | |||

Авторы

Даты

1991-05-07—Публикация

1988-10-03—Подача