Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки информации.

Цель изобретения - расширение функ- циональнах возможностей путем адаптивного перераспределения загрузки процессоров.

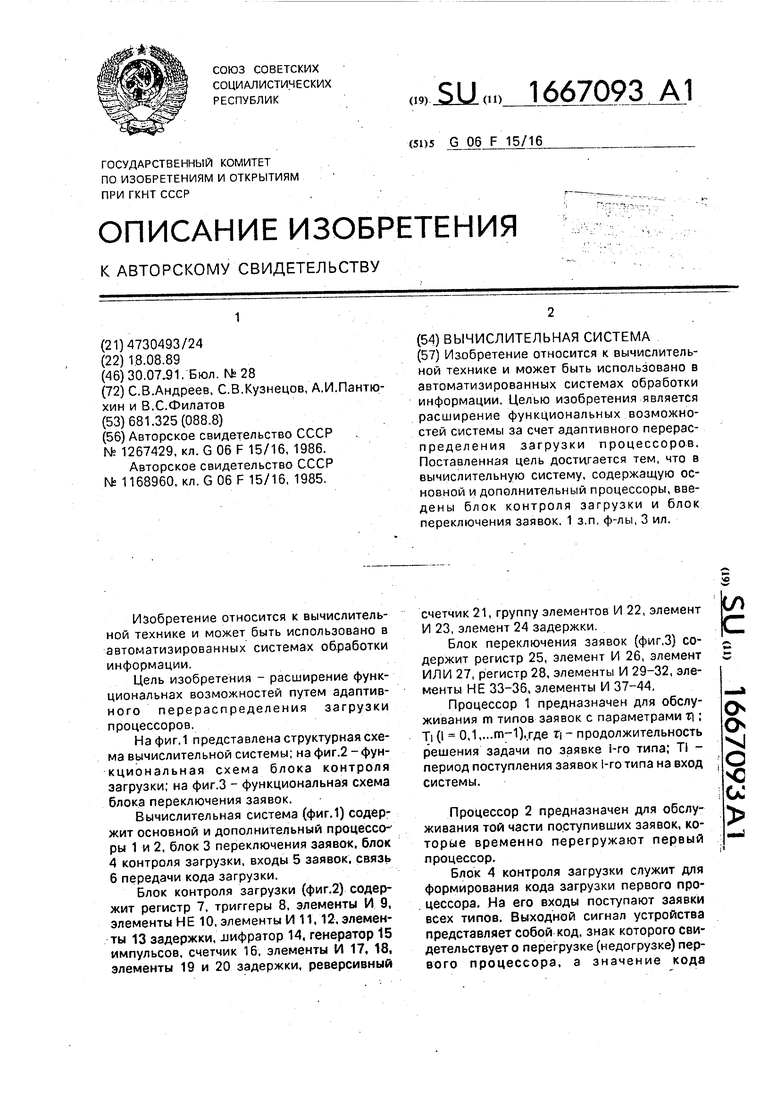

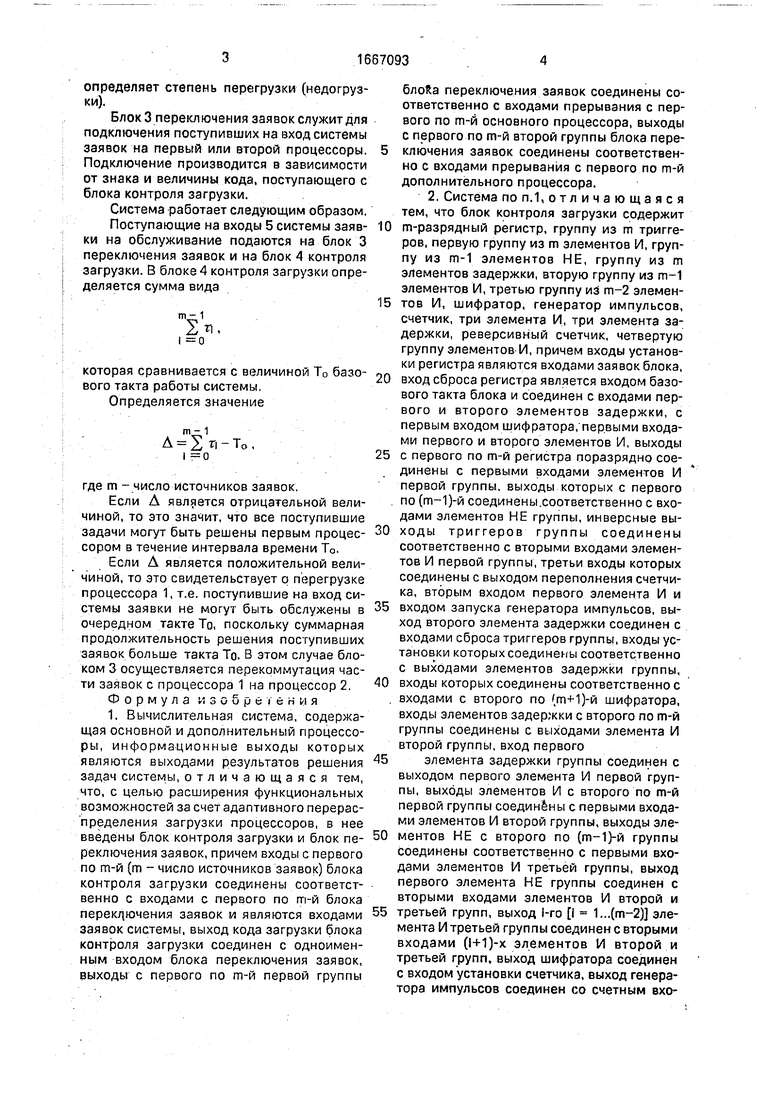

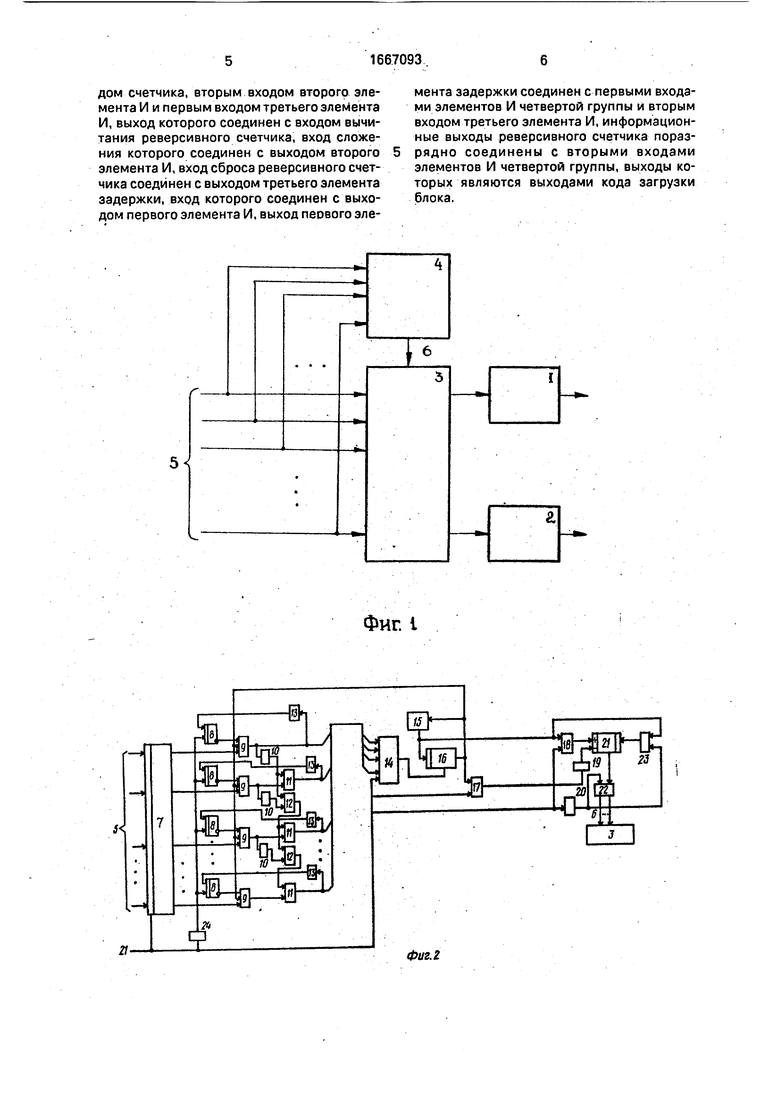

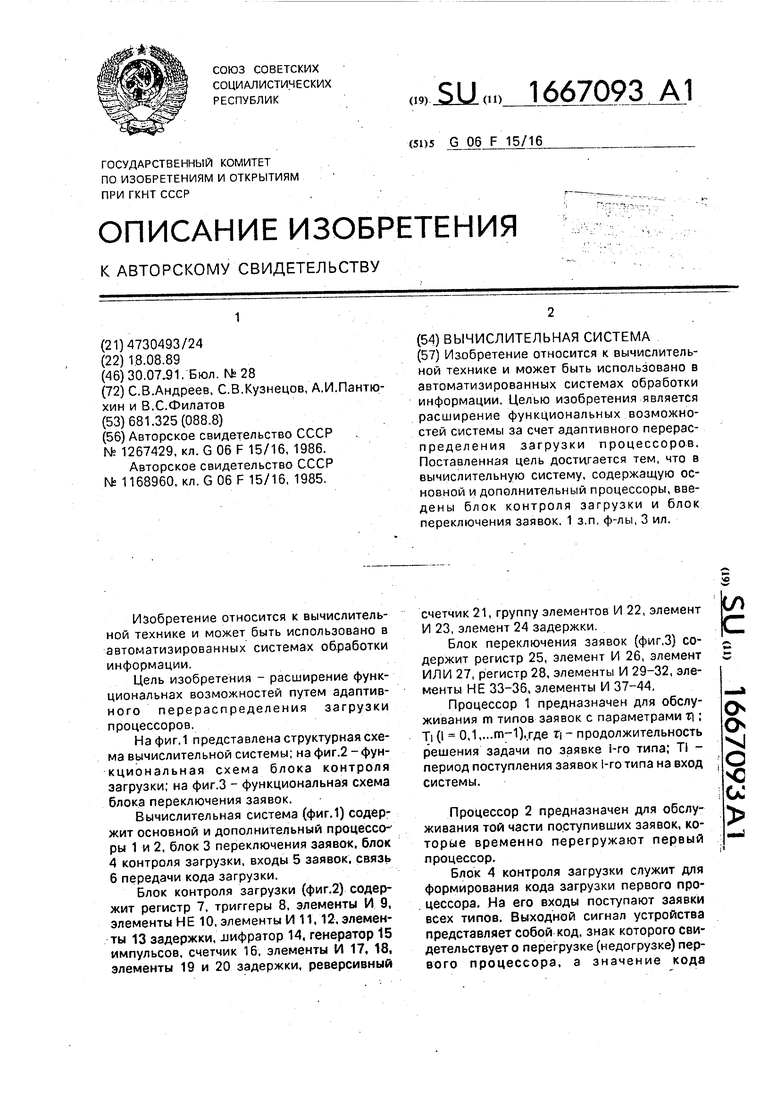

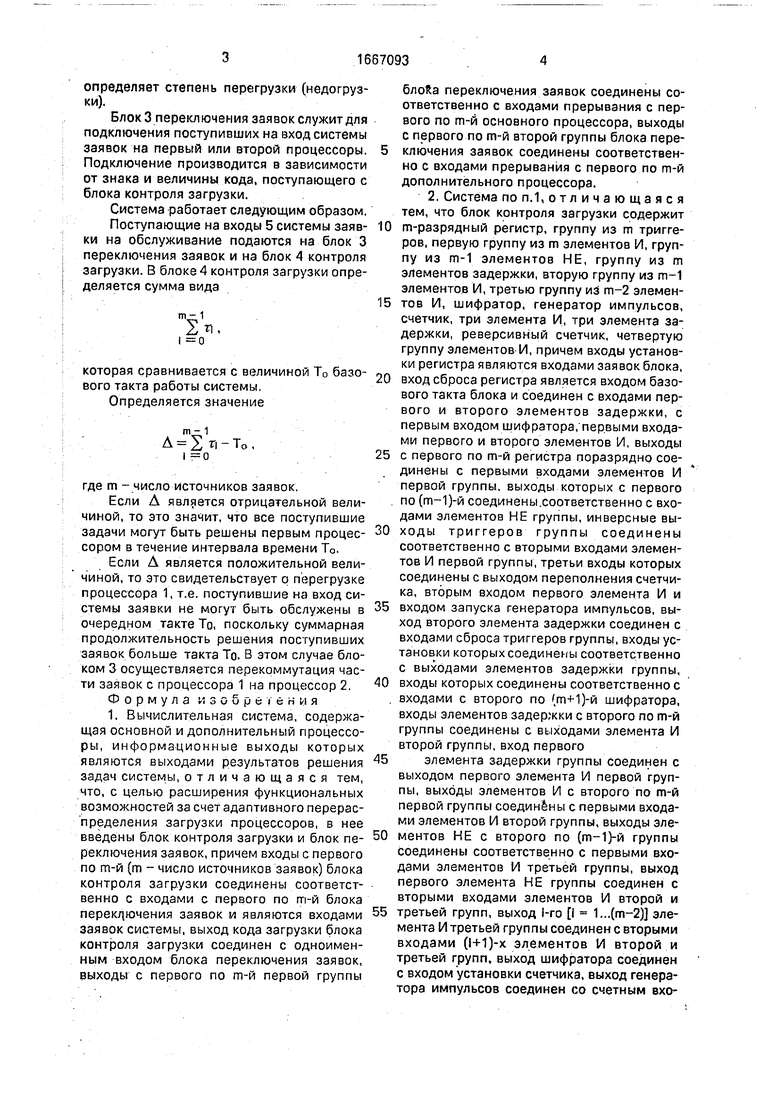

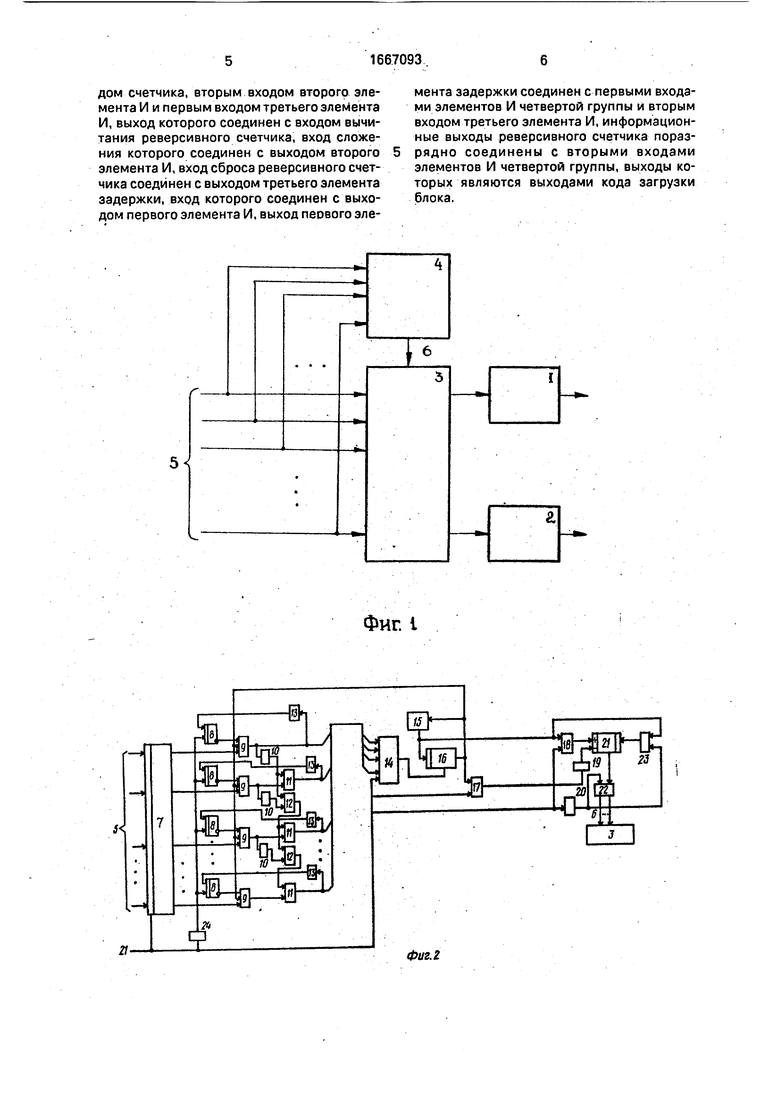

На фиг.1 представлена структурная схема вычислительной системы; на фиг.2 - фун- кциональная схема блока контроля загрузки; на фиг.З - функциональная схема блока переключения заявок.

Вычислительная система (фиг.1) содержит основной и дополнительный процессоры 1 и 2, блок 3 переключения заявок, блок 4 контроля загрузки, входы 5 заявок, связь 6 передачи кода загрузки.

Блок контроля загрузки (фиг.2) содержит регистр 7, триггеры 8, элементы И 9, элементы НЕ 10, элементы И 11.12. элементы 13 задержки, шифратор 14, генератор 15 импульсов, счетчик 16, элементы И 17, 18, элементы 19 и 20 задержки, реверсивный

счетчик 21, группу элементов И 22, элемент И 23, элемент 24 задержки

Блок переключения заявок (фиг.З) содержит регистр 25, элемент И 26, элемент ИЛИ 27, регистр 28, элементы И 29-32, элементы НЕ 33-36, элементы И 37-44.

Процессор 1 предназначен для обслуживания m типов заявок с параметрами TJ (I 0,1,...т-1),где т - продолжительность решения задачи по заявке 1-го типа; TI - период поступления заявок 1-го типа на вход системы.

Процессор 2 предназначен для обслуживания той части поступивших заявок, которые временно перегружают первый процессор.

Блок 4 контроля загрузки служит для формирования кода загрузки первого процессора. На его входы поступают заявки всех типов. Выходной сигнал устройства представляет собой код, знак которого свидетельствует о перегрузке(недогрузке) первого процессора, а значение кода

сл

с

с о

VI о ч: с:

определяет степень перегрузки (недогрузки).

БлокЗ переключения заявок служит для подключения поступивших на вход системы заявок на первый или второй процессоры. Подключение производится в зависимости от знака и величины кода, поступающего с блока контроля загрузки.

Система работает следующим образом.

Поступающие на входы 5 системы заявки на обслуживание подаются на блок 3 переключения заявок и на блок 4 контроля загрузки. В блоке 4 контроля загрузки определяется сумма вида

т-1

2, я

I 0

которая сравнивается с величиной Т0 базового такта работы системы. Определяется значение

т- 1

А 2 Ъ То ,

i -О

где т - число источников заявок.

Если Д является отрицательной величиной, то это значит, что все поступившие задачи могут быть решены первым процессором в течение интервала времени Т0.

Если Д является положительной величиной, то это свидетельствует о перегрузке процессора 1, т.е. поступившие на вход системы заявки не могут быть обслужены в очередном такте То, поскольку суммарная продолжительность решения поступивших заявок больше такта То. В этом случае блоком 3 осуществляется перекоммутация части заявок с процессора 1 на процессор 2.

Формула изобрц1сния

1. Вычислительная система, содержащая основной и дополнительный процессоры, информационные выходы которых являются выходами результатов решения задач системы, отличающаяся тем, что, с целью расширения функциональных возможностей за счет адаптивного перераспределения загрузки процессоров, в нее введены блок контроля загрузки и блок переключения заявок, причем входы с первого по m-й (т - число источников заявок) блока контроля загрузки соединены соответственно с входами с первого по m-й блока переключения заявок и являются входами заявок системы, выход кода загрузки блока контроля загрузки соединен с одноименным входом блока переключения заявок, выходы с первого по m-й первой группы

блоКа переключения заявок соединены соответственно с входами прерывания с первого по m-й основного процессора, выходы с первого по m-й второй группы блока переключения заявок соединены соответственно с входами прерывания с первого по m-й дополнительного процессора.

2. Система поп.1,отличающаяся тем, что блок контроля загрузки содержит

0 m-разрядный регистр, группу из m триггеров, первую группу из m элементов И, группу из т-1 элементов НЕ, группу из m элементов задержки, вторую группу из т-1 элементов И, третью группу из т-2 элемен5 тов И, шифратор, генератор импульсов, счетчик, три элемента И, три элемента задержки, реверсивный счетчик, четвертую группу элементов И, причем входы установки регистра являются входами заявок блока,

0 вход сброса регистра является входом базового такта блока и соединен с входами первого и второго элементов задержки, с первым входом шифратора, первыми входами первого и второго элементов И, выходы

5 с первого по m-й регистра поразрядно соединены с первыми входами элементов И первой группы, выходы которых с первого по (т-1)-й соединены соответственно с входами элементов НЕ группы, инверсные вы0 ходы триггеров группы соединены соответственно с вторыми входами элементов И первой группы, третьи входы которых соединены с выходом переполнения счетчика, вторым входом первого элемента И и

5 входом запуска генератора импульсов, выход второго элемента задержки соединен с входами сброса триггеров группы, входы установки которых соединены соответственно с выходами элементов задержки группы,

0 входы которых соединены соответственно с входами с второго по цгл+1)-й шифратора, входы элементов задержки с второго по m-й группы соединены с выходами элемента И второй группы, вход первого

5 элемента задержки группы соединен с выходом первого элемента И первой группы, выходы элементов И с второго по m-й первой группы соединены с первыми входами элементов И второй группы, выходы эле0 ментов НЕ с второго по (т-1)-й группы соединены соответственно с первыми входами элементов И третьей группы, выход первого элемента НЕ группы соединен с вторыми входами элементов И второй и

5 третьей групп, выход 1-го I 1...(т-2) элемента И третьей группы соединен с вторыми входами (1+1)-х элементов И второй и третьей групп, выход шифратора соединен с входом установки счетчика, выход генератора импульсов соединен со счетным входом счетчика, вторым входом второго элемента И и первым входом третьего элемента И, выход которого соединен с входом вычитания реверсивного счетчика, вход сложения которого соединен с выходом второго элемента И, вход сброса реверсивного счетчика соединен с выходом третьего элемента задержки, вход которого соединен с выходом первого элемента И, выход первого элемента задержки соединен с первыми входами элементов И четвертой группы и вторым входом третьего элемента И, информационные выходы реверсивного счетчика поразрядно соединены с вторыми входами элементов И четвертой группы, выходы которых являются выходами кода загрузки блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переменного приоритета | 1986 |

|

SU1417000A2 |

| УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПО ПРОЦЕССОРАМ | 1991 |

|

RU2017206C1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Устройство для управления реконфигурацией резервированной вычислительной систем | 1989 |

|

SU1718398A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для моделирования систем "Человек-машина | 1984 |

|

SU1275462A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Устройство для формирования признака команды | 1986 |

|

SU1387000A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки информации. Целью изобретения является расширение функциональных возможностей системы за счет адаптивного перераспределения загрузки процессоров. Поставленная цель достигается тем, что в вычислительную систему, содержащую основной и дополнительный процессоры, введены блок контроля загрузки и блок переключения заявок. 1 з.п. ф-лы, 3 ил.

а

Фиг. I

Фиг, г

1

Фиг.З

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-08-18—Подача