Os

О

VJ ю

fc

Изобретение относится к цифроанало- говой измерительной и вычислительной тех нике и может быть использовано для преобразования аналоговых величин в цифро вые

Целью изобретения является повыше ние точности

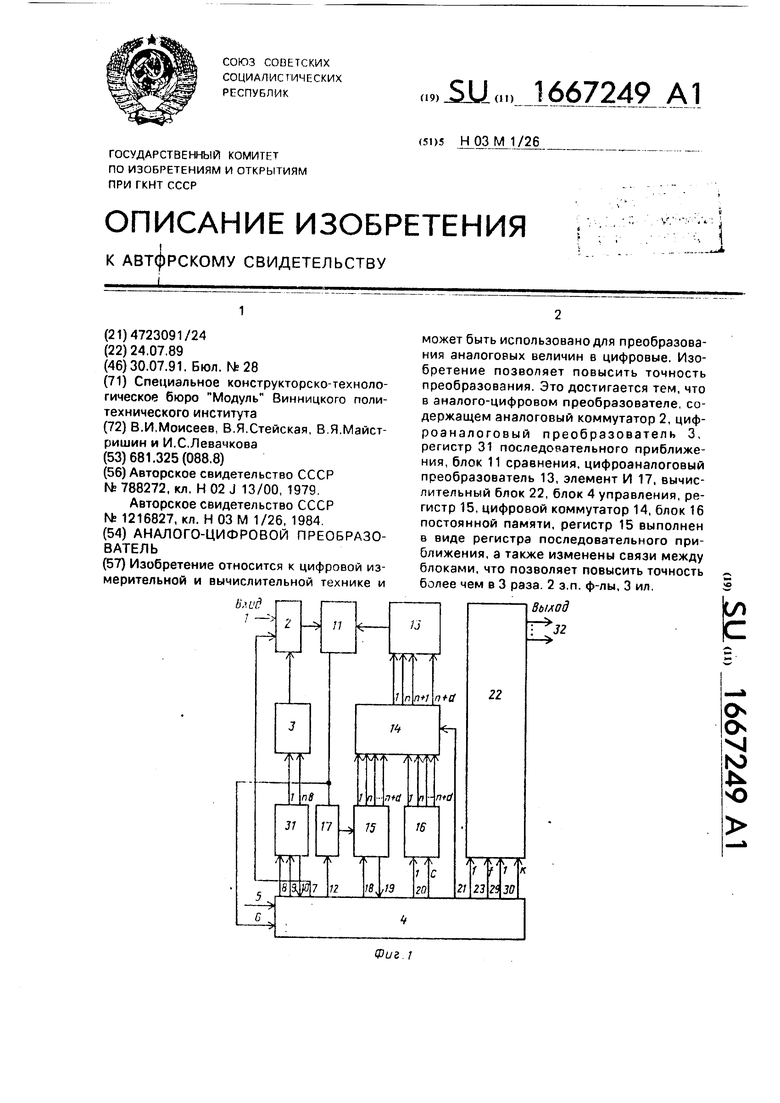

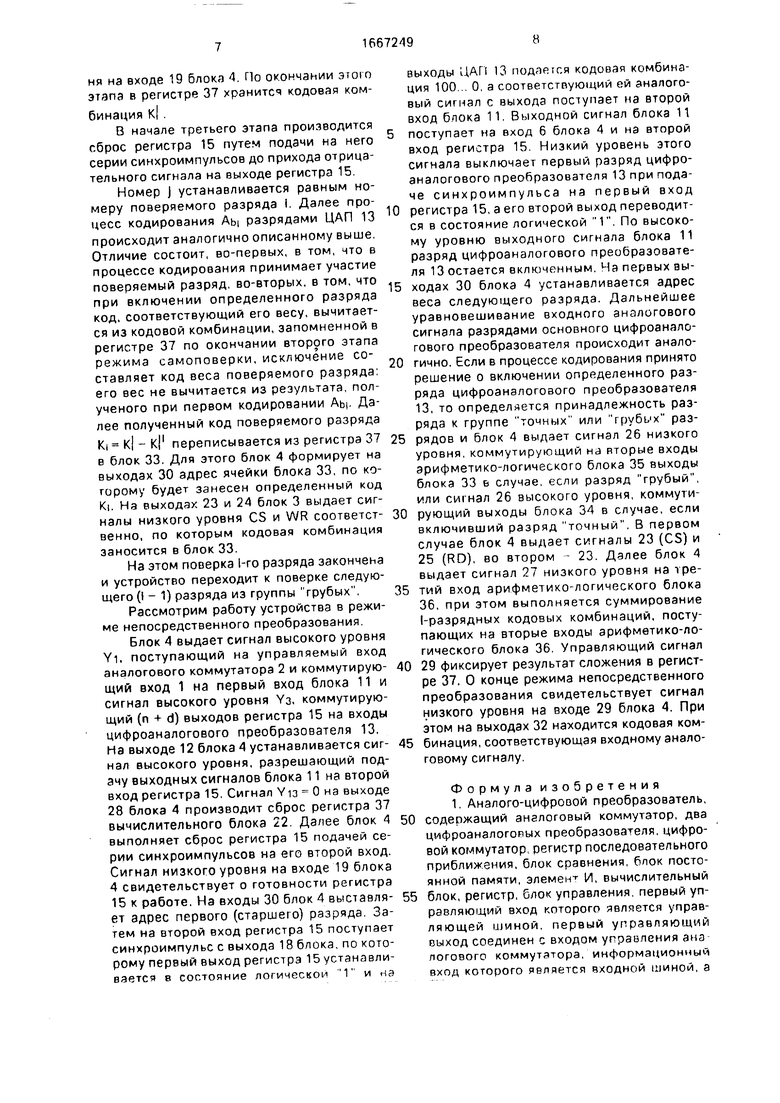

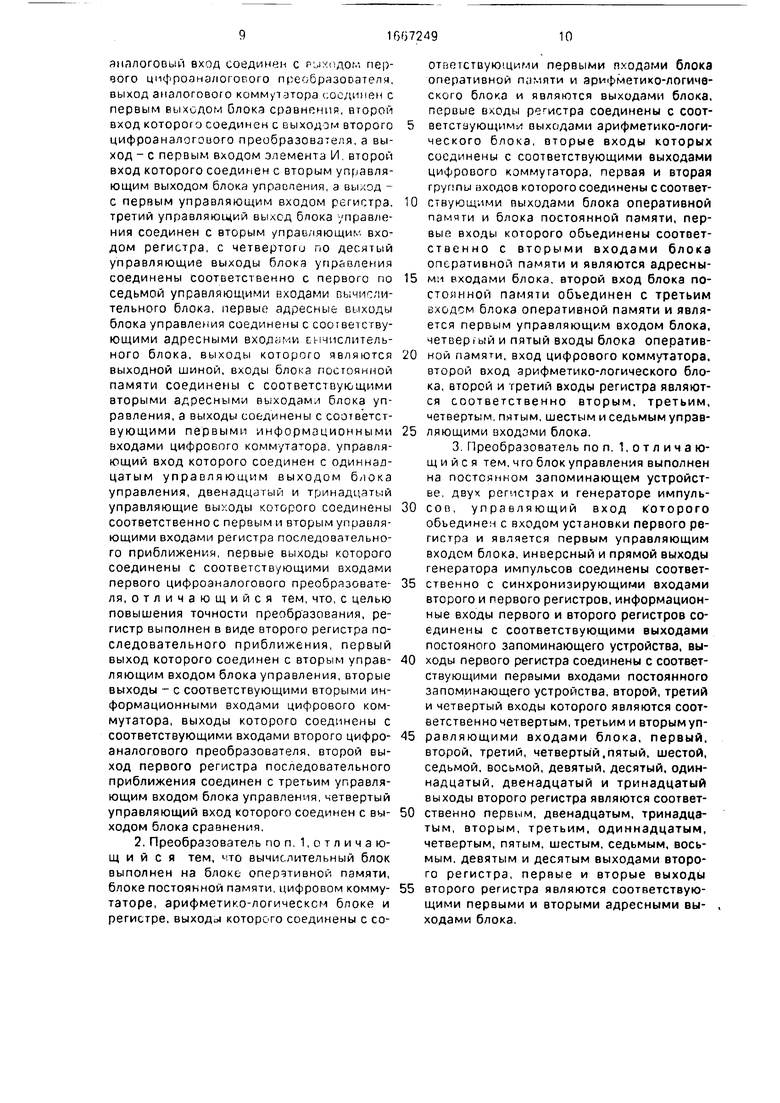

На фиг. 1 приведена функциональна схема устройства, на фиг 2 - функцио нальнэя схема вычислительного блока на фиг 3 - функциональная схема блока уп равления

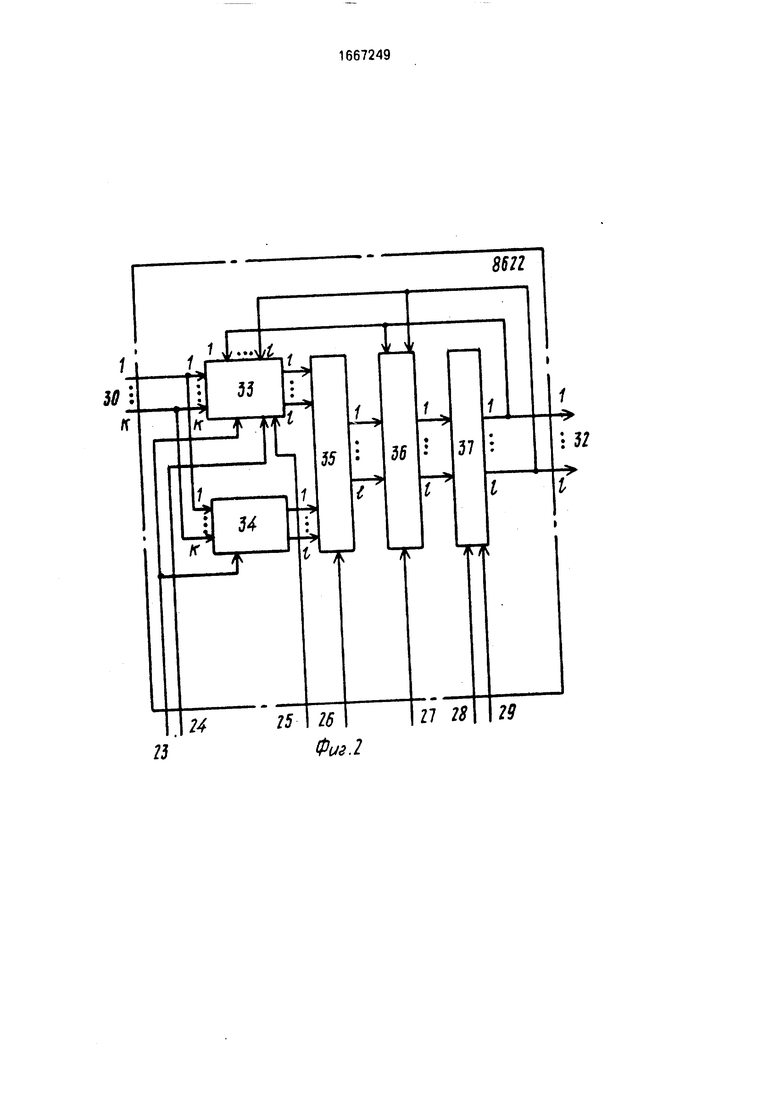

Преобразователь (фиг 1) содержит вход 1, аналоговый коммутатор 2 цифроанало говый преобразователь 3 (ЦАП), блок 4 уп равления и регистр последовательною приближения входы 5, 6 блока 4 упрнпле- ния, выходы 7, В 9, вход 10 блока 4 бло 11 сравнении, выходы 12 блока-4 цифро аналоговый преобразователь 13 (ЦАП) цифровой коммутатор 14 регистр 15 после довательногс приближения блок 1C постоянной памяти элемент И 17 выход 18 и вход 19 блока 4, адресный выходы 20 выход 21 блока 4, вычислительный блок 22 ВБ выхп ды 23 29, 30 блока 4, выходь. 32 устройства peincrp Ч последовательно1о ррибл е

НМЛ

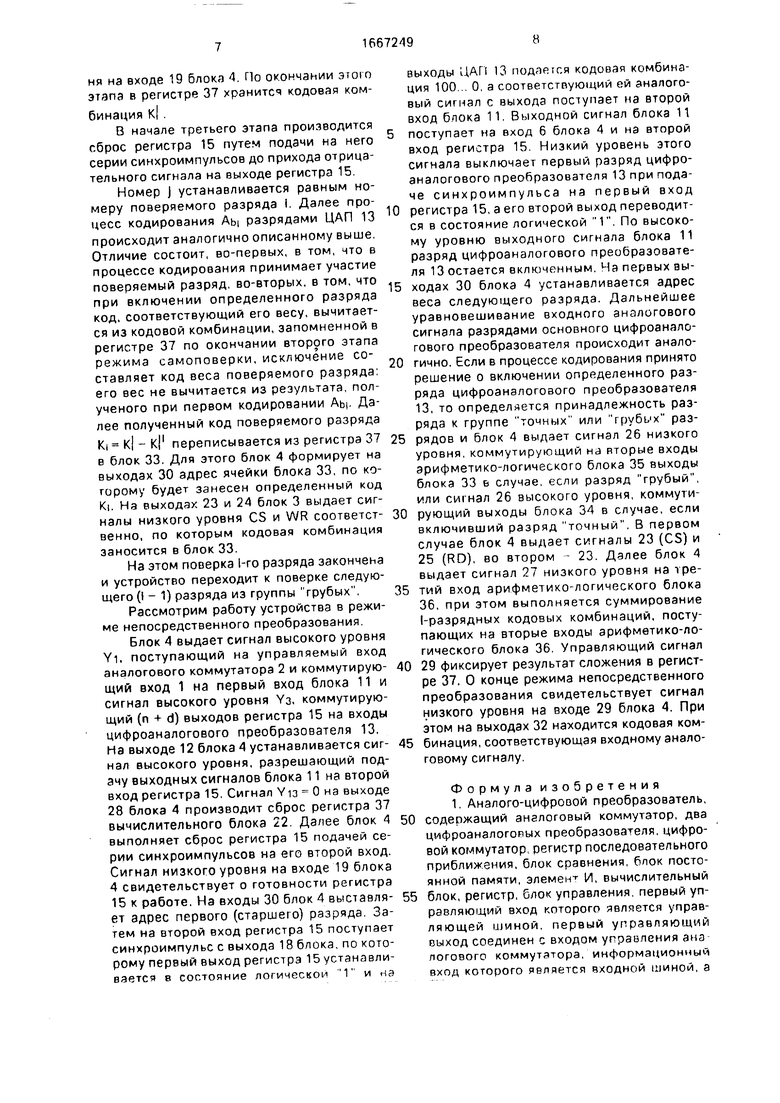

Вычислительный блик (фиг 2) содержит блок 33 оперативной памяти, блок 34 посю янной памяти цифровой коммутатор 15 арифметико-логический блок 36 (А Л Б) ре (истр 37

Блок управления содержит постоянное запоминающее устройство 38 (ПЗУ) пегист ры 39, 40

Цифроаналоговые преобразователи 3 13 должны быть выполнены на основе избы точных измерительных кодов

Количество адресных входов блока 16 выбирается из условия возможности эдое- сации массива, содержащего m С-разряд- ных кодовых комбинаций

С 1одгт(1)

Количество адресных входов вычисли тельного блока К определяется по числу n + d адресуемых разрядов и вычисляется по формуле

К logz (n + d)(2)

Количество управляющих влодов ьычис лительного блока 22 f зависит от реализа ции и типа элементов входящих в вычислительный блок Если вычислитель ный блок выполнить согласно фиг 2 го чо личество f входов вычислительного блокз равно 7,

Устройств фучкциогнирует в дв,х режи мах. самолов, рки и непосредственного аналого-цифрового npeofipaJOPuien t np рекцией примем во тором прои

стьо функционирует аналогично известному устройству При этом происходит преобразование аналогового сигнала Авх в двоичный код с помощью всех блоков устройства

за исключением цифроаналогового преобразователя 3 регистра 31 и блока 16. Указанное преобразование осуществляется с учетом кодов Ki реальных значений весов разрядов цифроаналогового преобразова

теля 13 Результат преобразования К(АВх) формируется в регистре вычислительного бгока 22 по фсимуле

п + d К(АВ0- 2 G k (3)

„

где d c,{0 1} двоичная цифра результата

уравновешивания Аьл сигналом Ак

Функционирование устройства в режи ме непосредственного преобразования

пеоиодимески прерывается режимом само поверки Частота перехода из режима в режим определи 1ся скоростью изменения реальных значении и°сов разрядов основ ного цифроаналогорого преобразователя

и зависит от стабильности параметров аналоговых узлов и изменения внешних условии

Работа устро ютга Р режиме сэмопо- ьерки отличается от итвесгного уст

о лчлва иным способом форг-.ирования вспомогательного аналогового сигнала

Данный процесс осуществляется при помощи спедующих блоков регистра 15 блока 16 цифрового коммутатора 14, цифроанэлогового преобразователя 13 блока 11 эпемента 17 аналогового коммутатора 2 цифроаналогового преобразователя 3 и регистра З1 При этом иифроаналоговый преобразователь 13 должен содержать n + d

разрядов, о цифроаналоговый преобразователь 13 (пь т) разрядов В свою очередь в блок 16 на этапе изготовления должны быть записаны m rb-разрядных кодовых комбинаций каждая из которых содержит только одну значащую единицу в группе корректиоуемых разрядов(1-м разряде)и не- скотько единиц в группе некорректируемых Разрядов а именно 12 I m m - 1 пв

Кы 0 0 1 0 х х

Рассмотрим работу устройства в режиме сэмоппверки (ОПС 4). Переход в режим самоповерки происходит при подаче отрицательного ,са на вход 5 блока 4

Режим самсповерки каждого 1-го разряда состоит И2 ipex этапов На первом эта пе производится формирование аналоговой пелич чы Аь, Второй этап зеключаетсч г г диропании чесами ЦАП 13 и формировании кодовой комбинации K| в регистре 37, На третьем этапе выполняется формирование кодовой комбинации к| , определение кода KI K - и запись его по адресу ADRi в блок 33.

В начале режима самоповерки I устанавливается равным т. Номер старшего разряда, участвующего в кодировании 1-го разряда, устанавливается равным (I + 1), Затем блок 4 производит сброс регистров 31,

15подачей серии синхроимпульсов на их входы 8 и 18 соответственно. Низкий уровень сигнала на входах 10, 19 блока 4 свидетельствует о том, что на всех выходах регистров 31, 15 установлены уровни логического О. Далее бпок 4 выдает отрицательный импульс на выходе 28, в результате чего производится сброс регистра 37. Сигнал низкого уровня на выходе 7 блока 4 коммутирует выход ЦАП 3 на первый вход блока 11, а сигнал низкого уровня на выходе 21 блока 4 коммутирует n + d выходы блока

16на n + d входы ЦАП 13.

На адресной шине блока 16 блок 4 формирует такой адрес, при котором на выход блока 16 выдается кодовая комбинация Кы. Код Кы поступает на вход ЦАП 13, на выходе которого устанавливается соответствующая входному коду Кь, аналоговая величина Abj. Далее производится поразрядное уравновешивание аналоговой величины АЫ разрядами ЦАП 3 следующим образом. На первый вход регистра 31 подается положительный импульс, по переднему фронту которого первый выход регистра 31 устанавливается в состояние логической 1, и на вход ЦАП 3 поступает кодовая комбинация 100... О, а соответствующий ей аналоговый сигнал с выхода ЦАП 3 поступает на первый вход блока 11. Выходной сигнал блока 11 поступает на вход б блока 4. По низкому уровню этого сигнала принимается решение о выключении первого разряда выходной шины регистра 31 и на его вход 9 блок 4 выдает сигнал низкого уровня. В противном случае на данный вход поступает уровень логической 1. По заднему фронту импульса на первом входе регистра 31 информация с его второго входа переписывается на первый вход, а следующий за ним выход переводится в состояние логической 1. Далее устройство работает аналогичным образом. По окончании процесса поразрядного уравновешивания аналоговой величины АЫ разрядами ЦАП 3 на выходе регистра 31 устанавливается сигнал низкого уроаня, который поступает на вход 10

блока 4. На выходе ЦАП 3 при этом устанавливается требуемое значение вспомогательной величины АЫ. которая поступает на первый вход блока 11.

После этого начинается второй этап режима самоповерки. Блок 4 выдает сигнал 21, равный логической 1. При этом выходная шина регистра 15 коммутируется на входы ЦАП 13. Далее блок 4 подает

(j - 1) импульсов на вход 18 регистра 15, предварительно подав на второй вход элемента 17 отрицательный сигнал. В результате на (J - 1) старших разрядах регистра 15 установятся уровни логического О, а

j-й разряд установится а состояние логической 1. Далее блок 4 выдает положительный сигнал на выходе 12, который разрешает прохождение сигналов с выхода блока 11 на второй вход регистра 15. В процессе

уравновешивания блок 4 анализирует состояние выхода блока 11. Если сигнал на этом выходе положительный, то блок 4 формирует на выходах 30 адрес ADRj и подает сигнал низкого уровня на блок 22.

Далее анализируется принадлежность J- го разряда к группе точных (j m) или неточных 0 гп) разрядов. При выполнении условия j m блок 4 выдает сигнал низкого уровня на выходе 26, по которому на вторые

входы АЛ Б 36 коммутируются выходы блока 33, и сигнал низкого уровня на выходе 25, по которому информация из блока 33 считывается на вторые входы АЛ Б 36.

При J m блок 4 выдает сигнал высокого

уровня на выходе 26, по которому на вторые входы АЛ Б 36 коммутируются выходы; блока 34.

После этого блок 4 выдает отрицательный импульс на выходе 27, по которому

происходит суммирование данных, присутствующих на первом и втором входах АЛ Б36. Далее блок 4 выдает сигнал высокого уровня на выход 23, отключающий блок 33 и 34 от соответствующей группы

входов коммутатора 35. По переднему фронту сигнала на выходе 29 блока 3 информация с выходов АЛБ 36 переписывается в регистр 37.

По заднему фронту импульса на пораом

входе регистра 15 информация с его второго входа переписывается на J-й выход, а следующий за ним 0 + 1)-й выход переводится в состояние логической 1. После этого производится увеличение номера разряда j на

1 и блок 4 переходит к анализу сигнала на входе 6. Далее процесс кодирования АЫ происходит аналогично.

О конце второго этапа режима самоповерки свидетельствует сигнал низкого уровня на входе 19 блока 4. По окончании этого этапа в регистре 37 хранится кодовая комбинация к|.

В начале третьего этапа производится сброс регистра 15 путем подачи на него серии синхроимпульсов до прихода отрицательного сигнала на выходе регистра 15.

Номер j устанавливается равным номеру поверяемого разряда I. Далее процесс кодирования АЫ разрядами ЦАП 13 происходит аналогично описанному выше. Отличие состоит, во-первых, в том, что в процессе кодирования принимает участие поверяемый разряд, во-вторых, в том, что при включении определенного разряда код, соответствующий его весу, вычитается из кодовой комбинации, запомненной в регистре 37 по окончании второго этапа режима самоповерки, исключение составляет код веса поверяемого разряда: его вес не вычитается из результата, полученого при первом кодировании АЫ. Далее полученный код поверяемого разряда

Ki K| - переписывается из регистра 37 в блок 33. Для этого блок 4 формирует на выходах 30 адрес ячейки блока 33, по которому будет занесен определенный код Ki. На выходах 23 и 24 блок 3 выдает сигналы низкого уровня CS и WR соответственно, по которым кодовая комбинация заносится в блок 33.

На этом поверка 1-го разряда закончена и устройство переходит к поверке следующего (I - 1) разряда из группы грубых,

Рассмотрим работу устройства в режиме непосредственного преобразования.

Блок 4 выдает сигнал высокого уровня YI, поступающий на управляемый вход аналогового коммутатора 2 и коммутирующий вход 1 на первый вход блока 11 и сигнал высокого уровня Уз, коммутирующий (n + d) выходов регистра 15 на входы цифроаналогового преобразователя 13. На выходе 12 блока 4 устанавливается сигнал высокого уровня, разрешающий подачу выходных сигналов блока 11 на второй вход регистра 15. Сигнал Утз 0 на выходе 28 блока 4 производит сброс регистра 37 вычислительного блока 22. Далее блок 4 выполняет сброс регистра 15 подачей серии синхроимпульсов на его второй вход. Сигнал низкого уровня на входе 19 блока 4 свидетельствует о готовности регистра 15 к работе. На входы 30 блок 4 выставляет адрес первого (старшего) разряда. Затем на второй вход регистра 15 поступает синхроимпульс с выхода 18 блока, по которому первый выход регистра 15 устанавливается в состояние логической 1 и на

выходы ЦАП 13 подается кодовая комбинация 100... О, а соответствующий ей аналоговый сигнал с выхода поступает на второй вход блока 11. Выходной сигнал блока 11

поступает на вход 6 блока 4 и на второй вход регистра 15. Низкий уровень этого сигнала выключает первый разряд цифро- аналогового преобразователя 13 при подаче синхроимпульса на первый вход

регистра 15, а его второй выход переводится в состояние логической 1. По высокому уровню выходного сигнала блока 11 разряд цифроаналогового преобразователя 13 остается включенным. На первых выходах 30 блока 4 устанавливается адрес веса следующего разряда. Дальнейшее уравновешивание входного аналогового сигнала разрядами основного цифроаналогового преобразователя происходит аналогично. Если в процессе кодирования принято решение о включении определенного разряда цифроаналогового преобразователя 13, то определяется принадлежность разряда к группе точных или грубь х разрядов и блок 4 выдает сигнал 26 низкого уровня, коммутирующий на вторые входы арифметико-логического блока 35 выходы блока 33 в случае, если разряд грубый, или сигнал 26 высокого уровня, коммутирующий выходы блока 34 в случае, если включивший разряд точный. В первом случае блок 4 выдает сигналы 23 (CS) и 25 (RD), во втором - 23. Далее блок 4 выдает сигнал 27 низкого уровня на третий вход арифметико-логического блока 36, при этом выполняется суммирование 1-разрядных кодовых комбинаций, поступающих на вторые входы арифметико-логического блока 36. Управляющий сигнал

29 фиксирует результат сложения в регистре 37. О конце режима непосредственного преобразования свидетельствует сигнал низкого уровня на входе 29 блока 4. При этом на выходах 32 находится кодовая комбинация, соответствующая входному аналоговому сигналу.

Формула изобретения

1. Аналого-цифровой преобразователь,

содержащий аналоговый коммутатор, два цифроаналогопых преобразователя, цифровой коммутатор, регистр последовательного приближения, блок сравнения, блок постоянной памяти, элемент И, вычислительный

блок, регистр, блок управления, первый управляющий вход которого является управляющей шиной, первый управляющий выход соединен с входом управления ана лотового коммутатора, информационный вход которого является входной шиной, а

диалоговый вход соединен с первого цифроанэлогового преобразователя, выход аналогового коммутатора (.осдинен с первым выходом Блока сравнения, втором вход которого соединен с выходам второго цифроэналогоиого преобразователя, а выход - с первым входом элемента И второй вход которого соединен с вторым управляющим выходом блока управления, а выход - с первым управляющим входом регистра. третий управляющий выхсд блока -/правления соединен с вторым управляющие входом регистра, с четвертого по десятый управляющие выходы блока управления соединены соответственно с первого по седьмой управляющими входами вычислительного блока, первые адресные выходы блока управления соединены с соответствующими адресными входьми Енчпслитель- ного блока, выходы которого являются выходной шиной, входы блока постоянной памяти соединены с соответствующими вторыми адресными выходами блока управления, а выходы соединены с соответствующими первыми информационными входами цифрового комм/татора, управляющий вход которого соединен с одиннадцатым управляющим выходом блока управления, двенадцатый и тринадцатый управляющие выходы которого соединены соответственно с первым и вторым управляющими входами регистра последовательного приближения, первые выходы которого соединены с соответствующими входами первого цифроаналогового преобразователя, отличающийся тем, что, с целью повышения точности преобразования, регистр выполнен в виде второго регистра последовательного приближения, первый выход которого соединен с вторым управляющим входом блока управления,вторые выходы - с соответствующими вторыми информационными входами цифрового коммутатора, выходы которого соединены с соответствующими входами второго цифро- аналогового преобразователя, второй выход первого регистра последовательного приближения соединен с третьим управляющим входом блока управления, четвертый управляющий вход которого соединен с выходом блока сравнения.

2, Преобразователь по п. 1, о т л и ч а га- ид и и с я тем, что вычислительный блок выполнен на блоке оперативной памяти, блоке постоянной памяти, цифровом коммутаторе, арифметико-логическом блоке и регистре, выходы которого соединены с соответствующими первыми пходами блока оперативной памяти и арифметико-логического блока и являются выходами блока, первые регистра соединены с соот- ветстаующим выходами арифметико-логического блока, вторые входы которых соединены с соответствующими выходами цифрового коммутатора, первая и вторая группы входов которого соединены с соответствующими выходами блока оперативной памяти и блока постоянной памяти, первые входы которого обьединены соответственно с вторыми входами блока оперативной памяти и являются адресными входами блока, второй вход блока постоянной памяти объединен с третьим входом блока оперативной памяти и является первым управляющим входом блока, нетвер)Ый и пятый входы блока оперативной памяти, вход цифрового коммутатора. второй вход арифметико-логического блока, второй и третий входы регистра являются соответственно вторым, третьим, четвертым, пятым, шестым и седьмым управляющими входами блока.

3 Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что блок управления выполнен на постоянном запоминающем устройстве, двух регистрах и генераторе импульсов, управляющий вход которого объединен с входом установки первого регистра и является первым управляющим входом блока, инверсный и прямой выходы генератора импульсов соединены соответственно с синхронизирующими входами второго и первого регистров, информационные входы первого и второго регистров соединены с соответствующими выходами постояного запоминающего устройства, выходы первого регистра соединены с соответствующими первыми входами постоянного запоминающего устройства, второй, третий и четвертый входы которого являются соответственно четвертым, третьим и вторымулравляющими входами блока, первый, второй, третий, четвертый.пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый и тринадцатый выходы второго регистра являются соответственно первым, двенадцатым, тринадцатым, вторым, третьим, одиннадцатым, четвертым, пятым, шестым, седьмым, восьмым, девятым и десятым выходами второго регистра, первые и вторые выходы

второго регистра являются соответствующими первыми и вторыми адресными выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1319279A1 |

| Многоканальный коммутатор аналоговых сигналов | 1988 |

|

SU1598149A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1702525A1 |

| Многоканальное устройство для ввода-вывода аналоговой информации | 1988 |

|

SU1564606A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

Изобретение относится к цифровой измерительной и вычислительной технике и может быть использовано для преобразования аналоговых величин в цифровые. Изобретение позволяет повысить точность преобразования. Это достигается тем, что в аналого-цифровом преобразователе, содержащем аналоговый коммутатор 2, цифроаналоговый преобразователь 3, регистр 31 последовательного приближения, блок 11 сравнения, цифроаналоговый преобразователь 13, элемент И 17, вычислительный блок 22, блок 4 управления, регистр 15, цифровой коммутатор 14, блок 16 постоянной памяти, регистр 15 выполнен в виде регистра последовательного приближения, а также изменены связи между блоками, что позволяет повысить точность более чем в 3 раза. 2 з.п. ф-лы, 3 ил.

| Искробезопасная система дистанционного питания | 1979 |

|

SU788272A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-07-30—Публикация

1989-07-24—Подача