1

Изобретение относится к цифровой измерительной и вычислительной технике и может быть использовано для преобразования аналоговых величин в цифровые.

Цель изобретения - расширение функциональных возможностей аналого- цифрового преобразователя.

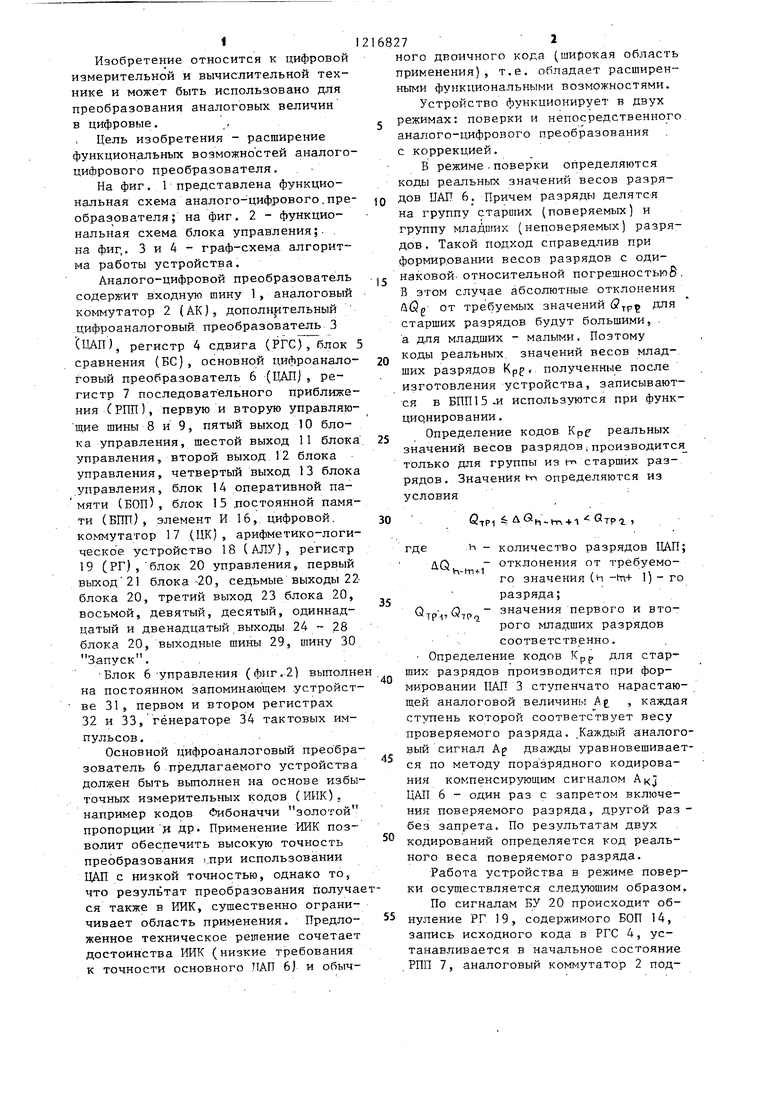

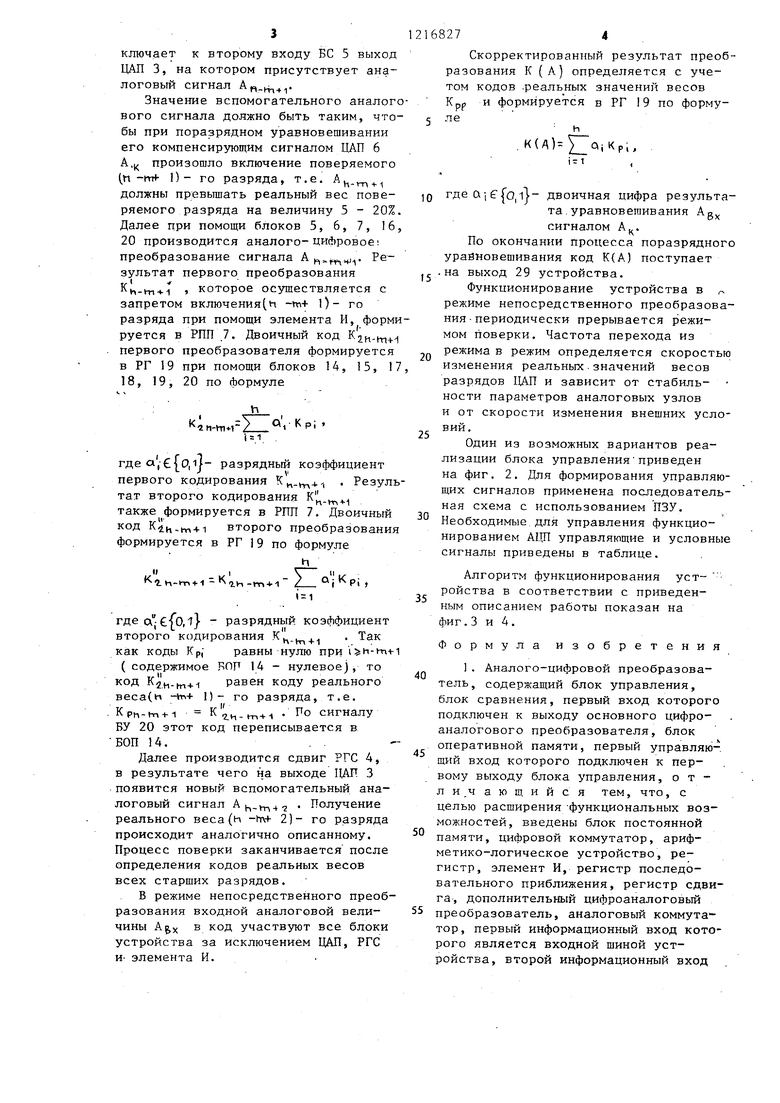

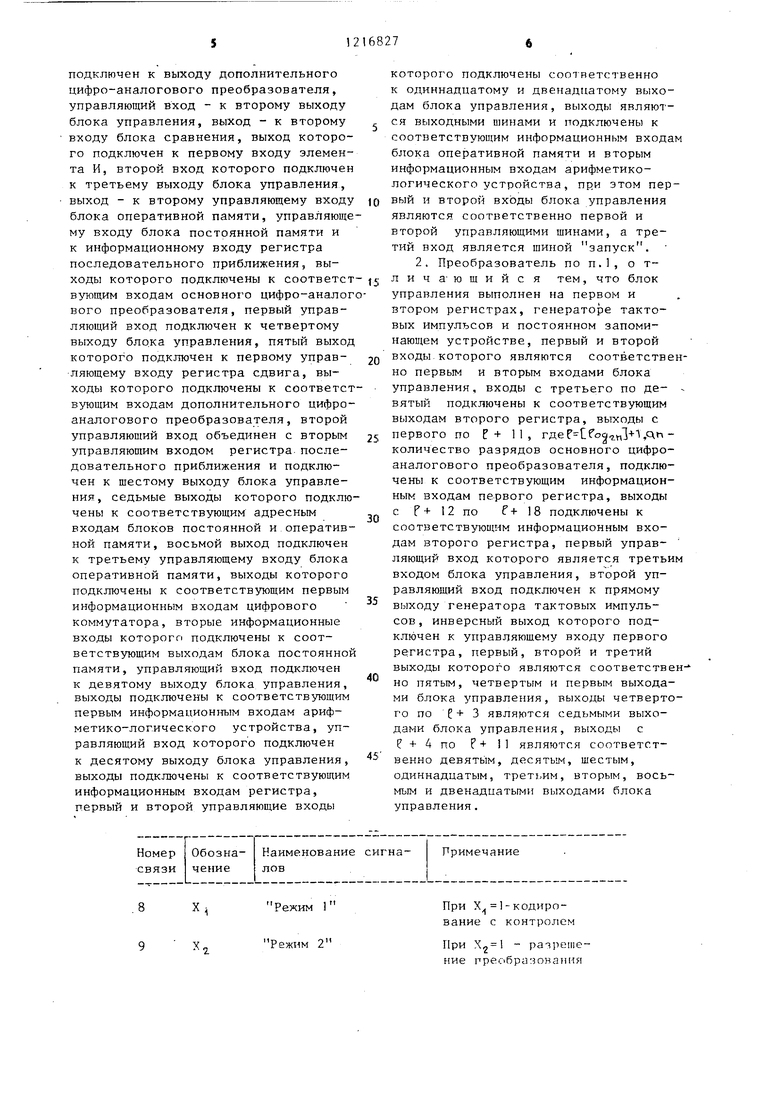

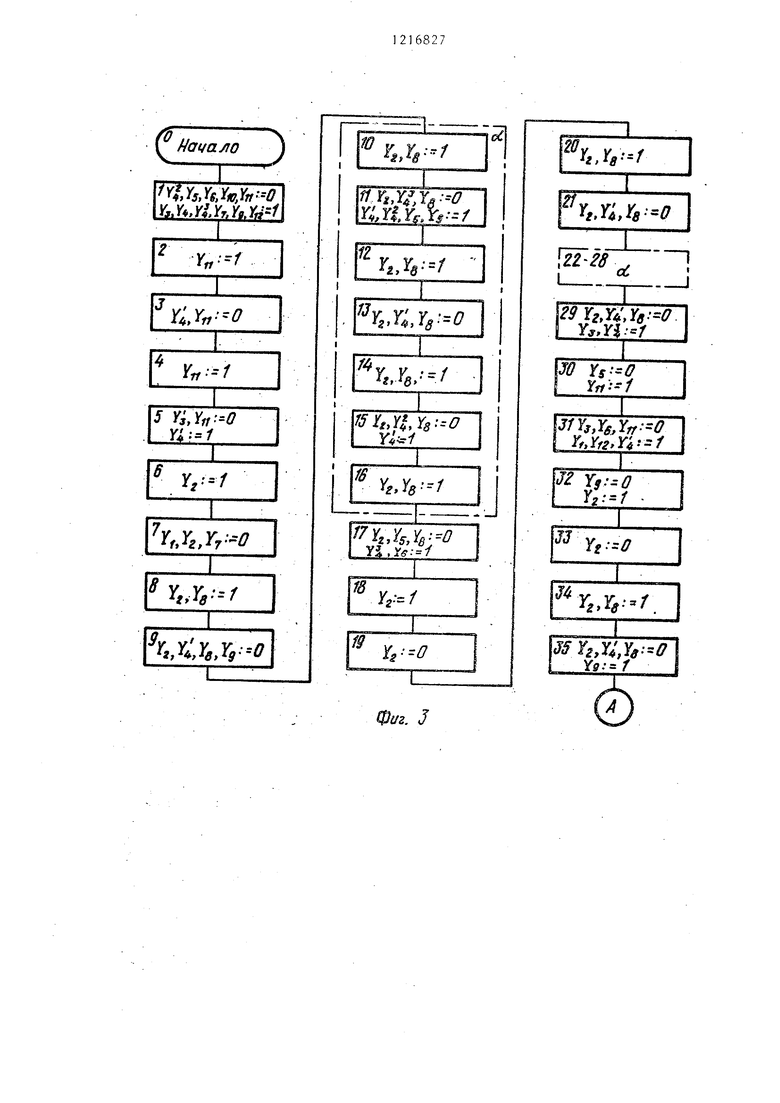

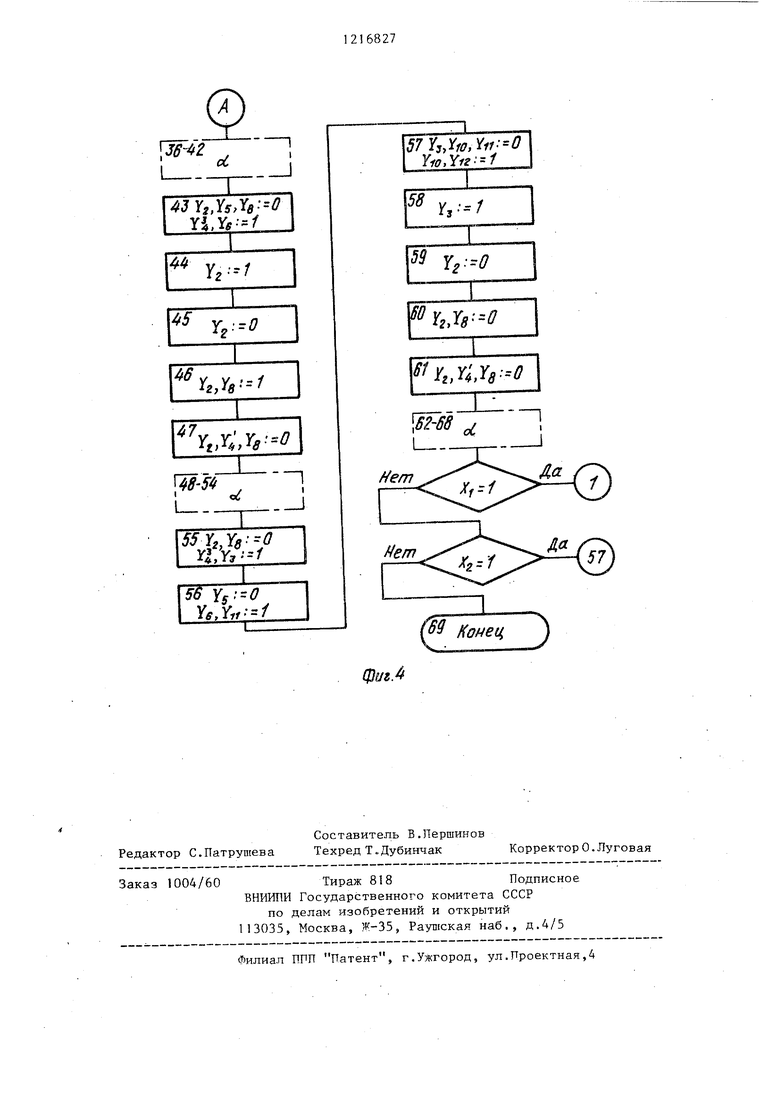

На фиг.1 представлена функциональная схема аналого-цифрового.преобразователя ; на фиг, 2 - функциональная схема блока управления;. на фиг,, 3 и 4 - граф-схема алгоритма работы устройства.

Аналого-цифровой преобразователь содержит входную шину 1, аналоговый коммутатор 2 (АК), дополнительный цифроаналоговый преобразователь 3 (ЦАП), регистр 4 сдвига (РГС), блок сравнения (БС), основной цифроаналоговый преобразователь 6 (иДП), регистр 7 последовательного приближения СРПП ), первую и вторую управляю- щие шины 8 и 9, пятый выход 10 блока управления, шестой выход 11 блока управления, второй выход 12 блока управления, четвертый выход 13 блока управления, блок 14 оперативной памяти (БОП) , блок 15 .постоянной памяти (БПП), элемент И 16, цифровой, коммутатор 17 (ЦК), арифметико-логическое устройство 18 (АЛУ), регистр 19 (РГ), блок 20 управления, первый выход 21 блока -20, седьмые выходы 22 блока 20, третий выход 23 блока 20, восьмой, девятый, десятый, одиннадцатый и двенадцатый.выходы, 24-28 блока 20, выходные шины 29, шину 30 Запуск, . .

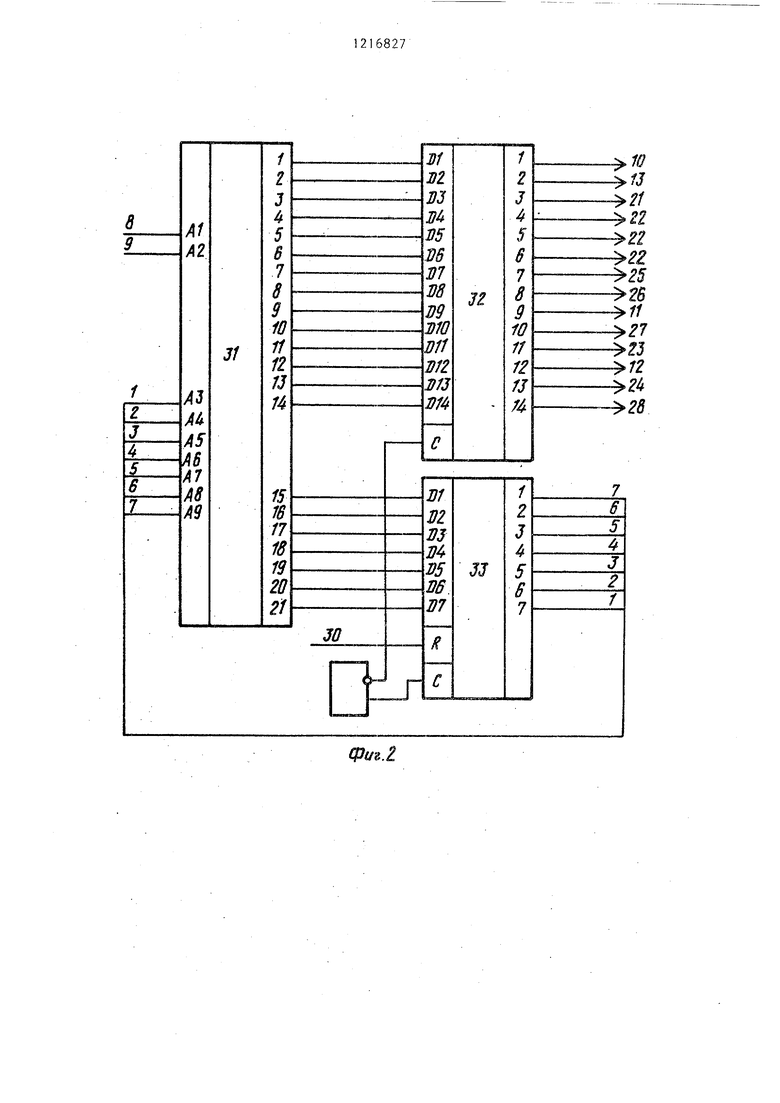

Блок 6-управления (фиг,2) выполне на постоянном запоминающем устройстве 31, первом и втором регистрах 32 и 33, генераторе 34 тактовых импульсов ,

Основной цифроаналоговый преобразователь 6 предлагаемого устройства должен быть вьтолнен на основе избыточных измерительных кодов (ИНК), например кодов Фибоначчи золотой пропорции и др. Применение ПИК позволит обеспечить высокую точность преобразования при использовании ЦАЦ с низкой точностью, однако то, что результат преобразования получаеся также в НИК, существенно ограничивает область применения. Предложенное техническое решение сочетает достоинства MiK (низкие требования к точности основного ПАП 6) и обыч27 2

ного двоичного кода (широкая область применения), т,е, обладает расширенными функциональными возможностями. Устройство функционирует в двух режимах: поверки и непосредственного аналого-цифрового преобразования с коррекцией.

В режиме.поверки определяются коды реальных значений весов разрядов ЦАП 6, Причем разряды делятся на группу старших (поверяемых) и группу младших (неповеряемых) разрядов . Такой подход справедлив при формир.овании весов разрядов с оди

наковой- относительной погрешностью .

В этом случае абсолютные отклонения u(pg от требуемых значений для старших разрядов будут большими, . а для младших - малыми. Поэтому

коды реальных, значений весов млад-, ших разрядов Крр« полученные после изготовления устройства, записываются в БПП15.И используются при функ- цирнировании,

Определение кодов V.pp реальных значений весов разрядов;производится только для группы из t-n старших разрядов. Значения ьп определяются из условия

( ла.т + ,

где h - количество разрядов ЦАП; дО - отклонения от требуемоh-lTH-1

ГО значения (и -( 1) - го разряда;

Q-fp , значения первого и второго младших разрядов соответственно, Определение кодов Кр для стар

ших разрядов производится при формировании ПАП 3 ступенчато нарастающей аналоговой величинь А , каждая ступень которой соответствует весу проверяемого разряда, .Каждый аналоговый сигнал Ар дважды уравновешивается по методу поразрядного кодирования компенсирующим сигналом ЦАП 6 - один раз с запретом включения поверяемого разряда, другой раз - без запрета. По результатам двух кодирований опре.деляется код реального веса поверяемого разряда.

Работа устройства в режиме поверки осуществляется следуюшим образом.

По сигналам БУ 20 происходит об- нуление РГ, 19, содержимого БОП 14, запись исходного кода в РГС 4, устанавливается в начальное состояние РПП 7, аналоговый коммутатор 2 под3

ключает к второму входу БС 5 выход ЦАП 3, на котором присутствует аналоговый сигнал Af,..

Значение вспомогательного аналогового сигнала должно быть таким, чтобы при поразрядном уравновешивании его компенсирующим сигналом ЦАП 6 А.| произошло включение поверяемого (п-mf 1)- го разряда, т.е. А. должны превышать реальный вес поверяемого разряда на величину 5 - 20%. Далее при помощи блоков 5, 6, 7, 16, 20 производится аналого-цифровое преобразование сигнала А (,,HJI зультат первого преобразования К,.„. , которое осуществляется с запретом включения(и tTi+ l)- го разряда при помощи элемента И, формируется в РПП 7. Двоичный код К,.. первого преобразователя формируется в РГ 19 при помощи блоков 14, 15, 17 18, 19, 20 по формуле

-ZM-VTu-rZ P

, .

где ci ,- 0|i|- разрядный коэффициент первого кодирования K.j.-, . Резултат второго кодирования К . также формируется в РПП 7, Двоичный код К,,„ц.1 второго преобразовани формируется в РГ 19 по формуле

И

I 11., + 1 - -m + i 2 Pi

,1} разрядный коэффициент второго кодирования К. . Так как коды Кр, равны нулю при 1: и-ит ( содержимое ROF 14 - нулевое), то код K n-fri-n равен коду реального веса(и -tr,+ 1)- го разряда, т.е. Kpf,-Hn-i К .. . По сигналу БУ 20 этот код переписывается в БОИ 14.

Далее производится сдвиг РГС 4, в результате чего на выходе ЦАП 3 появится новый вспомогательный аналоговый сигнал А.4-2 Получение реального веса(н -гти- 2)- го разряда происходит аналогично описанному. Процесс поверки заканчивается после определения кодов реальных весов всех старших разрядов.

В режиме непосредственного преобразования входной аналоговой величины Ag,x в код участвуют все блоки устройства за исключением ЦАП, РГС И элемента И.

2168274

Скорректированный результат преобразования К (А) определяется с учетом кодов .реальных значений весов

5

Крр ле

и формируется в РГ 19 по форму

I 1

К(А) Oi Kpi,

i-1

Q где Q i f | О|il- двоичная цифра результата, уравновешивания Ag сигналом А...

А

По окончании процесса поразрядного урайиовешивания код К(А) поступает J .на выход 29 устройства.

Функционирование устройства в режиме непосредственного преобразования периодически прерывается режимом поверки. Частота перехода из режима в режим определяется скоростью изменения реальных.значений весов разрядов ЦАП и зависит от стабильности параметров аналоговых узлов и от скорости изменения внешних условий.

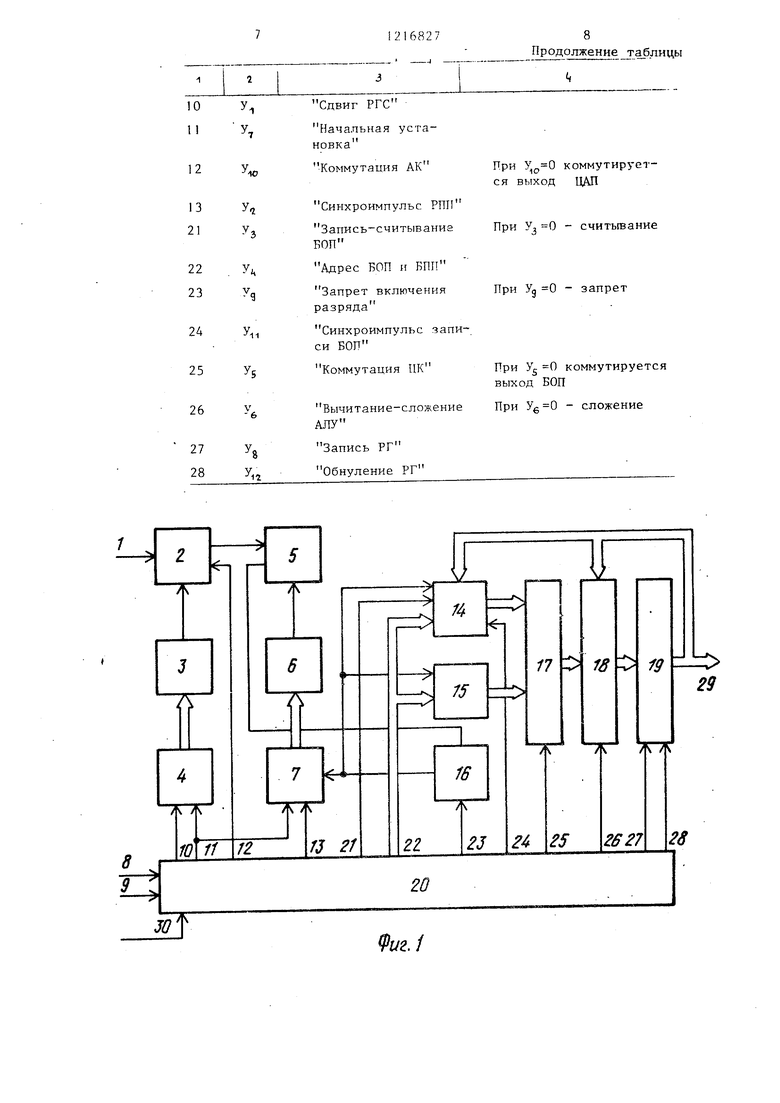

Один из возможных вариантов реализации блока управления приведен на фиг. 2. Для формирования управляющих сигналов применена последовательная схема с использованием ПЗУ. Необходимые для управления функционированием АЦП управляющие и условные сигналы приведены в таблице.

5

Алгоритм функционирования уст- ройства в соответствии с приведенным описанием работы показан на фиг.3 и 4.

Формула изобретения . Аналого-цифровой преобразова

тель, содержащий блок управления, блок сравнения, первый вход которого подключен к выходу основного цифро- аналогового преобразователя, блок оперативной памяти, первый управляю-, щий вход которого подключен к первому выходу блока управления, о т - ли ч ающийся тем, что, с целью расширения функциональных возможностей, введены блок постоянной памяти, цифровой коммутатор, арифметико-логическое устройство, регистр, элемент И, регистр последовательного приближения, регистр сдвига, дополнительный цифроаналоговый преобразователь, аналоговый коммутатор , первый информационный вход которого является входной шиной устройства, второй информационный вход

подключен к выходу дополнительного цифро-аналогового преобразователя, управляющий вход - к второму выходу блока управления, выход - к второму входу блока сравнения, выход которого подключен к первому входу элемента И, второй вход которого подключен к третьему выходу блока управления, выход - к второму управляющему входу блока оперативной памяти, управляющему входу блока постоянной памяти и к информационному входу регистра последовательного приближения, выходы которого подключены к соответствующим входам основ Hoi o цифро-аналог вого преобразователя, первый управляющий вход подключен к четвертому выходу блока управления, пятый выход которог о подключен к первому управляющему входу регистра сдвига, выходы которого подключены к соответствующим входам дополнительного цифро- аналогового преобразователя, второй управляющий вход объединен с вторым управляющим входом регистра, последовательного приближения и подключен к шестому выходу блока управления , седьмые выходы которого подключены к соответствующим адресным входам блоков постоянной и оперативной памяти, восьмой выход подключен к третьему управляющему входу блока оперативной памяти, выходы которого подключены к соответствующим первым информационным входам цифрового коммутатора, вторые информационные входы которого подключены к соответствующим выходам блока постоянной памяти, управляющий вход подключен к девятому выходу блока управления, выходы подключены к соответствующим первым информационным входам арифметико-логического устройства, управляющий вход которого подключен к десятому выходу блока управления, выходы подключены к соответствующим информационным входам регистра, первый и второй управляющие входы

Режим 1 Режим 2

0

s

0

5

0

5

которого подключены соответственно к одиннадцатому и двенадцатому выходам блока управления, выходы являются выходными шинами и подключены к соответствующим информационным входам блока оперативной памяти и вторым информационным входам арифметико- логического устройства , пр.и этом первый и второй входы блока управления являются соответственно первой и второй управляющими щинами, а третий вход является шиной запуск.

2. Преобразователь по п.1, о т- лича юшийся тем, что блок управления выполнен на первом и втором регистрах, генераторе тактовых импульсов и постоянном запоминающем устройстве, первый и второй входы которого являются соответственно первым и вторым входами блока управления, входы с третьего по де- вятый подключены к соответствующим выходам второго регистра, выходы с первого по Р+ 11, гл.e.o , количество разрядов основного цифро- аналогового преобразователя, подключены к соответствующим информационным входам первого регистра, выходы с Г+ 12 по f+ 18 подключены к соответствующим информационным входам второго регистра, первый управляющий вход которого является третьим входом блока управления, второй управляющий вход подключен к прямому выходу генератора тактовых импульсов, инверсный выход которого подключен к управляющему входу первого регистра, первый, второй и третий выходы которого являются соответственно пятым, четвертым и первым выходами блока управления, выходы четвертого по f + 3 являются седьмыми выходами блока управления, выходы с Р + 4 по f + i 1 являются соответственно девятым, десятым, щестым, одиннадцатым, третьим, вторым, восьмым и двенадцатыми выходами блока управления.

При Х 1-кодиро- вание с контролем

При - разрешение преобра ования

to

УЛ 9

УН У5

-6

17

новка Коммутация АК

Синхроимпульс РПП

Запись-считывание БОП

Адрес БОП и БПП

Запрет включения разряда

Синхроимпульс запи- си БОП

Коммутация ЦК

Вычитание-сложение АЛУ

Запись РГ Обнуление РГ

JO

Продолжение таблицы

При У, коммутируется выход ЦАП

При У 0 - считьшание

При Уд 0 - запрет

При У 0 коммутируется выход БОП

При Уе 0 - сложение

te/

фа..2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257848A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1667249A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257847A1 |

Изобретение относится к цифровой измерительной и вычислительной технике и может быть использовано для преобразования аналоговых величин в цифровые. Изобретение позволяет расширить функциональные возможности аналого-цифрового преобразователя (АЦП), работающего в избыточно-измерительном коде (НИК). Применение ИИК обеспечивает высокую точность преобразования при использовании цифроаналогового преобразовате- ,ля низкой точности, а введение блока постоянной памяти,,цифрового коммутатора, арифметико-логического устройст ва, регистра, элемента И, регистра последовательного приближения, регистра сдвига и дополнительного цифро- аналогового преобразователя, которые обеспечивают работу АЦП в режиме поверки- и непосредственного преобразования с коррекцией, позволяет получить результат преобразования в обычном двоичном коде, т.е. в изобретении сочетаются достоинот- ва ИИК (низкие требования к точности ТДАЛ) и обычного двоичного кода (широкая область применения). 1 з.п, ф-лы, 4 ил. (Л С с о С N9

| Искробезопасная система дистанционного питания | 1979 |

|

SU788272A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1027815A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-03-07—Публикация

1984-08-15—Подача