Изобретение относится к цифровой измерительной и вычислительной технике и может быть использовано для преобразования аналоговых величин в цифровые.

Целью изобретения является повышение точности.

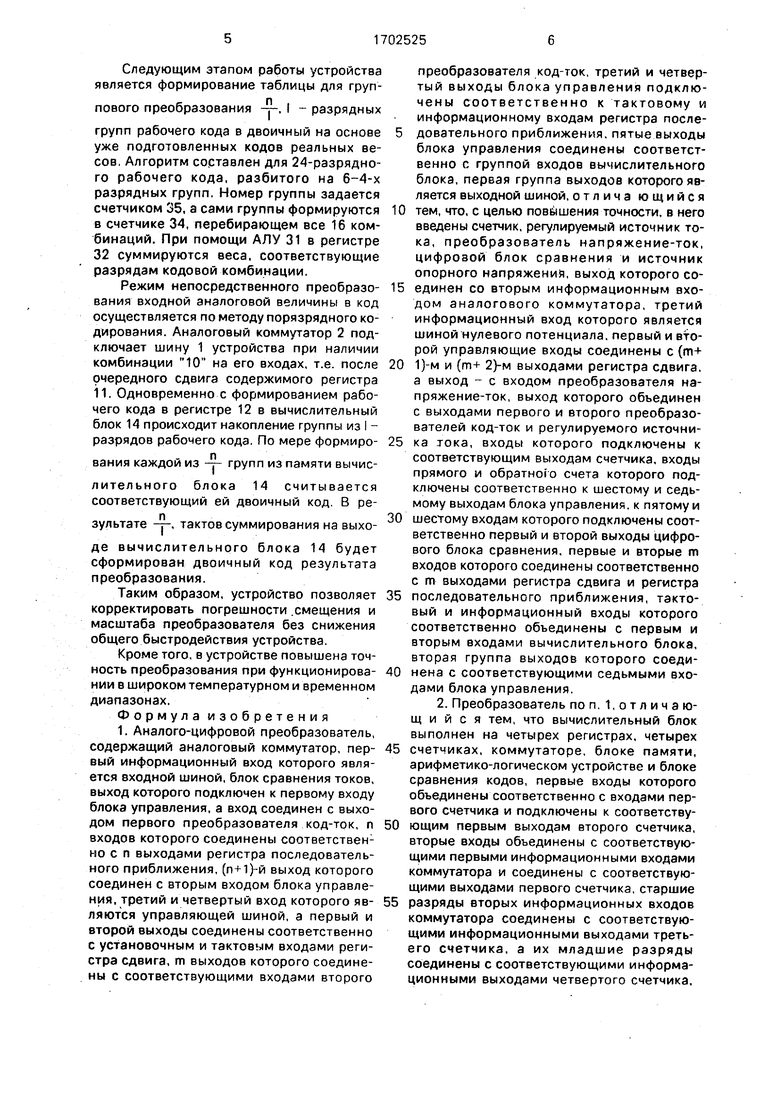

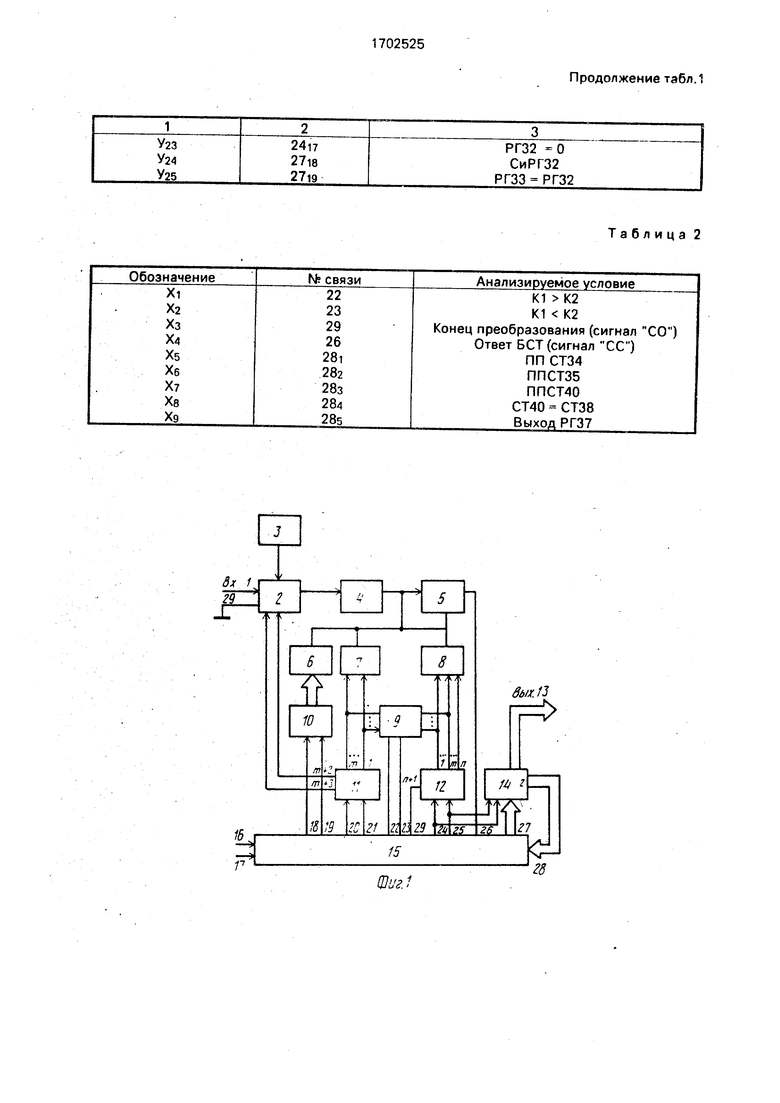

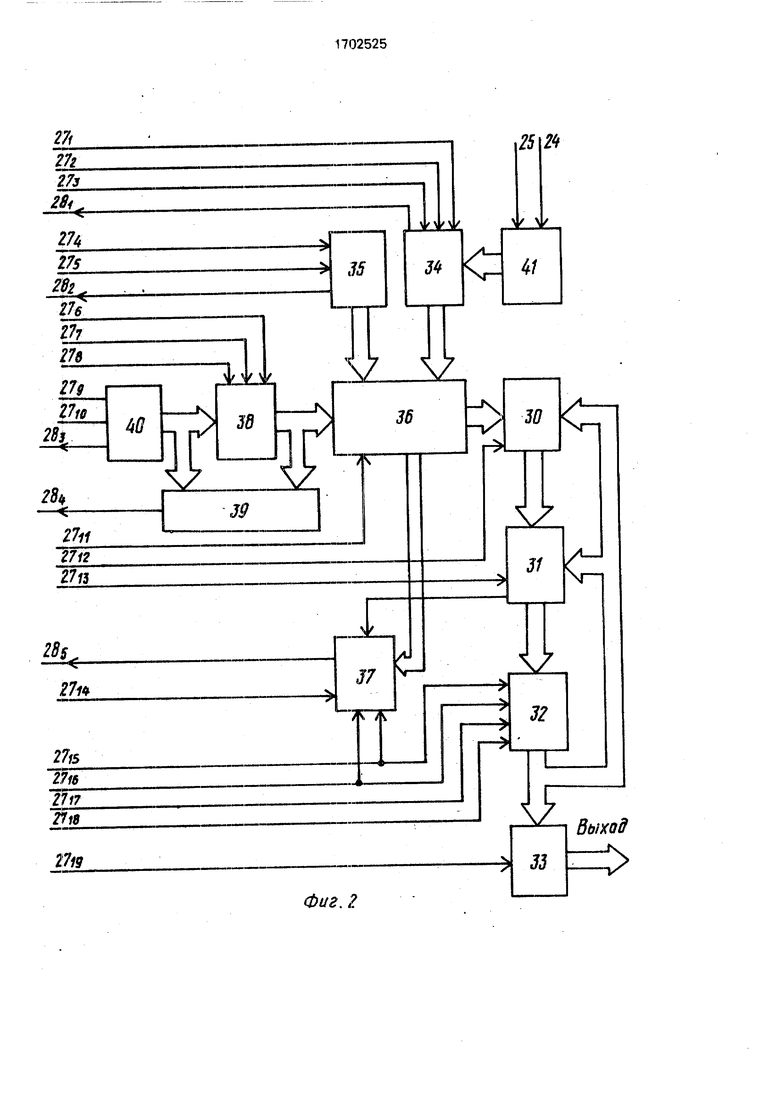

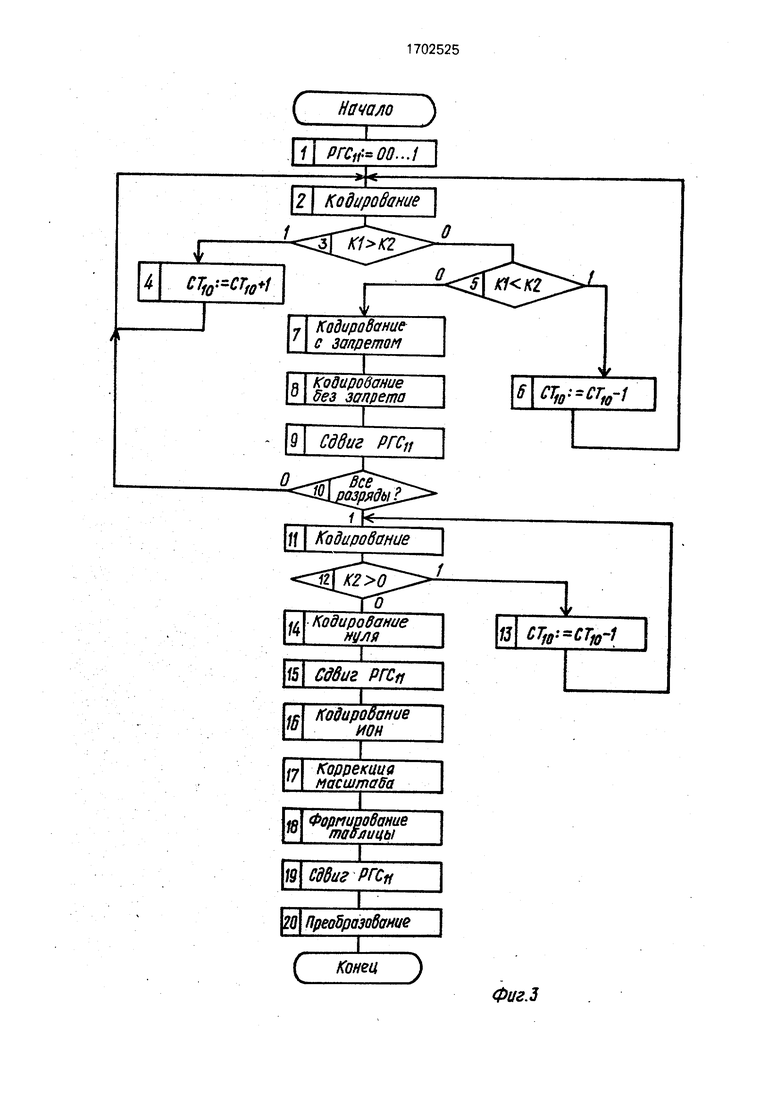

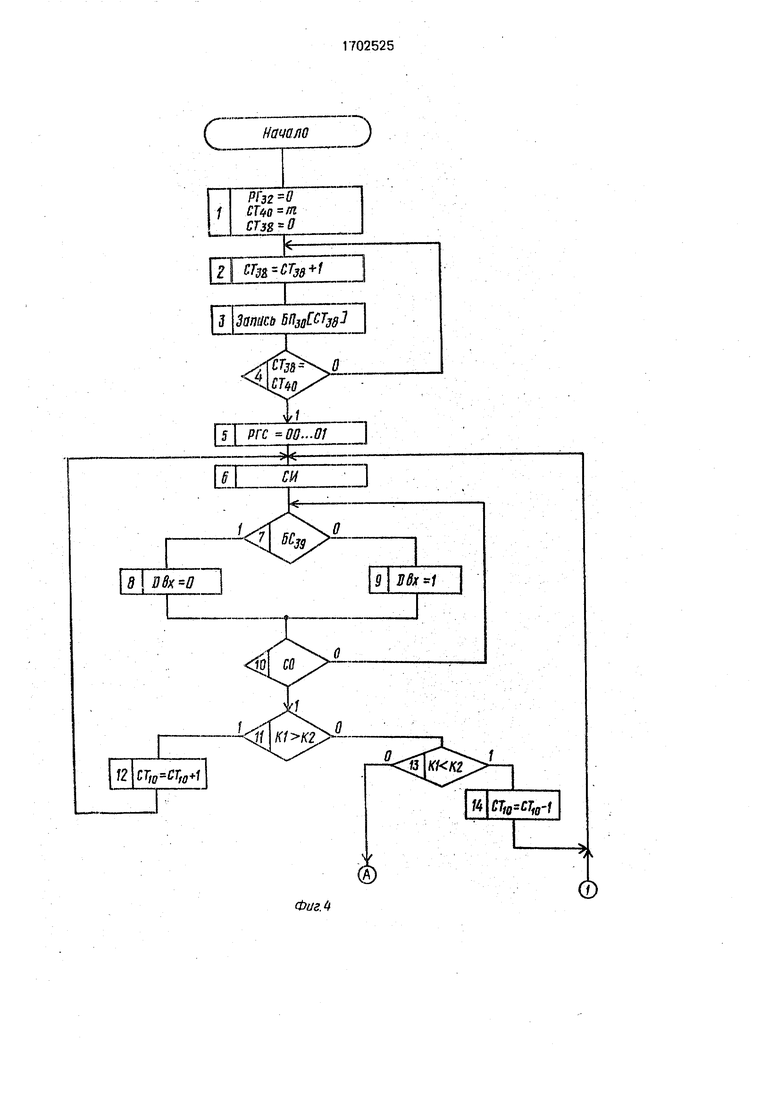

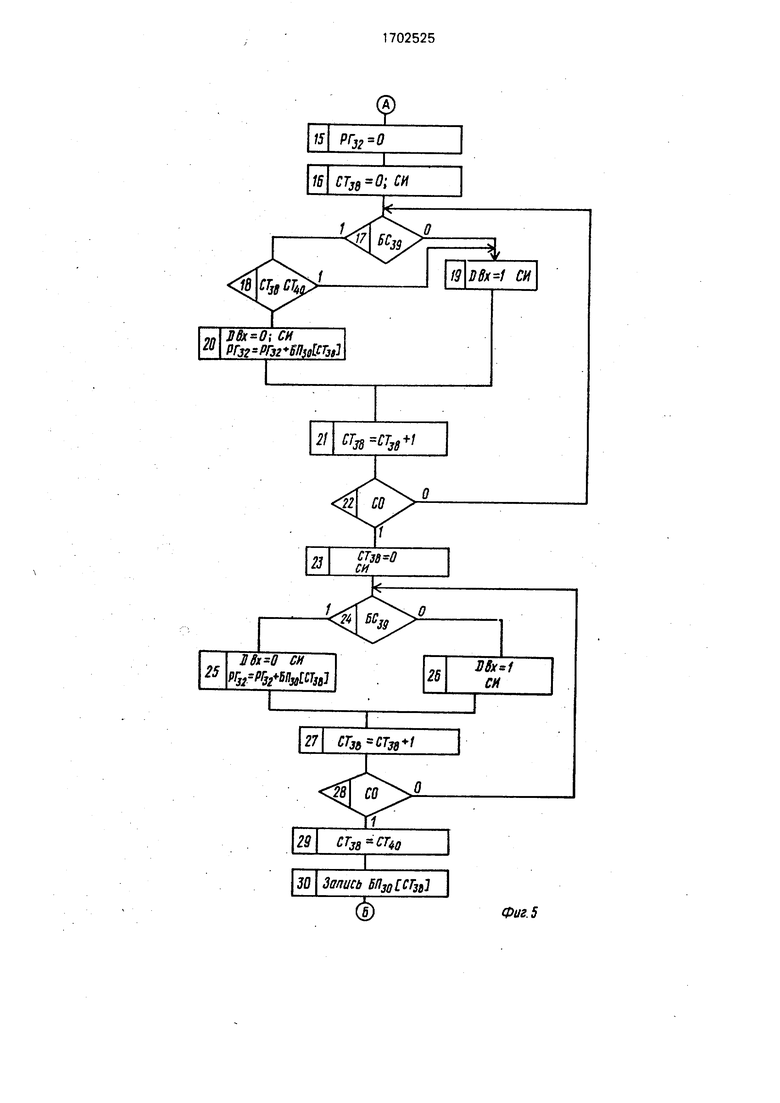

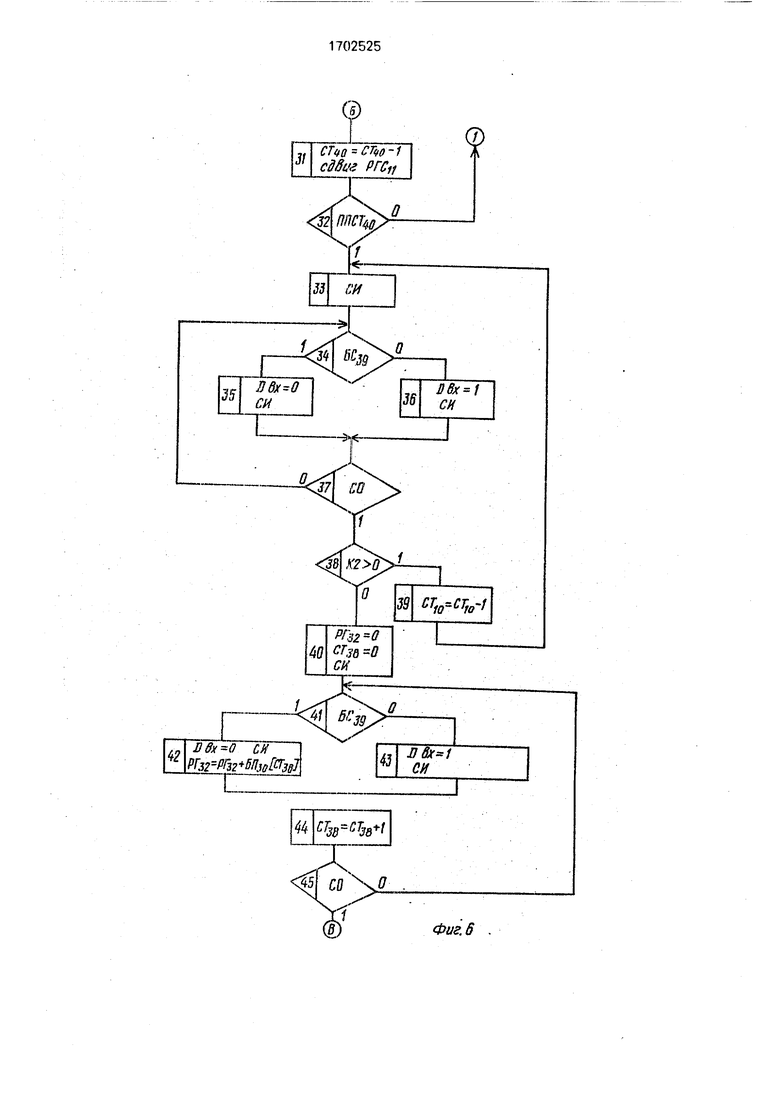

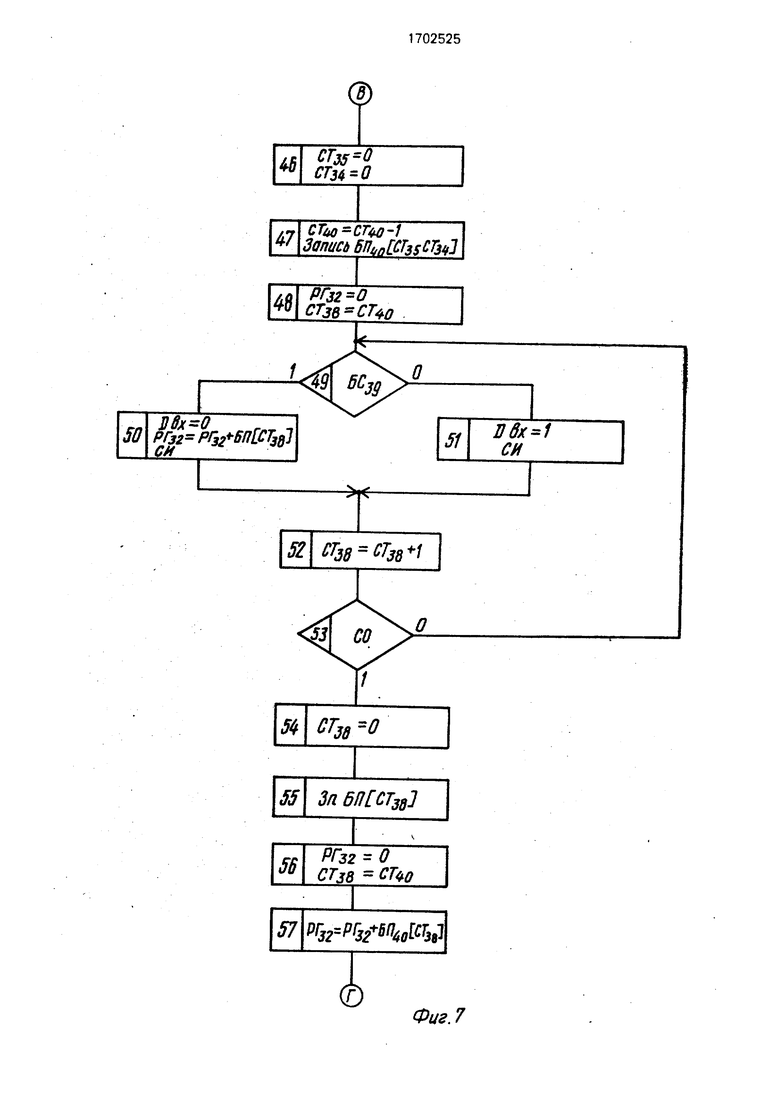

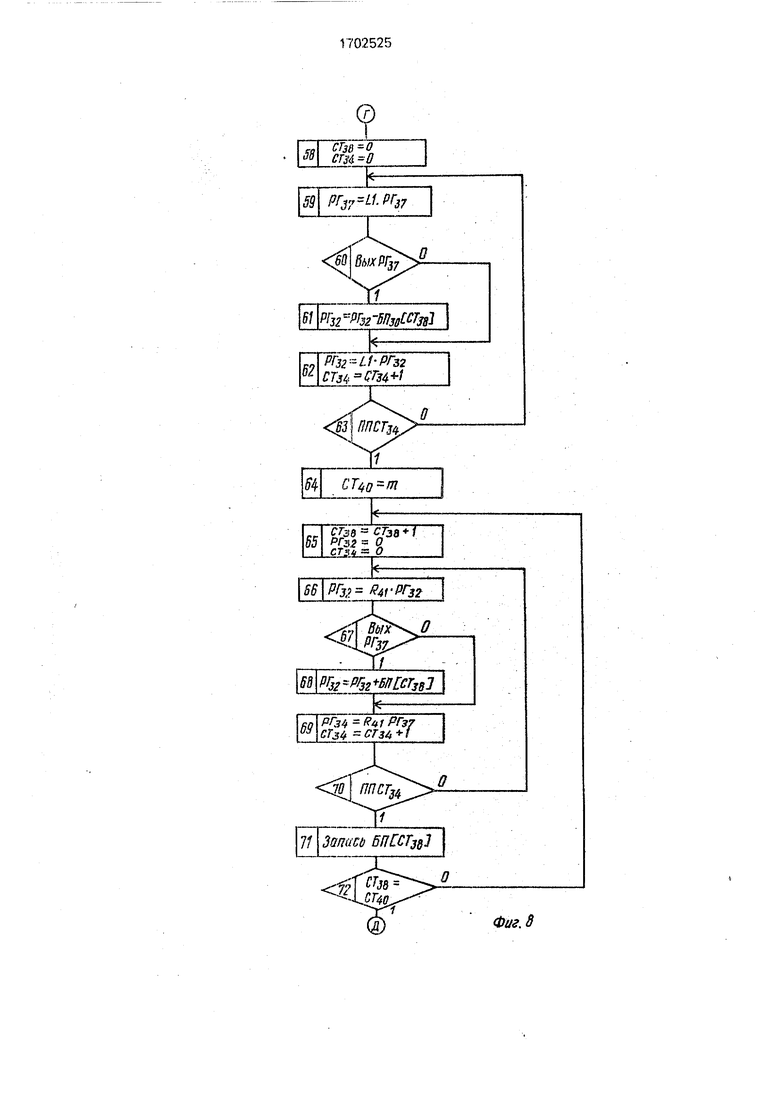

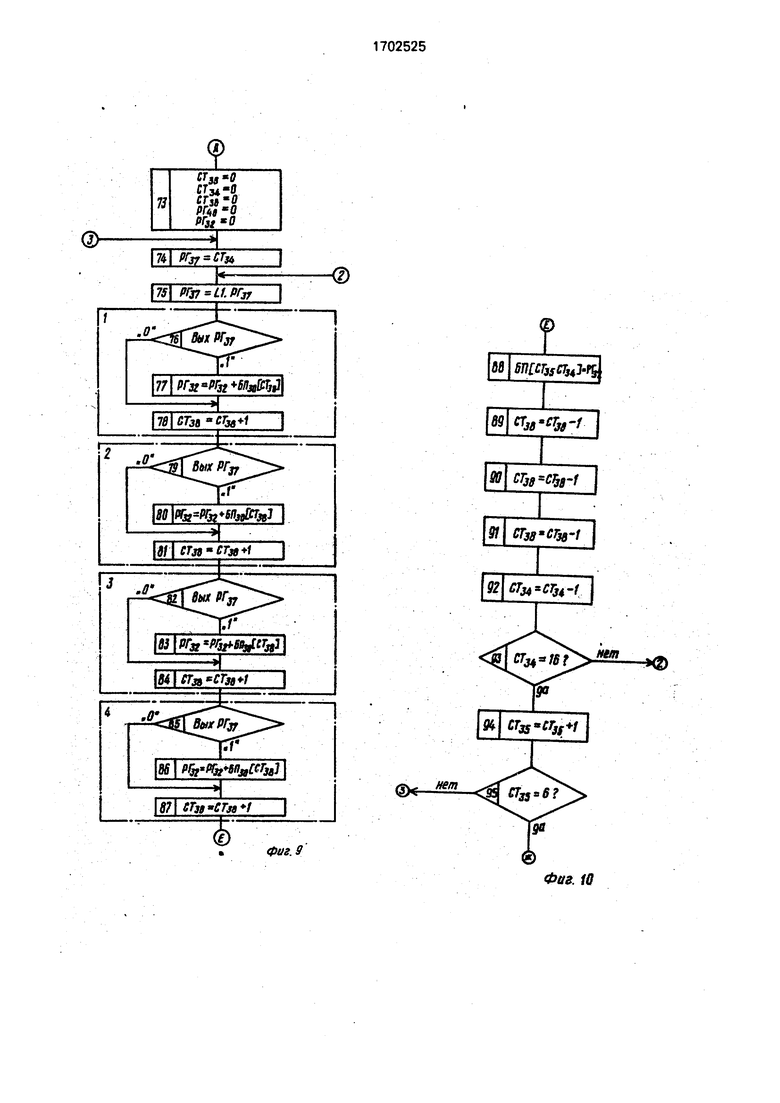

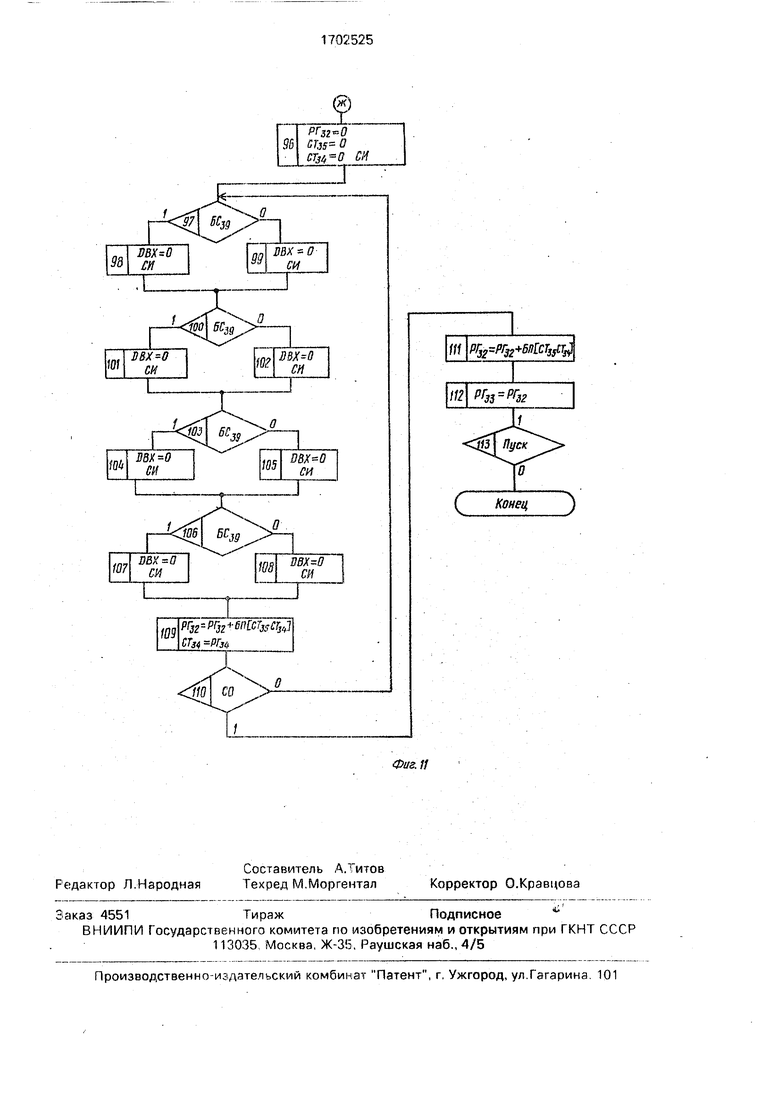

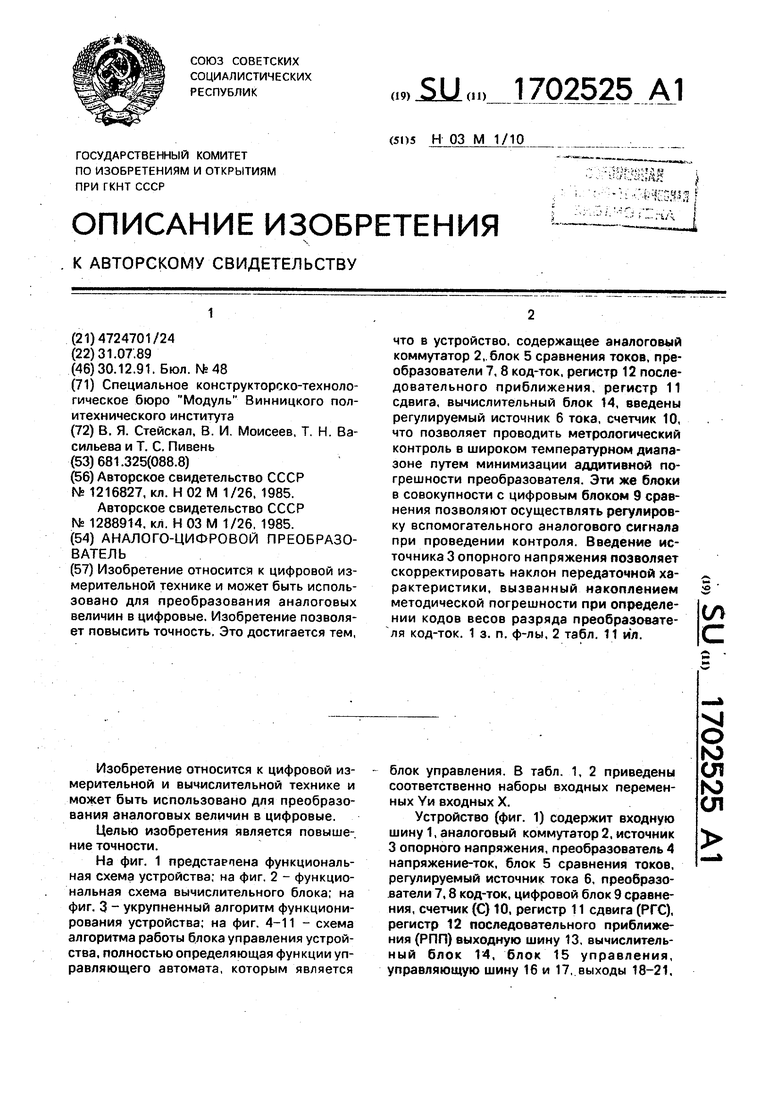

На фиг. 1 предстарпена функциональная схема устройства; на фиг 2 - функциональная схема вычислительного блока, на фиг. 3 - укрупненный алгоритм функционирования устройства, на фиг. 4-11 - схема алгоритма работы блока управления устройства, полностью определяющая функции управляющего автомата, которым является

блок управления. В табл 1, 2 приведены соответственно наборы входных переменных Уи входных X.

Устройство (фиг. 1) содержит входную шину 1, аналоговый коммутатор 2, источник 3 опорного напряжения, преобразователь 4 напряжение-ток, блок 5 сравнения токов, регулируемый источник тока 6, преобразователи 7,8 код-ток, цифровой блок 9 сравнения, счетчик (С) 10. регистр 11 сдвига (РГС), регистр 12 последовательного приближения (РПП) выходную шину 13. вычислительный блок 14, блок 15 управления, управляющую шину 16 и 17 выходы 18-21,

VI

О

ю ся ю ся

вход 22, 23. выходы 24. 25, вход 26, выход 27, входы 28, 29.

Вычислительный блок (фиг. 2) содержит блок 30 памяти, арифметико-логическое устройство (АЛУ) 31, регистры (РГ) 32 и 33, счетчики 34 и 35, коммутатор (К) 36. регистр (РГ) 37, счетчик (Ст) 38, блок 39 сравнения кодов, счетчик (СТ) 40, регистр (РГ) 41.

Устройство функционирует в двух режимах: самоповерки и непосредственно аналого-цифрового преобразования с коррекцией. Режим самоповерки состоит из четырех этапов контроля линейности, смещения нуля, масштаба и формирования таблицы. При контроле линейности производится определение кодов весов группы старших разрядов с 1 -го по m-й основного преобразователя 8 код-ток. Определение данных кодов производится аналогично прототипу путем двух кодирований ступенчато формируемой вспомогательной аналоговой величины. Однако установление данной вспомогательной величины происходит в два этапа. Выполнение алгоритма начинается с обнуления области блока 30, где будут записываться вычисленные коды весов старших разрядов преобразователями 8 с 1-го по m-й (вершина 1 ...4) фиг. 1.

Затем при помощи записи в регистр 11 происходит включение разряда преобразователем 7 для определения кода веса младшего (т-го) из корректируемых разрядов. При этом определяется требуемое соотношение между сигналами преобразователей 7, 8. Для этого производится кодирование установленной вспомогательной аналоговой величины (в 6...10 путем подачи на вход регистра 12 серии синхроимпульсов (СИ) и установки его D-входа в зависимости от ответов блока 5 на включение () либо включения (ДВХ-1) разрядов до появления сигнала конца преобразования СО.

При помощи блока 9 определяется факт включения корректируемого разряда преобразователя 8. Если включение разряда не произошло, т.е. кодовая m-разрядная комбинация К 1 на выходе регистра 11 больше кодовой комбинации К2 старших разрядов регистра 12, то при помощи регулируемого источника 6 и счетчика 10 производится увеличение вспомогательной аналоговой величины, либо происходит ее уменьшение, если произошло включение более старшего разряда (в 11...14). Таким образом, путем ряда последовательных иттераций. устанавливается требуемое соотношение между преобразователями 7, 8. Затем по результатам двух кодирований с запретом (в 16...22) и без (в 24...29) определяется код реального веса проверяемого разряда, который записывается в блок 30 по адресу, определяемому счетчиком 40,

На втором этапе самоповерки определяется погрешность смещения нуля преобразователя. Сдвиг содержимого регистра 11 после определения кодов весов всех разрядов преобразователя 8 приводит к появлению единицы в (т-Н)-м разряде регистра 11. При этом отключаются разряды

преобразователя 7, а комбинация 00 на управляющих входах аналогового коммутатора 2 соответствует подключению нулевой шины. Для правильного определения погрешности смещения необходимо исключить включение корректируемых разрядов, т.е. провести минимизацию аддитивной погрешности.

Минимизация данной погрешности в широком температурном диапазоне производится при помощи регулируемого источника б и счетчика 10 (вершины 33...39). Для этого перед кодированием смещения нуля преобразователя (вершины 41...45) произ- водится ряд последовательных иттераций, направленных на исключение появления при этом значащих единиц в группе корректируемых разрядов. После кодирования код смещения нуля записывается в ячейку блока 30, адресуемую через коммутатор 36 счетчиками 35 и 34, сохраняясь таким образом до следующего контроля.

На третьем этапе самоповерки

корректируется наклон передаточной характеристики преобразователя. Сдвиг содержимого регистра 11 устанавливает на управляющих входах аналогового коммутатора комбинацию 01, при которой

происходит подключение источника 3. Производится кодирование опорного источника 3, Результат записывается в блок 30.

Затем в регистр 32 переписывается код, соответствующий данному источнику

и хранящийся в блоке 30 и происходит вычисление масштабного коэффициента Км путем деления данного кода на результат кодирования. Деление осуществляется путем последовательных вычитаний и

сдвигов. Частное формируется в регистре 37 (в 58...63). Коррекция погрешности масштаба преобразователя производится путем умножения кодов корректируемых весов разрядов преобразователя 8 на

вычисленный масштабный коэффициент (в 64...72).

После выполнения трех этапов самоповерки в памяти вычислительного блока будут сформированы коды всех весов разрядов преобразователя.

Следующим этапом работы устройства является формирование таблицы для группового преобразования -р I - разрядных

групп рабочего кода в двоичный на основе уже подготовленных кодов реальных весов. Алгоритм составлен для 24-разрядного рабочего кода, разбитого на 6-4-х разрядных групп. Номер группы задается счетчиком 35, а сами группы формируются в счетчике 34. перебирающем все 16 комбинаций. При помощи АЛУ 31 в регистре 32 суммируются веса, соответствующие разрядам кодовой комбинации.

Режим непосредственного преобразования входной аналоговой величины в код осуществляется по методу порязрядного кодирования. Аналоговый коммутатор 2 подключает шину 1 устройства при наличии комбинации 10 на его входах, т.е. после очередного сдвига содержимого регистра 11. Одновременно с формированием рабочего кода в регистре 12 в вычислительный блок 14 происходит накопление группы из I - разрядов рабочего кода. По мере формиро- п

вания каждой из

групп из памяти вычислительного блока 14 считывается соответствующий ей двоичный код. В реп

зультате -т-, тактов суммирования на выходе вычислительного блока 14 будет сформирован двоичный код результата преобразования.

Таким образом, устройство позволяет корректировать погрешности смещения и масштаба преобразователя без снижения общего быстродействия устройства.

Кроме того, в устройстве повышена точность преобразования при функционировании в широком температурном и временном диапазонах.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий аналоговый коммутатор, первый информационный вход которого является входной шиной, блок сравнения токов, выход которого подключен к первому входу блока управления, а вход соединен с выходом первого преобразователя код-ток, п входов которого соединены соответствен1 но С п выходами регистра последовательного приближения, (п + 1)-й выход которого соединен с вторым входом блока управления, третий и четвертый вход которого являются управляющей шиной, а первый и второй выходы соединены соответственно с установочным и тактовчм входами регистра сдвига, m выходов которого соединены с соответствующими входами второго

преобразователя код-ток, третий и четвертый выходы блока управления подключены соответственно к тактовому и информационному входам регистра после- 5 довательного приближения, пятые выходы блока управления соединены соответственно с группой входов вычислительного блока, первая группа выходов которого является выходной шиной, отлича ющийся

0 тем, что, с целью повышения точности, в него введены счетчик, регулируемый источник тока, преобразователь напряжение-ток, цифровой блок сравнения и источник опорного напряжения, выход которого со5 единен со вторым информационным входом аналогового коммутатора, третий информационный вход которого является шиной нулевого потенциала, первый и второй управляющие входы соединены с (т+

0 1)-м и (т+ 2)-м выходами регистра сдвига, а выход - с входом преобразователя напряжение-ток, выход которого объединен с выходами первого и второго преобразователей код-ток и регулируемого источни5 ка тока, входы которого подключены к соответствующим выходам счетчика, входы прямого и обратного счета которого подключены соответственно к шестому и седьмому выходам блока управления, к пятому и

0 шестому входам которого подключены соответственно первый и второй выходы цифрового блока сравнения, первые и вторые m входов которого соединены соответственно с m выходами регистра сдвига и регистра

5 последовательного приближения, тактовый и информационный входы которого соответственно объединены с первым и вторым входами вычислительного блока, вторая группа выходов которого соеди0 нена с соответствующими седьмыми входами блока управления.

2. Преобразователь по п. 1. о т л и ч а ю- щ и и с я тем, что вычислительный блок выполнен на четырех регистрах, четырех

5 счетчиках, коммутаторе, блоке памяти, арифметико-логическом устройстве и блоке сравнения кодов, первые входы которого объединены соответственно с входами первого счетчика и подключены к соответству0 ющим первым выходам второго счетчика, вторые входы объединены с соответствующими первыми информационными входами коммутатора и соединены с соответствующими выходами первого счетчика, старшие

5 разряды вторых информационных входов коммутатора соединены с соответствующими информационными выходами третьего счетчика, а их младшие разряды соединены с соответствующими информационными выходами четвертого счетчика.

информационные входы которого соединены с соответствующими выходами первого регистра, первый и второй входы которого являются соответственно третьим и вторым входами блока, а первые выходы коммутатора подключены к соответствующим адресным входам блока памяти, информационные входы которого объединены соответственно с первыми входами арифметико-логического уст- ройства, информационными входами второго регистра и соединены с соответствующими выходами третьего регистра, информационные входы которого соединены с соответствующими информационными выходами арифметико-логического устройства, вторые входы которого соединены с соответствующими выходами блока памяти, выход переноса арифметико-логического устройства соединен с входом данных чет- вертого регистра, первый и второй входы управления режимом работы которого объединены соответственно с одноименными входами третьего регистра и являются соответственно первым и вторым входами труп- пы входов блока, первый, второй и третий управляющие входы четвертого счетчика.

входы обнуления и счета третьего счетчика, входы обнуления, записи и счета первого счетчика, входы записи и счета второго счетчика, адресный вход коммутатора, вход записи блока памяти, вход управления режимом арифметико-логического устройства, тактовый вход четвертого регистра, входы обнуления и тактовый вход третьего регистра, вход записи второго регистра являются соответственно третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым, пятнадцатым, шестнадцатым, семнадцатым входами группы входов блока, выходы второго регистра являются первой группой выходов блока, выходы переполнения четвертого и третьего счетчиков, второй выход второго счетчика, выход блока сравнения кодов и выход четвертого регистра являются соответственно первым, вторым, третьим, четвертым и пятым выходами второй группы выходов блока, информационные входы четвертого регистра соединены с соответствующими выходами коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1495993A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1667249A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Устройство цифро-аналогового преобразования | 1985 |

|

SU1312739A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

Изобретение относится к цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые. Изобретение позволяет повысить точность. Это достигается тем, что в устройство, содержащее аналоговый коммутатор 2, блок 5 сравнения токов, преобразователи 7. 8 код-ток, регистр 12 последовательного приближения, регистр 11 сдвига, вычислительный блок 14, введены регулируемый источник 6 тока, счетчик 10, что позволяет проводить метрологический контроль в широком температурном диапазоне путем минимизации аддитивной погрешности преобразователя. Эти же блоки в совокупности с цифровым блоком 9 сравнения позволяют осуществлять регулировку вспомогательного аналогового сигнала при проведении контроля. Введение источника 3 опорного напряжения позволяет скорректировать наклон передаточной характеристики, вызванный накоплением методической погрешности при определении кодов весов разряда преобразователя код-ток. 1 з. п. ф-лы, 2 табл. 11 ил. (/) С

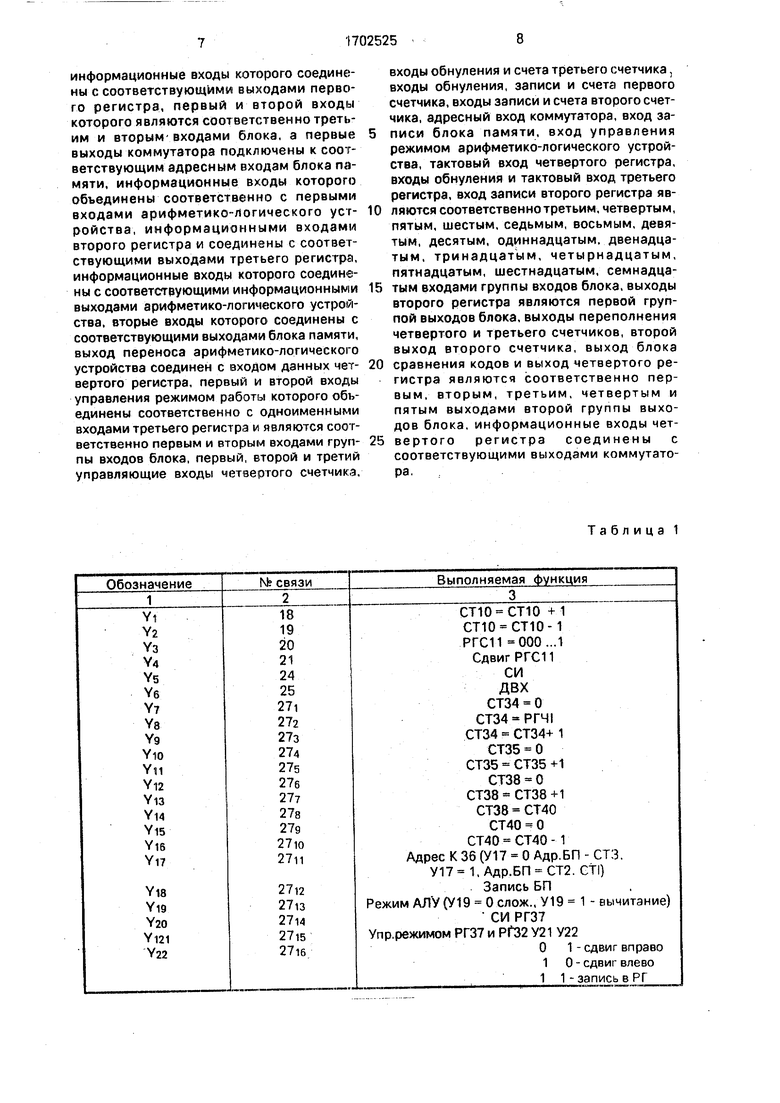

Таблица 1

Продолжение табл.1

Таблица 2

27i

27г

274

275

2b

276

276

v

27ig

Фиг. 2

Л

Л

i J

V V

35

J«

VV

с

Выход

С Конец )

Фиг.З

начало

г | CTn CT38+1

Запаси

Фиг А

)

/5

27 СГ36 СТ„+1

29

30 Запись

J/

CTtK

сдвиг РГСц

О .

Фиг. 6

45

47

СГйо-Cr ff-f

Запись бп,0 СТз$сЬ«

Ш

SO

РГм РГз2+6П СТз81 СИ

К

&38 СТ38 +1

54

СТзд -О

55

Зп

51

Явх 1 СИ

Фиг.7

W РГя РГз2-6ПзвСЯл1

и

РГзг И РГзг СТз4яСГн+1

Ј4

65

стзв стзл+Т ргзг о

СТ34 О

| | /д У /-ДГдг

6B l ra f%g+6ff&r g

J±

fi

РГ34 РыРГз7 СТзЬ СГз4+1

Фиг. 8

i

ffJ7 fo

±

J

.РГ„ |

фиг. 9

flfl 15Л СТиСТмЩ

SO

Wff Cbg-f

9 I crje Cfy-i

92 CT CT34-i

М СТ„ СГ„+1

Фаг. 10

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-12-30—Публикация

1989-07-31—Подача