Изобретение относится к вычислительной технике и может быть использовано в полупроводниковых запоминающих устройствах.

Цель изобретения - повышение быстродействия формирователя сигналов выборки.

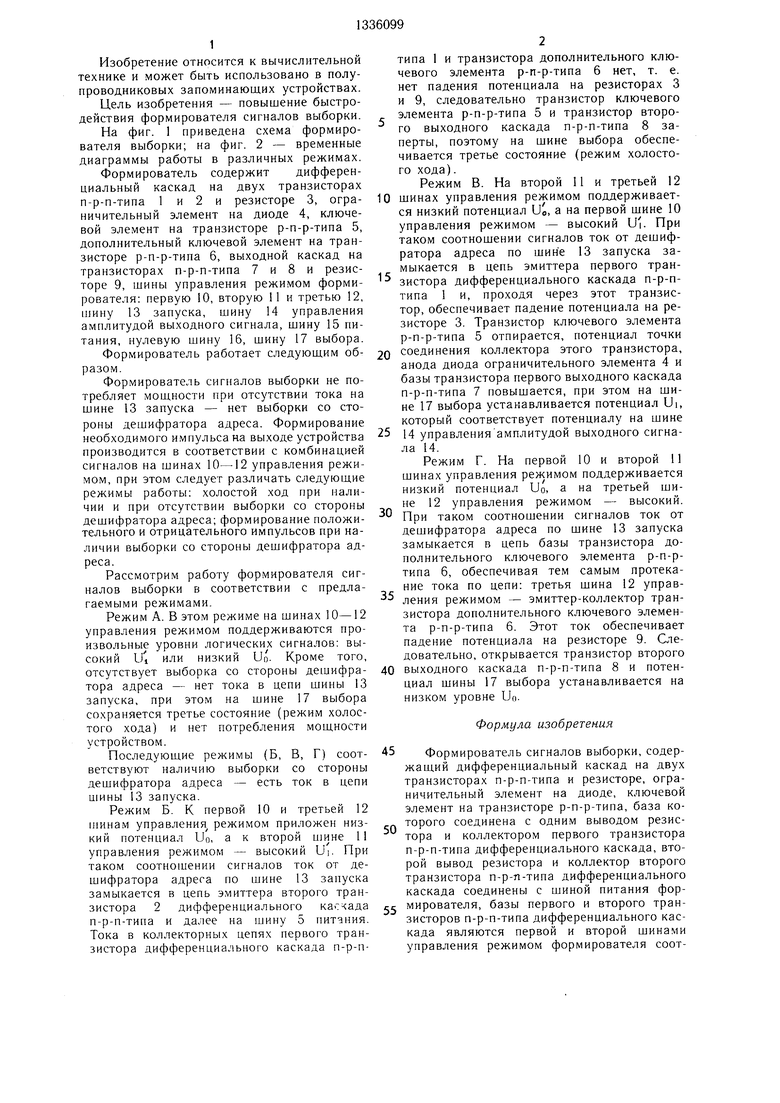

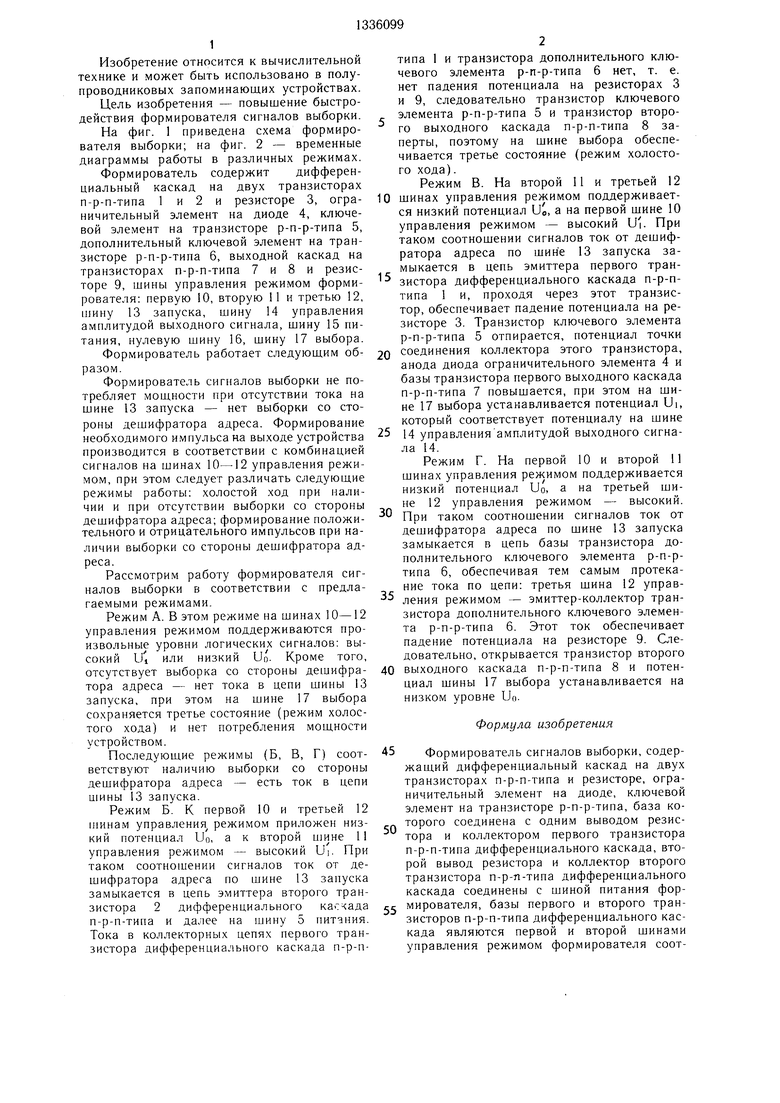

На фиг. 1 приведена схема формирователя выборки; на фиг. 2 - временные диаграммы работы в различных режимах.

Формирователь содержит дифференциальный каскад на двух транзисторах п-р-п-типа 1 и 2 и резисторе 3, ограничительный элемент на диоде 4, ключевой элемент на транзисторе р-п-р-типа 5, дополнительный ключевой элемент на транзисторе р-п-р-типа 6, выходной каскад на транзисторах п-р-п-типа 7 и 8 и резисторе 9, шины управления режимом формирователя: первую 10, вторую 11 и третью 12, шину 13 запуска, шину 14 управления амплитудой выходного сигнала, шину 15 питания, нулевую шину 16, шину 17 выбора.

Формирователь работает следуюш,им образом.

Формирователь сигналов выборки не потребляет мощности при отсутствии тока на шине 13 запуска - нет выборки со стороны дешифратора адреса. Формирование необходимого импульса на выходе устройства производится в соответствии с комбинацией сигналов на шинах 10-12 управления режимом, при этом следует различать следующие режимы работы: холостой ход при наличии и при отсутствии выборки со стороны дешифратора адреса; формирование положительного и отрицательного импульсов при наличии выборки со стороны дешифратора адреса.

Рассмотрим работу формирователя сигналов выборки в соответствии с предлагаемыми режимами.

Режим А. В этом режиме на шинах 10-12 управления режимом поддерживаются произвольные уровни логических сигналов: высокий Ui или низкий DO. Кроме того, отсутствует выборка со стороны дешифратора адреса - нет тока в цепи шины 13 запуска, при этом на шине 17 выбора сохраняется третье состояние (режим холостого хода) и нет потребления мощности устройством.

Последующие режимы (Б, В, Г) соответствуют наличию выборки со стороны дешифратора адреса - есть ток в цепи шины 13 запуска.

Режим Б. К первой 10 и третьей 12 пшнам управления режимом приложен низкий потенциал Uo, а к второй 11 управления режимом - высокий Ui. При таком соотношении сигналов ток от дешифратора адреса по шине 13 запуска замыкается в цепь эмиттера второго транзистора 2 дифференциального каскада п-р-п-типа и далее на шину 5 питания. Тока в коллекторных цепях первого транзистора дифференциального каскада п-р-п0

5

0

5

0

5

0

5

0

5

типа 1 и транзистора дополнительного ключевого элемента р-п-р-типа 6 нет, т. е. нет падения потенциала на резисторах 3 и 9, следовательно транзистор ключевого элемента р-п-р-типа 5 и транзистор второго выходного каскада п-р-п-типа 8 заперты, поэтому на шине выбора обеспечивается третье состояние (режим холостого хода).

Режим В. На второй 11 и третьей 12 шинах управления режимом поддерживается низкий потенциал Uo, а на первой шине 10 управления режимом - высокий IJ. При таком соотношении сигналов ток от дешифратора адреса по шине 13 запуска замыкается в цепь эмиттера первого транзистора дифференциального каскада п-р-п- типа 1 и, проходя через этот транзистор, обеспечивает падение потенциала на резисторе 3. Транзистор ключевого элемента р-п-р-типа 5 отпирается, потенциал точки соединения коллектора этого транзистора, анода диода ограничительного элемента 4 и базы транзистора первого выходного каскада п-р-п-типа 7 повышается, при этом на шине 17 выбора устанавливается потенциал Ui, который соответствует потенциалу на шине 14 управления амплитудой выходного сигнала 14.

Режим Г. На первой 10 и второй 11 шинах управления режимом поддерживается низкий потенциал Uo, а на третьей шине 12 управления режимом - высокий. При таком соотношении сигналов ток от дешифратора адреса по шине 13 запуска замыкается в цепь базы транзистора дополнительного ключевого элемента р-п-р- типа 6, обеспечивая тем самым протекание тока по цепи: третья шина 12 управления режимом - эмиттер-коллектор транзистора дополнительного ключевого элемента р-п-р-типа 6. Этот ток обеспечивает падение потенциала на резисторе 9. Следовательно, открывается транзистор второго выходного каскада п-р-п-типа 8 и потенциал шины 17 выбора устанавливается на низком уровне UQ.

Формула изобретения

Формирователь сигналов выборки, содержащий дифференциальный каскад на двух транзисторах п-р-п-типа и резисторе, ограничительный элемент на диоде, ключевой элемент на транзисторе р-п-р-типа, база которого соединена с одним выводом резистора и коллектором первого транзистора п-р-п-типа дифференциального каскада, второй вывод резистора и коллектор второго транзистора п-р-п-типа дифференциального каскада соединены с шиной питания формирователя, базы первого и второго транзисторов п-р-п-типа дифференциального каскада являются первой и второй шинами управления режимом формирователя соответственно, эмиттеры первого и второго транзисторов п-р-п-типа дифференциального каскада объединены и являются шиной запуска формирователя, эмиттер транзистора р-п-р-типа ключевого элемента и коллектора транзистора п-р-п-типа первого выходного каскада соединены с шиной питания формирователя, а коллектор - с базой транзистора п-р-п-типа первого выходного каскада и анодом диода ограничительного элемента, катод которого является шиной управления амплитудой выходного сигнала формирователя, отличающийся тем, что, с целью повышения быстродействия, он содержит дополнительный ключевой элемент на транзисторе р-п-р-типа и второй

Що

выходной каскад на резисторе и транзисторе п-р-п-типа, эмиттер которого и один вывод резистора подключены к нулевой шине формирователя, второй вывод резистора

и база транзистора п-р-п-типа второго выходного каскада подключены к коллектору транзистора р-п-р-типа дополнительного ключевого элемента, эмиттер которого является третьей шиной управления режимом

,, формирователя, а база соединена с эмиттерами первого и второго транзисторов п-р-п- типа дифференциального каскада, коллектор транзистора п-р-п-типа второго выходного каскада соединен с эмиттером транзистора п-р-п-типа первого выходного каскада и является шиной выборки формирователя.

Редактор Н. Бобкова Заказ 3809/49

Составитель В. Гордонова

Техред И. ВересКорректор А. Обручар

Тираж 589Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| ФОРМИРОВАТЕЛЬ ТОКА ВЫБОРКИ | 1973 |

|

SU377869A1 |

| Формирователь тока выборки дляблОКОВ пАМяТи | 1979 |

|

SU842954A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

Изобретение относится к вычислительной технике и может быть использовано в полупроводниковых запоминающих устройствах. Целью изобретения является повышение быстродействия формирователя сигналов выборки. Устройство содержит лиф- ференциальный каскад на двух транзисторах п-р-п типа 1 и 2 и резисторе 3, ограничительный элемент на диоде 4, ключевой элемент на транзисторе р-п-р-типа 5, дополнительный ключевой элемент на транзисторе р-п-р-типа 6, выходной каскад на транзисторах п-р-п типа 7 и 8 и резисторе 9, шины управления режимом формирователя; первую 10, вторую 11 и третью 12, шину запуска 13, шину управления амплитудой выходного сигнала 14, шину питания 15, нулевую шину 16, шину выбора 17. Формирователь сигналов выборки не потребляет мощности при отсутствии тока на шине 13 запуска, нет выборки со стороны дешифратора адреса. Формирование необходимого импульса на выходе устройства производится в соответствии с комбинацией сигналов на шинах 10-12 управления режимом, при этом следует различать следуюш,ие режимы работы: холостой ход при наличии и при отсутствии выборки со стороны дешифратора адреса, формирование положительного и отрицательного импульсов при наличии выборки со стороны дешифратора адреса. 2 ил. i (Л 00 оо О5 О ;о ;о

| Валиев К | |||

| А., Орликовский А | |||

| А | |||

| Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах | |||

| - М.: Советское радио, 1979, с | |||

| Крутильный аппарат | 1922 |

|

SU233A1 |

| Электроника, № 9, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

Авторы

Даты

1987-09-07—Публикация

1985-07-08—Подача