Изобретение относится к вычислительной технике, а именно к запоминающим устройствам на биполярных транзисторах.

Известны запоминающие устройства, содержащие в качестве накопителя информации матрицу элементов памяти, каждый из которых состоит из двух транзисторов с перекрестно связанными базовыми и коллекторными выводами.

Недостатком указанных устройств является их низкая надежность функционирования, вызванная наличием возможности рассогласования уровней напряжений в элементах памяти и уровня опорного напряжения считывания при разбросе параметров элементов памяти.

Наиболее близким к предлагаемому является запоминающее устройство, содержащее элементы памяти, каждый из которых состоит из двух ключевых транзисторов, двух нагрузочных резисторов, первого и второго ограничительных диодов, катоды которых соединены с первыми выводами первого и второго нагрузочных резисторов соответственно, базами второго и первого ключевых транзисторов соответственно и коллекторами первого и второго ключевых транзисторов соответственно, и коллекторами первого и второго ключевых транзисторов соответственно первые эмиттеры которых объединены и являются выво- домпитания элемента памяти, анод первого ограничительного диода является входом выборки элемента памяти и соединен с анодом второго ограничительного диода и вторыми выводами первого и второго нагрузочных резисторов, вторые эмиттеры первых и вторых ключевых транзисторов всех элементов памяти подключены к первой и второй разрядным шинам устройства соответственно, блок компенсации параметров, состоящий из двух ключевых транзисторов, двух нагрузочных резисторов, компенсирующего резистора и первого ограничительного диода, анод которого является входом выборки устройства и соединен с первым выводом первого нагрузочного резистора, второй вывод которого соединен с первым выводом компенсирующего резистора и первым выводом второго нагрузочного резистора, второй вывод которого соединен с катодом первого ограничительного диода и коллекторами первого и второго ключевых транзисторов, эмиттеры которых соответственно подключены к первой и второй разрядным шинам устройства, а базы соединены с вторым выводом компенсирующего резистора.

Функциональная надежность устройства-прототипа достигается за счет эквивалентности блока компенсации параметров и элементов памяти, что позволяет получить высокую степень соответствия уровня опорного напряжения на базах ключевых транзисторов блока компенсации параметров уровням логических напряжений на базах ключевых транзисторов в выбранном элементе памяти. Конструкция блока компенсации параметров такова, что взаимное

расположение уровня опорного напряжения и логических напряжений в элементе памяти стабильно в условиях различных дестабилизирующих воздействий в установившемся режиме считывания, однако

нарушается при переходном процессе во время смены элемента памяти. Это приводит к снижению быстродействия особенно в случае, когда переключение ранее выбранного элемента памяти в режиме хранения

происходит быстрее, чем процесс выборки нового элемента памяти. При этом в течение достаточно длительного периода времени уровень на базах ключевых транзисторов блока компенсации параметров, сохраняя

свое положение, установившееся в статическом режиме, оказывается выше логических уровней в прежде выбран ном элементе памяти, уже перешедшем в режим хранения, и в еще не выбранном подлежащем считыванию элементе памяти. На разрядных шинах запоминающего устройства в течение этого периода устанавливаются одинаковые уровни напряжений, формируемые ключевыми транзисторами блока компенсации

параметров, что и приводит к увеличению задержки появления нового информационного сигнала.

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что в запоминающем устройстве, содержащем элементы памяти, каждый из которых состоит из двух ключевых транзисторов, двух нагрузочных резисторов, первого и второго

ограничительных диодов, катоды которых соединены с первыми выводами первого и второго нагрузочных резисторов соответственно, базами второго и первого ключевых транзисторов соответственно и коллекторами первого и второго ключевых транзисторов соответственно, первые эмиттеры которых объединены и являются выводом питания элемента памяти, анод первого ограничительного диода является входом выборки элемента памяти и соединен с анодом второго ограничительного диода и вторыми выводами первого и второго нагрузочных резисторов, вторые эмиттеры первых и вторых ключевых транзисторов всех элементов

памяти подключены к первой и второй разрядным шинам устройства соответственно, блок компенсации параметров, состоящий из двух ключевых транзисторов, двух нагрузочных резисторов, компенсирующего резистора, первого ограничительного диода, анод которого является входом выборки устройства и соединен с первым выводом первого нагрузочного резистора, второй вывод которого соединен с первым выводом компенсирующего резистора и первым выво- дом второго нагрузочного резистора, второй вывод которого соединен с катодом первого ограничительного диода и коллектором первого ключевого транзистора, эмиттер которого подключен к первой раз- рядной шине устройства, а база соединена с вторым выводом компенсирующего резистора и базой второго ключевого транзистора, эмиттер которого подключен к второй разрядной шине устройства, в блок компен- сации разброса параметров введены третий нагрузочный резистор и второй ограничительный диод, анод которого соединен с анодом первого ограничительного диода, а катод - с коллектором второго ключевого тра нзистора и первым выводом третьего нагрузочного резистора, второй вывод которого соединен с первым выводом компенсирующего резистора.

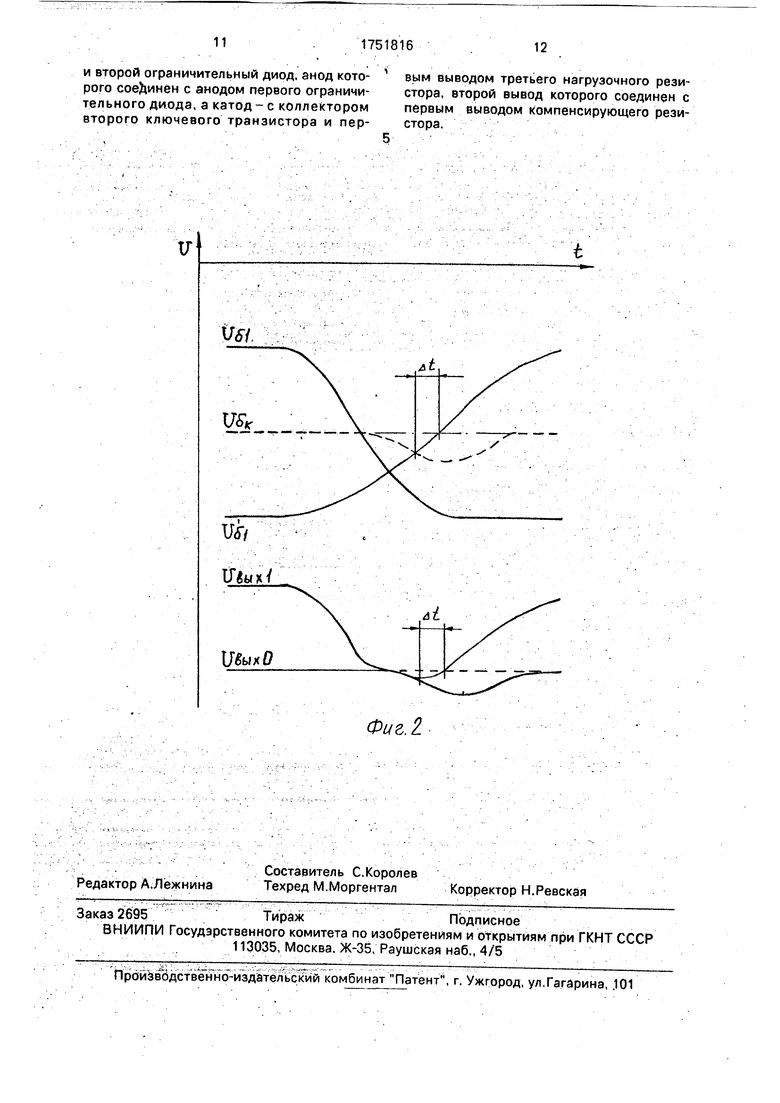

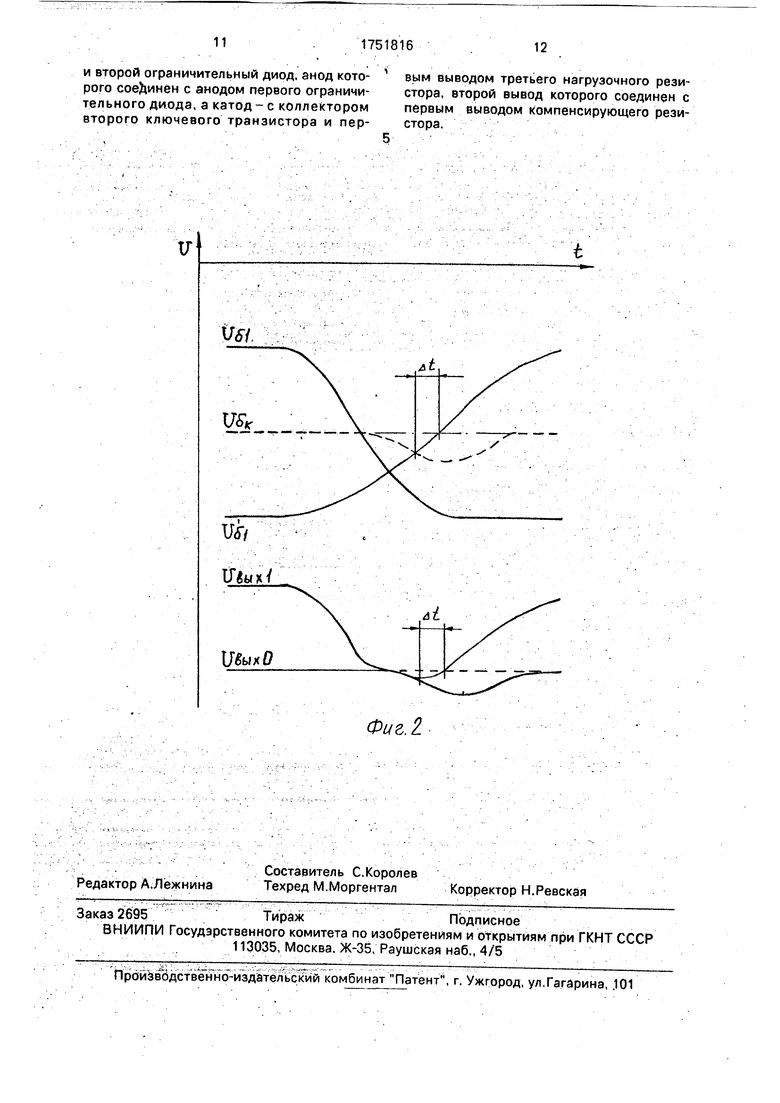

На фиг.1 изображена принципиальная электрическая схема запоминающего устройства; на фиг.2 - временные диаграммы логических напряжений в элементах памяти и блоках компенсации параметров при смене элементов памяти в предлагаемом уст- ройстве и устройстве-прототипе.

Запоминающее устройство содержит элементы 1 памяти, каждый из которых состоит из двух ключевых транзисторов 2 и 3, двух нагрузочных резисторов 4 и 5 и первого и второго ограничительных диодов б и 7, катоды которых соединены с первыми выводами первого и второго нагрузочных резисторов 4 и 5 соответственно, базами второго и первого ключевых транзисторов 3 и 2 со- ответственно и коллекторами первого и второго ключевых транзисторов 2 и 3 соответственно, первые эмиттеры которых объединены и являются выводом 8 питания элемента 1 памяти. Анод первого ограничи- тельного диода 6 является входом 9 выборки элемента 1 памяти и соединен с анодом второго ограничительного диода 7 и вторыми выводами первого и второго нагрузочных резисторов 4 и 5. Вторые эмиттеры первых и вторых ключевых транзисторов 2 и 3 всех элементов 1 памяти подключены к первой и второй разрядным шинам 10 и 11 устройства соответственно, В состав устройства входит также блок 12 компенсации

параметров, состоящий из двух ключевых транзисторов 13 и 14, трех нагрузочных резисторов 15, 16 и 17, компенсирующего резистора 18 и двух ограничительных диодов 19 и 20, аноды которых соединены с первым выводом первого нагрузочного резистора 15 и являются входом 21 выборки устройства. Второй вывод нагрузочного резистора

15соединен с первым выводом компенсирующего резистора 18 и первыми выводами второго и третьего нагрузочных резисторов

16и 17, вторые выводы которых соединены с катодами первого и второго ограничительных диодов 19 и 20 соответственно и коллекторами первого и второго ключевых транзисторов 13 и 14. Эмиттеры последних подключены к первой и второй разрядным шинам 10 и 11 устройства соответственно, а базы соединены с вторым выводом компенсирующего резистора 18.

Запоминающее устройство работает следующим образом.

Каждый элемент 1 памяти представляет собой RS-триггер ЭСЛ-типа, В режиме хранения информации состояния триггеров- элементов 1 памяти - поддерживаются за счет протекания в них токов, поступающих в элементы 1 памяти через выводы 8 питания. В режиме записи информации выборка нужного элемента 1 памяти осуществляется посредством повышения потенциала на соответствующем входе 9 выборки. Для установки выбранного элемента 1 памяти в требуемое состояние в одну из разрядных шин 10 и 11 включается ток записи. Ток записи включается в ту разрядную шину 10 или 11, к которой подключен второй эмиттер ключевого транзистора 2 или 3 выбранного элемента 1 памяти, у которого в соответствии с поступающей информацией в результате записи на базе должен установиться высокий потенциал. Уровень напряжения на входе 21 выборки устройства равен напряжению на входах 9 выборки невыбранных элементов 1 памяти. Этот уровень в режиме записи информации находится ниже нижнего уровня напряжения на базах ключевых транзисторов 2 и 3 выбранного элемента 1 памяти. Таким образом, среди транзисторов 2, 3, 13 и 14, эмиттеры которых подключены к разрядной шине 10 или 11с включенным тохсм записи, самый высокий потенциал на базе имеет транзистор 2 или 3 выбранного элемента 1 памяти при любом его состоянии и, следовательно, ток записи ответвляемся в эмиттер этого транзистора 2 или 3, что приводит к установке выбранного элемента 1 памяти в требуемое состояние. В режиме считывания информации выборка элемента 1 памяти осуществляется так же, как в режиме записи. На входе 21 выборки устройства устанавливается напряжение, равное напряжению на входе 9 выборки выбранного элемента 1 памяти. В обе разрядные шины 10 и 11 включаются токи считывания. Ток считывания, включенный в узел, соответствующий второму эмиттеру транзистора 2 или 3 выбранного элемента 1 памяти с низким уровнем напряжения на базе, протекает в эмиттере соответствующего ключевого транзистора 13 или 14 блока 12 компенсации параметров, так как в момент включения тока считывания этот транзистор имеет самый высокий базовый потенциал. Ток считывания, включенный в узел, соответствующий транзистору 2 или 3 выбранного элемента 1. памяти с высоким базовым потенциалом, по завершении формирования уровня напряжения на базах транзисторов 13 и 14 полностью протекает в выбранный элемент 1 памяти, В результате описанного распределения токов считывания на разрядных шинах 10 и 11 формируются логические напряжения в соответствии с состоянием выбранного элемента 1 памяти. На шине 10 или 11, где ток считывания протекает в транзистор 13 или 14 блока 12 компенсации параметров, формируется напряжение низкого логического уровня, равное напряжению на базе транзисторов 13 и 14 минус напряжение между базой и эмиттером соответствующего транзистора 13 или 14, а на другой разрядной шине 10 или 11 - напряжение высокого логического уровня, равное высокому базовому уровню в выбранном элементе 1 памяти минус напряжение между базой и эмиттером соответствующего транзистора 2 или 3, . Блок 12 компенсации параметров выполняет две функции: формирование информационной разности потенциалов на разрядных шинах 10 и 11 и предотвращение включения хотя бы части тока считывания в закрытый транзистор 2 или 3 выбранного элемента 1 памяти, которое может привести к самопроизвольному его опрокидыванию. При формировании базового напряжения транзисторов 13 и 14 ток считывания, включенный в блок 12 компенсации параметров, разделяется на базовый и коллекторный токи проводящего его транзистора 13 или 14, Если это транзистор 13, коллекторный ток протекает в цепи из последовательных резисторов 15 и 16 и параллельно подключенного к ним диода 19, а если транзистор 14 - в цепи из резисторов 15 и 17 и диода 20. Базовый ток транзисторов 13 и 14 при любой считываемой информации протекает в общий узел резисторов 15-18 через резистор 18. Такое распределение токов происходит вследствие того, что в условиях обычного для транзисторов 13 и 14 нормального активного режима, при котором коллекторный ток по величине превосходит базовый, открыт только тот из диодов 19 и 20, который подключен к коллектору транзистора 13 или 14, про водящего то к считывания, другой диод 19 или 20 при этом закрыт, так как напряжение на нем, формируемое делителем на резисторах 15, 16 и 17, равно части необходимого для отпирания напряжения.

На основании приведенного описания работы запоминающего устройства для рассматриваемых уровней напряжений получе- ны следующие выражения:

Uei Ug - R4 1б ;(1)

Ueo Ug - идэп,(2)

(Ufl5K-R,5-f6)(Ri5+Rie)l6,(3)

где Uei и Ueo - соответственно высокий и низкий уровни на базах транзисторов 2 и 3 выбранного элемента 1 памяти;

Ug - напряжение на входе 9 выборки элемента 1 памяти, выбранного для считывания;

R4 - номинальное сопротивление нагрузочных резисторов 4 и 5 элементов 1 памяти;

- номинальное сопротивление первого нагрузочного резистора 15 блока 12 компенсации параметров;

Rie - номинальное сопротивление второго и третьего нагрузочных резисторов 16 и 17 блока 12;

RIB - номинальное сопротивление компенсирующего резистора 18;

1б - базовый ток открытых транзисторов 2 и 3 выбранного элемента 1 памяти и тран- зисторов 13 и 14 блока 12 компенсации параметров;

Удэп и ЦЦБК - соответственно напряжения на открытом диоде 6 или 7 выбранного элемента 1 памяти и открытом диоде 19 или 20 блока 12 компенсации параметров;

Ыбк - напряжение на базах транзисторов 13 и 14 блока 12 компенсации параметров:

Uai - напряжение на входе 21 выборки устройства, в режиме считывания информации .

Наиболее оптимальное выполнение обеих функций блоками 12 компенсации параметров достигается, когда базовое напря- жение транзисторов 13 и 14 - Убк - занимает среднее положение между высоким и низким уровнями напряжений в выбранном элементе 1 памяти. Для обеспечения такого соотношения уровней достаточно зквивалентности транзисторов 2, 3, 13 и 14 по электрическим параметрам, эквивалентности диодов 6, 7 и 19, 20, равенства номинального сопротивления резисторов 15, 16 и 17 половине номинального сопротивле- ния резисторов 4 и 5 и равенства номинального сопротивления резистора 18 четверти номинального сопротивления резисторов 4 и 5. Данное утверждение легко проверить, подставив в выражения (1), (2) и (3) указан- ные соотношения сопротивлений. Так как , , а идБК 11дэп.

Кбк U9 -(Удал -R4 у ) -1 R4 «в , (4)

полусумма высокого и низкого базовых напряжений в выбранном элементе 1 памяти

Urf-i

Ug - ( УДЭП + R4 16 ) V4 . (

Сопоставив выражения (5) и (4) после приведения подобных членов, легко видеть, что их правые части тождественны.

Запоминающее устройство допускает смену элементов 1 памяти в режиме считывания. При этом после того, как напряжение на преждевыбранном входе 9 опустится до такой степени, что высокий базовый уровень напряжения в преждевыбранном эле- менте 1 памяти сравняется с уровнем напряжения на базах транзисторов 13 и 14, ток считывания, ранее полностью протекавший в элементе 1 памяти, начинает ответвляться в блок 12. В результате появления дополнительного тока в резисторе 15 снижается уровень базового напряжения транзисторов 13 и 14. Минимальный уровень этого напряжения достигается, когда в блоке 12 протекают оба тока считывания.

ибкмин U9 - (ЦДБК - 2R15 б)

2R15

2R15+R16

- 2 ( Rl5 + R18 ) б .(6)

Подставив в выражение (6) принятые соотношения номинальных сопротивлений резисторов, легко установить, что ибкмин смещен относительно номинального значения Кб на величину одной шестой от логи- ческого перепада в выбранном элементе 1 памяти. Опускание базового уровня транзисторов 13 и 14 при смене элементов 1 памяти приводит к более раннему пересечению этого уровня.повышающимся высоким базо- вым уровнем элемента 1 памяти (фиг.2). Это ускоряет процесс формирования информационной разности потенциалов на разрядных шинах 10 и 11 устройства и,

следовательно, позволяет уменьшить время задержки выборки и сократить продолжительность пребывания запоминающего устройства в процессе смены адреса, когда на его разрядных шинах 10 и 11 устанавливаются одинаковые уровни напряжения, что воспринимается последующими логическими каскадами как неопределенное состояние.

Таким образом, ускорение процесса формирования логических напряжений на разрядных шинах запоминающего устройства повышает быстродействие при смене элементов памяти в режиме считывания информации.

Формула изобретения Запоминающее устройство, содержащее элементы памяти, каждый из которых состоит из двух ключевых транзисторов, двух нагрузочных резисторов, первого и второго ограничительных диодов, катоды которых соединены с первыми выводами первого и второго нагрузочных резисторов соответственно, базами второго и первого ключевых транзисторов соответственно и коллекторами первого и второго ключевых транзисторов соответственно, первые эмиттеры которых объединены и являются выводом питания элемента памяти, анод первого ограничительного диода является входом выборки элемента памяти и соединен с анодом второго ограничительного диода и вторыми выводами первого и второго нагрузочных резисторов, вторые эмиттеры первых и вторых ключевых транзисторов всех элементов памяти подключены к первой и второй разрядным шинам устройства соответственно, блок компенсации разброса параметров, состоящий из двух ключевых транзисторов, двух нагрузочных резисторов, компенсирующего резистора, первого ограничительного диода, анод которого является входом выборки устройства и соединен с первым выводом первого нагрузочного резистора, второй вывод которого соединен с первым выводом компенсирующего резистора и первым выводом второго нагрузочного резистора, второй вывод которого соединен с катодом первого ограничительного диода и коллектором пер- вого ключевого транзистора, эмиттер которого подключен к первой разрядной шине устройства, а база соединена с вторым выводом компенсирующего резистора и базой второго ключевого транзистора, эмиттер которого подключен к второй разрядной шине устройства, отличающееся тем, что, с целью повышения быстродействия устройства, блок компенсации разброса параметров содержит третий нагрузочный резистор

и второй ограничительный диод, анод которого соединен с анодом первого ограничительного диода, а катод - с коллектором второго ключевого транзистора и первым выводом третьего нагрузочного резистора, второй вывод которого соединен с первым выводом компенсирующего резистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1990 |

|

SU1751814A1 |

| Запоминающее устройство | 1986 |

|

SU1361630A1 |

| Генератор тока для устройств выборкииНфОРМАции из НАКОпиТЕля | 1979 |

|

SU851490A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1569901A1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Элемент памяти | 1989 |

|

SU1679552A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1573472A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2018979C1 |

Изобретение относится к вычислительной технике, а точнее к запоминающим устройствам на биполярных транзисторах. S Целью изобретения является повышение быстродействия запоминающего устройства. Поставленная цель достигается тем, что устройство содержит третий нагрузочный резистор 17 и второй ограничительный диод 20. При смене выбранного элемента 1 памяти через резистор 17 протекает дополнительный ток, который снижает уровень базового напряжения транзисторов 13 и 14. В результате потенциал базы открытого транзистора вновь выбранного элемента памяти превысит базовый уровень транзисторов 13 и 14 раньше. Это ускоряет процесс формирования информационной разности потенциалов на разрядных шинах 10 и 11 запоминающего устройства. 2 ил. ч Ё VI сл 00 Фиг.1 11

Фиг 2.

| Валиев К.А., Орликовский А.А | |||

| Интегральные схемы памяти на биполярных транзисторных структурах | |||

| М.: Сов.радио, 1979, с | |||

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

| Запоминающее устройство | 1986 |

|

SU1361630A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-07-30—Публикация

1990-06-18—Подача