(Л

со

О1

Изобретение относится к вычисли- т ельной технике и может быть использовано в процессорах ЭВМ.

Цель изобретения упрощение с умматора„

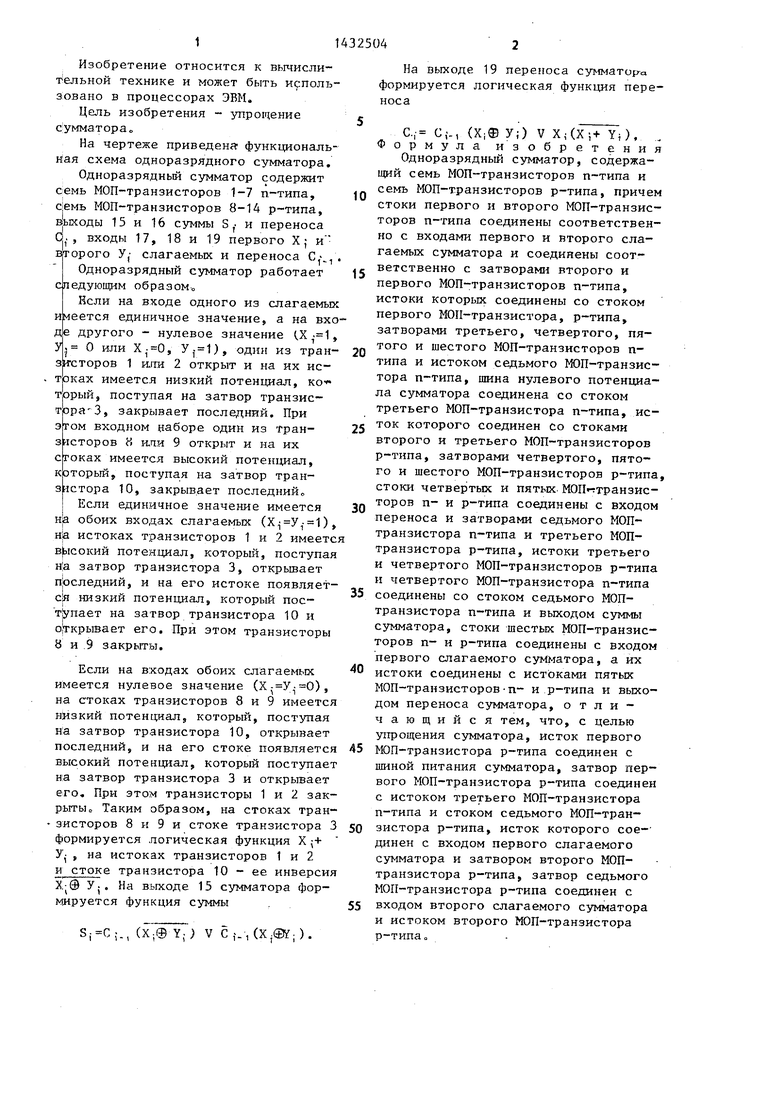

На чертеже приведена функциональная схема одноразрядного сумматора.

Одноразрядньм сумматор содержит семь МОП-транзисторов 1-7 п-типа, с|емь МОП-транзисторов 8-14 , выходы 15 и 16 суммы S,- и переноса О.-, входы 17, 18 и 19 первого X , и второго у, слагаемых и переноса С,- .

Одноразрядный сз мматор работает спедующим образом

Нсли на входе одного из слагаемых имеется единичное значение, а на входе другого - нулевое значение (,Х,1, У. О или , ), один из тран- зи-сторов 1 И.ПИ 2 открыт и на их истоках имеется низкий потенциал, ко- торый, поступая на затвор транзистора 3, закрывает последний. При этом входном наборе один из тран- Зггсторов Н И.ПИ 9 открыт и на их стоках имеется высокий потенциал, который, поступая на затвор транзистора 10, закрывает последний

I Если единичное значение имеется Ир обоих входах слагаемых (), нЬ истоках транзисторов 1 и 2 имеетс в|ысокий потен:и;иал, который, поступая Н:а затвор транзистора 3, открывает последний, и на его истоке появляет- с|я низкий потенциал, который пос топает на затвор транзистора 10 и о гкрывает его. При этом транзисторы 8 и 9 закрыты.

Если на входах обоих слагаемых имеется нулевое значение (), на стоках транзисторов 8 и 9 имеется низкий потенциал, который, поступая на затвор транзистора 10, открывает последний, и на его стоке появляется высокий потенциал, который поступает на затвор транзистора 3 и открьгоает его. При этом транзисторы 1 и 2 закрыты Таким образом, на стоках тран- зисторов 8 и 9 и стоке транзистора 3 формируется логическая функция X (+ У,- , на истоках транзисторов 1 и 2 к стоке транзистора 10 - ее инверсия Х;@ У;. На выходе 15 сумматора формируется функция суммы .

., (Х;® Y;) V Cf-,().

На выходе 19 переноса сумматора формируется логическая функция переноса

С.,- С;., (Х|ф У;) V Х(Х;+ Y; ) , . Формула изобретения

Одноразрядный сумматор, содержащий семь МОП-транзисторов и семь МОП-транзисторов р-типа, причем стоки первого и второго МОП-транзисторов п-типа соединены соответственно с входами первого и второго слагаемых сумматора и соединены соответственно с затворами второго и первого МОП-транзисторов п-типа, истоки которых соединены со стоком первого МОП-транзистора, р-типа, затворами третьего, четвертого, пятого и шестого МОП-транзисторов п- типа и истоком седьмого ЮП-транзис- тора п-типа, шина нулевого потенциала сумматора соединена со стоком третьего МОП-транзистора п-типа, исток которого соединен со стоками второго и третьего МОП-транзисторов р-типа, затворами четвертого, пятого и шестого МОП-транзисторов р-типа, стоки четвертых и пятьк МОП«транзис- торов п- и р-типа соединены с входом переноса и затворами седьмого МОП- транзистора п-типа и третьего МОП- транзистора р-типа, истоки третьего и четвертого МОП-транзисторов р-типа и четвертого МОП-транзистора п-типа соединены со стоком седьмого МОП- транзистора п-типа и выходом суммы сумматора, стоки шестых МОП-транзисторов п- и р-типа соединены с входом первого слагаемого сумматора, а их истоки соединены с истоками пятых МОП-транзисторов-п- и р-типа и выходом переноса сзжматора, отличающийся тем, что, с целью упрощения сумматора, исток первого МОП-транзистора р-типа соединен с шиной питания сумматора, затвор первого МОП-транзистора р-типа соединен с истоком третьего МОП-транзистора п-типа и стоком седьмого МОП-транзистора р-типа, исток которого сое- динен с входом первого слагаемого сумматора и затвором второго МОП- транзистора р-типа, затвор седьмого МОП-транзистора р-типа соединен с входом второго слагаемого сумматора и истоком второго МОП-транзистора р-типао

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор на КМОП-транзисторах | 1987 |

|

SU1439578A1 |

| Одноразрядный сумматор | 1987 |

|

SU1509874A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1357945A1 |

| Одноразрядный сумматор | 1986 |

|

SU1325465A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1441387A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1381490A1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР НА МОП ТРАНЗИСТОРАХ | 1996 |

|

RU2152641C1 |

| Комбинационный сумматор | 1988 |

|

SU1596321A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 1996 |

|

RU2164036C2 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения упрощение сумматора. Одноразрядный сумматор содержит семь МОП-транзисторов п-типа 1-7, семь МОП-транзисторов р-типа 8-14, выходы 15, 16 суммы S и переноса С(, входы 17-19 первого и второго слагаемого X,, У; и переноса С;.i. одноразрядный сумматор формирует логические функции суммы S , С; Х,- ® ,) V Ci(X,-@ Yi) и пере-, носа С , С ,-., (X f Ф У,-; V Xi(X;@y,. ) . 1 ил. с

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-10-23—Публикация

1986-12-18—Подача