Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ.

Цель изобретения - упрощение одноразрядного сумматора.

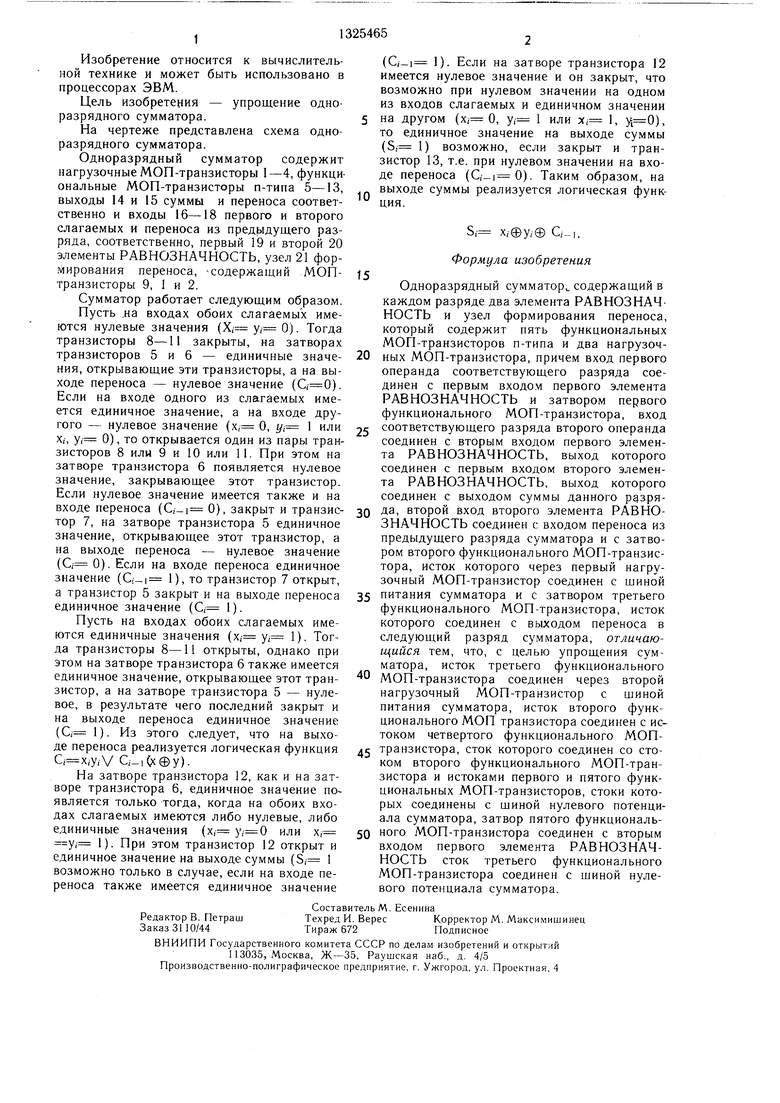

На чертеже представлена схема одноразрядного сумматора.

Одноразрядный сумматор содержит нагрузочные МОП-транзисторы 1-4, функциональные МОП-транзисторы п-типа 5-13, выходы 14 и 15 суммы и переноса соответственно и входы 16-18 первого и второго слагаемых и переноса из предыдущего разряда, соответственно, первый 19 и второй 20 элементы РАВНОЗНАЧНОСТЬ, узел 21 формирования переноса, содержащий .МОП- транзисторы 9, 1 и 2.

Сумматор работает следующим образом.

Пусть .на входах обоих слагаемых имеются нулевые значения (Xi у, 0). Тогда транзисторы 8-11 закрыты, на затворах транзисторов 5 и 6 - единичные значения, открывающие эти транзисторы, а на выходе переноса - нулевое значение (С,0). Если на входе одного из слагаемых имеется единичное значение, а на входе другого - нулевое значение (х, О, ;/, 1 или X,, у, 0), то открывается один из пары транзисторов 8 или 9 и 10 или 11. При этом на затворе транзистора 6 появляется нулевое значение, закрывающее этот транзистор. Если нулевое значение имеется также и на входе переноса (C,i 0), закрыт и транзистор 7, на затворе транзистора 5 единичное значение, открывающее этот транзистор, а на выходе переноса - нулевое значение (С, 0). Если на входе переноса единичное значение ( 1), то транзистор 7 открыт, а транзистор 5 закрыт и на выходе переноса единичное значение (С, 1).

Пусть на входах обоих слагаемых имеются единичные значения (х; у, 1). Тогда транзисторы 8-11 открыты, однако при этом на затворе транзистора 6 также имеется единичное значение, открывающее этот транзистор, а на затворе транзистора 5 - нулевое, в результате чего последний закрыт и на выходе переноса единичное значение (С, 1). Из этого следует, что на выходе переноса реализуется логическая функция

C,,-V C; iOi®y).

На затворе транзистора 12, как и на затворе транзистора 6, единичное значение появляется только тогда, когда на обоих входах слагаемых имеются либо нулевые, либо единичные значения (х, у, 0 или х, у, 1). При этом транзистор 12 открыт и единичное значение на выходе суммы (S, 1 возможно только в случае, если на входе переноса также имеется единичное значение

Составитель М. Есенина

Редактор В. ПетрашТехред И. ВересКорректор М. Максимишинец

Заказ 3110/44Тираж 672Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(С,1 1). Если на затворе транзистора 12 имеется нулевое значение и он закрыт, что возможно при нулевом значении на одном из входов слагаемых и единичном значении на другом (xi О, у,- 1 или х, 1, ), то единичное значение на выходе суммы (S; 1) возможно, если закрыт и транзистор 13, т.е. при нулевом значении на входе переноса (C,). Таким образом, на выходе суммы реализуется логическая функция.

S,- С,1. Формула изобретения

5

Одноразрядный сумматор,, содержащий в каждом разряде два элемента РАВНОЗНАЧНОСТЬ и узел формирования переноса, который содержит пять функциональных МОП-транзисторов п-типа и два нагрузоч0 ных МОП-транзистора, причем вход первого операнда соответствующего разряда соединен с первым входом первого элемента РАВНОЗНАЧНОСТЬ и затвором первого функционального МОП-транзистора, вход

5 соответствующего разряда второго операнда соединен с вторым входом первого элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с выходом суммы данного разря0 да, второй вход второго элемента РАВНОЗНАЧНОСТЬ соединен с входом переноса из предыдущего разряда сумматора и с затвором второго функционального МОП-транзистора, исток которого через первый нагрузочный МОП-транзистор соединен с щиной

5 питания сумматора и с затвором третьего функционального МОП-транзистора, исток которого соединен с выходом переноса в следующий разряд сумматора, отличающийся тем, что, с целью упрощения сумматора, исток третьего функционального

МОП-транзистора соединен через второй нагрузочный МОП-транзистор с шиной питания сумматора, исток второго функционального МОП транзистора соединен с истоком четвертого функционального МОПс транзистора, сток которого соединен со стоком второго функционального МОП-транзистора и истоками первого и пятого функциональных МОП-транзисторов, стоки которых соединены с шиной нулевого потенциала сумматора, затвор пятого функциональ0 ного МОП-транзистора соединен с вторым входом первого элемента РАВНОЗНАЧНОСТЬ сток третьего функционального МОП-транзистора соединен с шиной нулевого потенциала сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1357945A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1381490A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1441387A1 |

| Одноразрядный сумматор | 1987 |

|

SU1432505A1 |

| Одноразрядный сумматор | 1987 |

|

SU1509874A1 |

| Одноразрядный сумматор на КМОП-транзисторах | 1987 |

|

SU1439578A1 |

| Одноразрядный сумматор | 1986 |

|

SU1432504A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР НА МОП ТРАНЗИСТОРАХ | 1996 |

|

RU2152641C1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

| Комбинационный сумматор | 1988 |

|

SU1527630A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - упрошение устройства. Одноразрядный сумматор содержит нагрузочные транзисторы 1-4, функциональные МОП-тран- исторы п-типа 5-13, два элемента РАВНОЗНАЧНОСТЬ 19, 20, выполненные на МОП- транзисторах. Одноразрядный сумматор имеет только прямые входы слагаемых и переноса и требует для своей реализации только 9 функциональных и 4 нагрузочных МОП-транзисторов п-типа. С учетом того, что нагрузочный транзистор идентичен функциональному, предложенное техническое решение дает экономию оборудования на 27%. 1 ил. rsD сл 4 05 СП

| Мурога С | |||

| Системное проектирование сверхбольших интегральных схем.-М.: Мир, 1985, кн | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| с | |||

| Регулятор давления для автоматических тормозов с сжатым воздухом | 1921 |

|

SU195A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| СПОСОБ ПРОИЗВОДСТВА ФРУКТОВОГО СОУСА | 2013 |

|

RU2528596C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-03—Подача