i

(21)4274164/24-24

(22)01.07.87

(46) 23.09.89. Бкш. № 35

(71)Ленинградский электротехнический институт им. В.И.Ульянова (Ленина)

(72)В.И.Варшавский, Н.А.Голдин, А.Ю.Кондратьев и Б.С.Цирлин

(53)681.325.5(088.8)

(56) Авторское свидетельство СССР № 1100620, кл. G 06 F 7/50,1983. Авторское свидетельство СССР № 1439578. кл. G 06 F 7/50, 27.05.87.

(54)ОДНОРАЗРЯДНЫЙ СУММАТОР

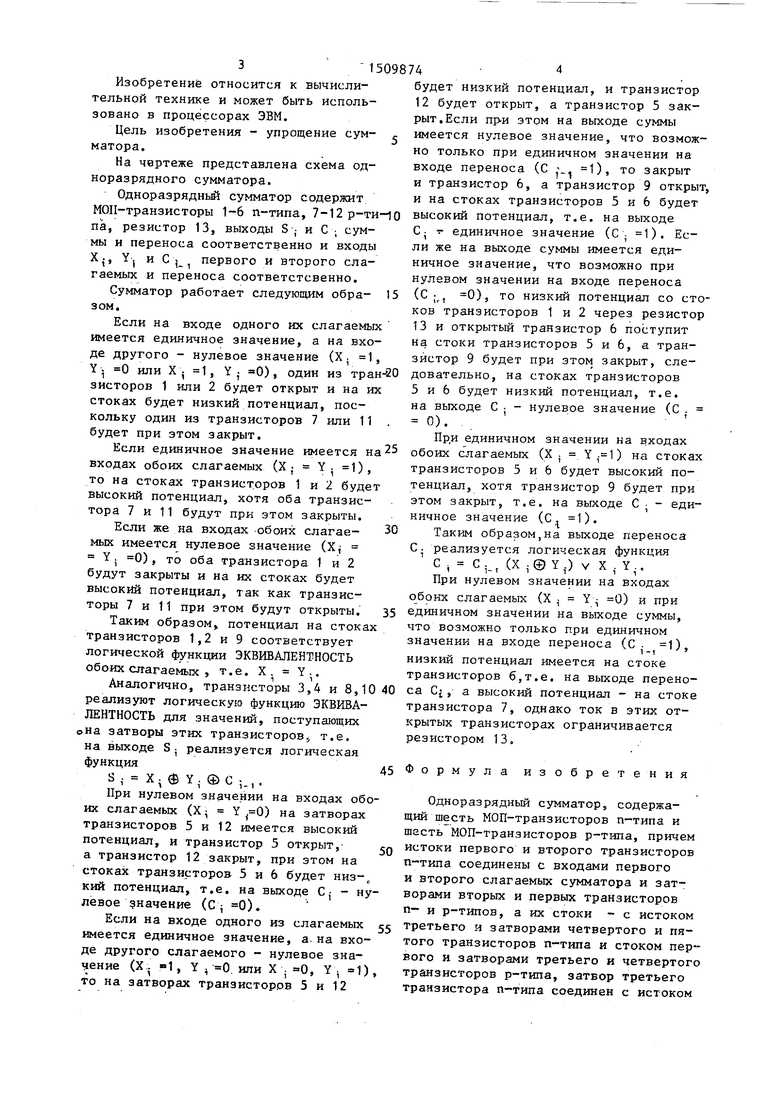

(57) Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения - упрощение сумматора. Одно- разрядньй сумматор содержит МОП-транзисторы 1-6 п-типа и 7-12 р-типа. Истоки транзисторов 1,5 и 2 соединены с входами первого и второго слагаемых и затворами транзисторов 2,11 и 1,7; стоки транзисторов 1,2,7 - с истоком транзистора 3 и затворами транзисторов 4,5,8,9; затворы транзисторов 3,10 и исток транзистора 4 - со входом переноса; стоки транзисторов 3,4,8 - с выходом суммы и затворами транзисторов 6,12; стоки 5,6,9 - с вькодом переноса; истоки транзисторов 10,11,12 - с шиной питания, а их стоки - с истоками транзисторов 8,7 и 9. В сумматор введен резистор 13, через который исток транзистора 6 соединен со стоком транзистора 7. 1 ил.

с

te

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор на КМОП-транзисторах | 1987 |

|

SU1439578A1 |

| Одноразрядный сумматор | 1986 |

|

SU1432504A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1357945A1 |

| Одноразрядный сумматор | 1986 |

|

SU1325465A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1381490A1 |

| Одноразрядный сумматор на МОП-транзисторах | 1986 |

|

SU1441387A1 |

| Комбинационный сумматор | 1988 |

|

SU1596321A1 |

| Комбинационный сумматор | 1988 |

|

SU1674108A1 |

| Одноразрядный сумматор | 1987 |

|

SU1432505A1 |

| Комбинационный сумматор | 1987 |

|

SU1543399A1 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения - упрощение сумматора. Одноразрядный сумматор содержит МОП- транзисторы 1-6 N-типа и 7-12 P - типа. Истоки транзисторов 1,5 и 2 соединены со входами первого и второго слагаемых и затворами транзисторов 2, 11 и 1, 7

стоки транзисторов 1, 2, 7 - с истоком транзистора 3 и затворами транзисторов 4, 5, 8, 9

затворы транзисторов 3, 10 и исток транзистора 4 - со входом переноса

стоки транзисторов 3, 4, 8 - с выходом суммы и затворами транзисторов 6, 12

стоки 5, 6, 9 - с выходом переноса

истоки транзисторов 10, 11, 12 - с шиной питания, а их стоки - с истоками транзисторов 8, 7 и 9. В сумматор введен резистор 13, через который исток транзистора 6 соединен со стоком транзистора 7. 1 ил.

;о

00

:

Изобретение относится к вычислиельной технике и может быть испольовано в процессорах ЭВМ.

Цель изобретения - упрощение сум- - атора.

На чертеже представлена схема одоразрядного сумматора.

Одноразрядный сумматор содержит МОП-транзисторы 1-6 п-типа, 7-12 р-ти-1о па, резистор 13, выходы S ; и С ; сумы и переноса соответственно и входы -, YJ и С j первого и второго слагаемых и переноса соответстсвенно.

Сумматор работает следующим обра- 15 зом.

Если на входе одного их слагаемых имеется единичное значение, а на входе другого - нулевое значение (Х 1, Y. 0 или Х 1, Y. 0), один из тран-йО зисторов 1 или 2 будет открыт и на их стоках будет низкий потенциал, поскольку один из транзисторов 7 или 11 будет при этом закрыт.

Если единичное значение имеется на входах обоих слагаемых (Х ; У- 1), то на стоках транзисторов 1 и 2 будет высокий потенциал, хотя оба транзистора 7 и 11 будут при этом закрыты.

Если же на входах обоих слагав- 30 мых имеется нулевое значение (Х - Y. 0), то оба транзистора 1 и 2 будут закрыты и на их стоках будет высокий потенциал, так как транзисторы 7 и 11 при этом будут открыты. 35

Таким образом потенциал на стоках транзисторов 1,2 и 9 соответствует логической функции ЭКВИВАЛЕНТНОСТЬ обоих слагаемых , т.е. X, Y..

Аналогично, транзисторы 3,4 и 8,1040 реализуют логическую функцию ЭКВИВАЛЕНТНОСТЬ для значений, поступающих На затворы этих транзисторов,, т.е. на выходе S, реализуется логическая функция45

S,. Х- ф Y; ®С ;.,.

При нулевом значении на входах обоих слагаемых (Х Y 0) на затворах транзисторов 5 и 12 имеется высокий потенциал, и транзистор 5 открыт, Q а транзистор 12 закрыт, при этом на стоках транзисторов 5 и 6 будет низ-„ кий потенциал, т.е. на выходе С,- - нулевое дначение (сi 0).

Если на входе одного из слагаемых 55 имеется единичное значение, а на входе другого слагаемого - нулевое значение (X. -1, У , 0. или X . 0, У, 1), то на затворах транзисторов 5 и 12

будет низкий потенциал, и транзистор

12будет открыт, а транзистор 5 закрыт. Если пр-и этом на выходе суммы имеется нулевое значение, что возможно только при единичном значении на входе переноса (С . 1), то закрыт

и транзистор 6, а транзистор 9 открыт и на стоках транзисторов 5 и 6 будет высокий потенциал, т.е. на выходе С; единичное значение (С; 1). Если же на выходе суммы имеется единичное значение, что возможно при нулевом значении на входе переноса (с ;, 0)j то низкий потенциал со стоков транзисторов 1 и 2 через резистор

13и открытый транзистор 6 поступит на стоки транзисторов 5 и 6, а транзистор 9 будет при этом закрыт, следовательно, на стоках транзисторов

5 и 6 будет низкий потенциал, т.е. на выходе С - - нулевое значение (С . 0). ,

При единичном значении на входах обоих слагаемых (X; У. 1) на стоках транзисторов 5 и 6 будет высокий потенциал, хотя транзистор 9 будет при этом закрыт, т.е. на выходе С ; - единичное значение (С, 1).

i

Таким образом,на выходе переноса С. реализуется логическая функция

С. С;., (X.©Y,.) V x,Y..

При нулевом значении на входах обоих слагаемых (X 0) и при единичном значении на выходе суммы, что возможно только при единичном значении на входе переноса (С - 1),

низкий потенциал имеется на стоке транзисторов б,т.е. на выходе переноса Ci, а высокий потенциал - на стоке транзистора 7, однако ток в этих открытых транзисторах ограничивается резистором 13.

Формула изобретения

Одноразрядный сумматор, содержащий шесть МОП-транзисторов п-типа и шесть МОП-транзисторов р-типа, причем истоки первого и второго транзисторов п-типа соединены с входами первого и второго слагаемых сумматора и затворами вторых и первых транзисторов п- и р-типов, а их стоки - с истоком третьего и затворами четвертого и пятого транзисторов п-типа и стоком первого и затворами третьего и четвертог транзисторов р-типа, затвор третьего транзистора п-типа соединен с истоком

515098746

четвертого транзистора п-типа, эатво-типов соединены.с выходом суммы сумма- ром пятого транзистора р-типа и вхо-тора, истоки- второго, пятого и шеото- дом переноса сумматора, а. стоки тре-го транзисторов р-типа согединены с тьих транзисторов р- и п-типов - со ,шиной питания сумматора, а их стоки - стоками четвертого транзистора п-ти- С истоками соответственно первого, па и выходом суммы сумматора, стоктретьего и четвертого транзисторов пятого транзистора п-типа соединен с iр-типа, отличающийся тем, входом одного слагаемого сумматора, ачто, с целью упрощения сумматора, он исток - с истоками четвертого транзис- Qсодержит резистор, через который ис- тора р-типа и шестого транзистораток шестого транзистора п-типа со- п-типа и выходом переноса сумматора,единен со стоком первого транзистора затворы шестых транзисторов п- и р-р-типа.

Авторы

Даты

1989-09-23—Публикация

1987-07-01—Подача